设计任务:

本章节将会在已经设计好的 DDR3 SDRAM 控制器的基础上,实现用户端的 写、读操作。

设计目的:

我们自己添加 FIFO 的 DDR3 SDRAM 控制器已经实现了,接着我们就可以通过该控制器对 DDR3 SDRAM 进行读写了。本节我们将会完成该控制器的写、读操作。

用户端写实现:

1、用户写控制器介绍用户端的写、读控制

主要功能需要按照 FIFO IP 核能够接受的逻辑时序编排对应的逻辑功能,因此该控制器的输出应该按照 FIFO IP 核的时序进行。 下面先对写控制器进行分析。FIFO IP 核预留的写端口主要包含两个 fifo 接 口,其中一个可以缓存数据,另外一个缓存命令。为了保证数据在写入 DDR3 SDRAM中时不出现数据量和突发长度不一致的情况,我们可以先将需要写入的数据存到数据 fifo 中,再对命令 fifo 发送写命令相关的信息,这样可以保证 FIFO IP 核接收到命令之后,有正确的突发长度的数据可以传输。

2、用户写控制器框架

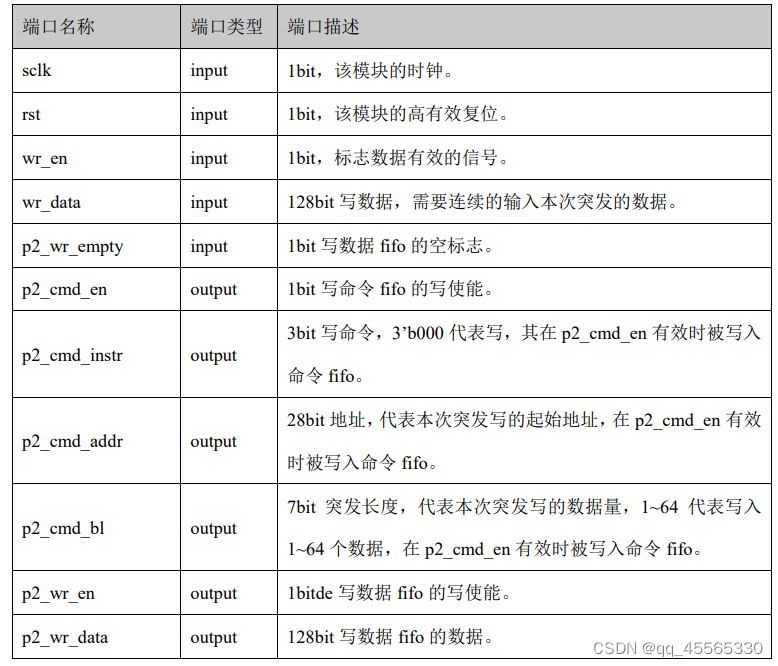

由上图可以看到,需要写入的数据 wr_data 由 wr_en标志有效,我们需要在该模块实现由输入的 wr_data 和 wr_en 产生 FIFO IP 核写端口所需要的信息,并 最终有 FIFO IP 核写数据端口的 fifo 空标志产生用户端写完成的信号。

3、该模块各个变量说明

下面对该模块的端口进行说明。

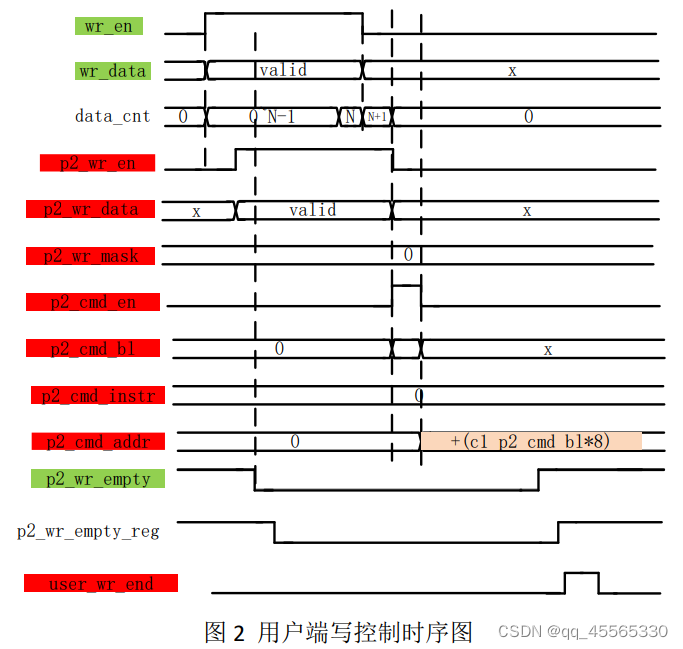

4、用户端写控制的时序图

由上图可以看到,我们根据输入进来的数据的数量确定突发的长度,当输入 的数据结束时,产生命令 fifo 的写使能等端口信息。当 FIFO IP 核在接收到命令 fifo 的命令后,会将数据 fifo 的数据取出写入的 DDR3 SDRAM 中,我们可以根据数据 fifo 的空标志确定是否完成该过程,当出现数据 fifo 的空标志上升沿,则认为所有突发的数据均以写入到 DDR3 SDRAM 中,此时我们可以产生一个 user_wr_end 信号告知外部模块本次突发写结束。 地址的计算:16 位的数据地址,每个地址递增 1 代表着写入 16 位数据,那 么 128 位

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

654

654

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?