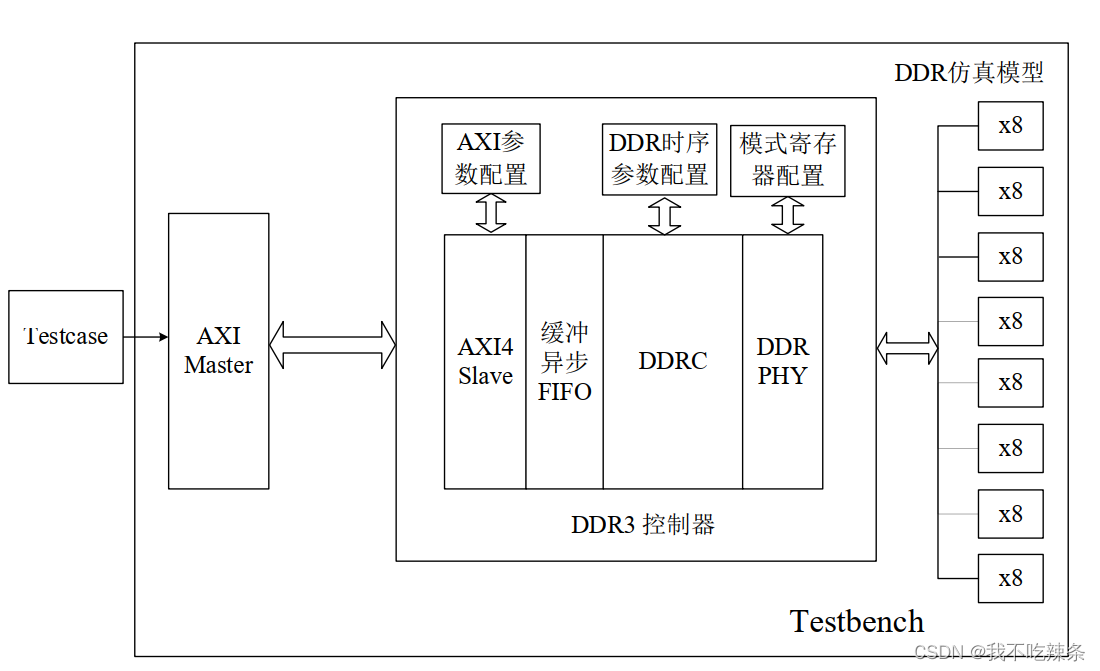

DDR controller 验证平台以及功能测试用例

验证点:

(1)DDR3协议验证

1、上电初始化和模式寄存器配置是否成功

2、刷新操作是否完成

3、进入、退出自刷新模式是否成功

为了降低内存在无读写操作时的功耗, 同时能够保存数据, 控制器发送自刷新命令使内存进入自刷新状态。 内存在进入自刷新模式之前处于空闲状态, 在内存时钟上升沿, cke 信号从高电平变为低电平,此时 cs_n、 ras_n、 cas_n保持低电平, we_n 信号保持高电平, 满足进入自刷新状态条件。在时钟上升沿 cke 从低电平变为高电平, cs_n、 ras_n、 cas_n 和 we_n 信号保持高电平, 信号的组合值满足内存退出自刷新状态条件。

4、进入退出断电模式是否成功

PD 模式相比自刷新能进一步减少功耗。 在 cke 保持低电平时,发送一个 NOP 命令就可以让内存进入 PD 模式。进入 PD 模式之前,内存处于空闲状态, 在内存时钟上升沿, cke 保持低电平, cs_n 保持高电平, 信号组合满足内存进入 PD 模式的条件。内存在 PD 状态中的时间超过刷新周期之后, SDRAM 中的数据就不会保持了。因此,为了保存数据, 控制器在自动刷新计数器超时的时候退出 PD 模式,完成刷新操作之后,如果没有预取的数据,继续进入 PD 模式。 观察波形图, 在内存时钟上升沿, cke 从高电平变为低电平,cs_n 保持高电平([cs_n, ras_n, cas_n, we_n]=4’b0111),内存进入 PD 模式, 等待一段时间, 在时钟上升沿, cke 从低电平变为高电平, cs_n 保持高电平, 内存退出 PD 模式并连续执行多个刷新操作, 执行完刷新操作之后控制器发出 PD 进入命令,命令执行流程满足设计要求。 因此控制器能够在 PD 模式执行刷新操作。 控制器发出 PD 模式退出指令,内存会从 PD 状态跳转到空闲状态。 观察波形图, 在内存时钟上升沿, cke 从低电平变为高电平, cs_n 保持高电平, 控制器发出的命令满足退出 PD 模式的条件。

5、读命令

6、写命令

(2)子模块功能验证

1、AXI接口的异步预取FIFO是否能够正确写入读出

2、AXI接口模块的写通道、读通道操作是否正确

3、读写仲裁模块能否公平轮询读写FIFO

4、bank队列的读入写出是否正确,命令状态码和命令重排序功能是否正常

5、协议转换模块读写操作是否正确,交叉指令功能是否实现

6、写数据缓冲功能是否正确,并正确发送出去

7、读缓冲模块对读数据能否正确的分配,并按照正确的顺序返回。

8、AXI总线上写入的数据和回读的数据是否相同

9、AXI总线上回读的数据是否按照读命令返回

(3)系统验证

1、连续地址读写操作

2、跨bank地址读写操作

3、随机地址读写操作

a、同一bank操作

1、ACT->READ

2、ACT->READ->READ

3、ACT(R1)->READ(R1)->PRE(R1)->ACT(R2)->READ(R2)

4、ACT->READ-WRITE

5、ACT(R1)->READ(R1)->PRE(R1)->ACT(R2)->WRITE(R2)

6、ACT->WRITE

7、ACT->WRITE->WRITE

8、ACT(R1)->WRITE(R1)->PRE(R1)->ACT(R2)->WRITE(R2)

9、ACT->WRITE->READ

10、ACT(R1)->WRITE(R1)->PRE(R1)->ACT(R2)->READ(R2)

b、跨bank操作

1、ACT(A)->READ(A)->ACT(B)->READ(B)

2、ACT(A)->READ(A)->ACT(B)->WRITE(B)

3、ACT(A)->WRITE(A)->ACT(B)->WRITE(B)

4、ACT(A)->WRITE(A)->ACT(B)->READ(B)

395

395

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?