一、VHDL的三个基本层次

首先来看一下一个简单的VHDL示例

library IEEE;

use IEEE.STD_LOGIC_1164.ALL; --使用IEEE库中的STD_LOGIC_1164中的所有

entity test_top is --实体的声明

Port (

a : IN STD_LOGIC; --定义a是一个输入的标准逻辑类型

b : IN STD_LOGIC;

s : IN STD_LOGIC;

y : OUT STD_LOGIC

); --实体的端口

end test_top;

architecture Behavioral of test_top is --结构体,实体内部要进行的操作

begin

y <= a WHEN s = '0' -- y=a当s=0的时候

ELSE

b WHEN s = '1';

end Behavioral;

上述代码包含了一个VHDL代码所需要的三个层次

分别是:

(1)库:包含器件的输入、输出端口,数据类型。

library IEEE;

use IEEE.STD_LOGIC_1164.ALL; --使用IEEE库中的STD_LOGIC_1164中的所有

(2)实体:在电路原理图上,相当于器件符号,用来描述引脚的

entity test_top is --实体的声明

Port (

a : IN STD_LOGIC; --定义a是一个输入的标准逻辑类型

b : IN STD_LOGIC;

s : IN STD_LOGIC;

y : OUT STD_LOGIC

); --实体的端口

end test_top;

(3)结构体:相当于器件的内部结构,器件的功能

architecture Behavioral of test_top is --结构体,实体内部要进行的操作

begin

y <= a WHEN s = '0' -- y=a当s=0的时候

ELSE

b WHEN s = '1';

end Behavioral;

二、元件例化

首先需要区分实体和元件:总结起来,实体是一个模块的接口描述,用于定义模块的输入和输出信号。元件则是实体的具体实现,包含了实现模块功能的逻辑描述。

VHDL中元件例化主要有两步,首先元件声明(architecture和begin之间),然后元件例化(在电路描述部分,即begin之后)

下面是一个使用VHDL的全加器的例子

(1)首先是半加器的代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL; --使用IEEE库中的STD_LOGIC_1164中的所有

entity haf_adder is --实体的声明

Port (

a : IN STD_LOGIC; --定义a是一个输入的标准逻辑类型

b : IN STD_LOGIC;

c : OUT STD_LOGIC;

s : OUT STD_LOGIC

); --实体的端口

end haf_adder;

architecture Behavioral of haf_adder is --结构体,实体内部要进行的操作

begin

s <= a XOR b;

c <= a AND b;

end Behavioral;

(2)然后是全加器代码

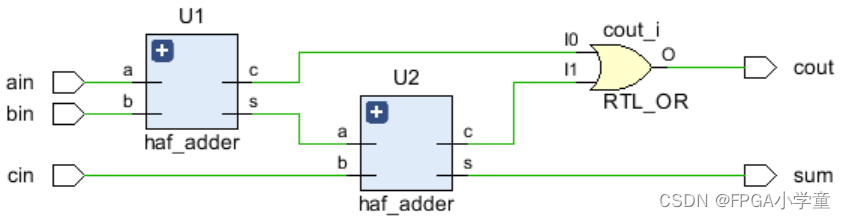

在全加器中例化了两个半加器

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity adder is

Port (

ain : IN STD_LOGIC; --定义a是一个输入的标准逻辑类型

bin : IN STD_LOGIC;

cin : IN STD_LOGIC;

cout: OUT STD_LOGIC;

sum : OUT STD_LOGIC

);

end adder;

architecture Behavioral of adder is

COMPONENT haf_adder --声明元件

Port (

a : IN STD_LOGIC;

b : IN STD_LOGIC;

c : OUT STD_LOGIC;

s : OUT STD_LOGIC

);

END COMPONENT;

SIGNAL c1,c2,s1 :STD_LOGIC; --定义信号线,进行器件的连接

begin

U1 : haf_adder PORT MAP(a=>ain,b=>bin,c=>c1,s=>s1 );

U2 : haf_adder PORT MAP(a=>s1,b=>cin,c=>c2,s=>sum );

--例化元件

cout <= c1 OR c2;

end Behavioral;

其中,

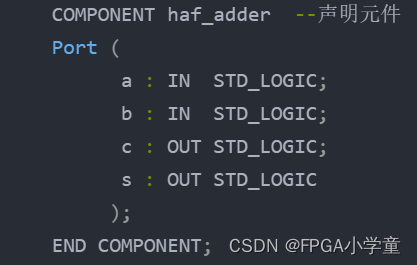

元件声明的方式为

Component 元件名称 is

Port(元件端口信息);

End component;

即代码中的

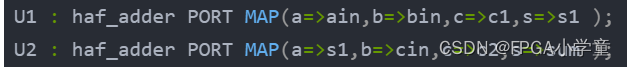

元件例化的方式为

例化名 :元件名称 port map 元件端口列表

注意:此处使用了端口信号名称关联方式进行例化元件,推荐使用这种方法,比较直观

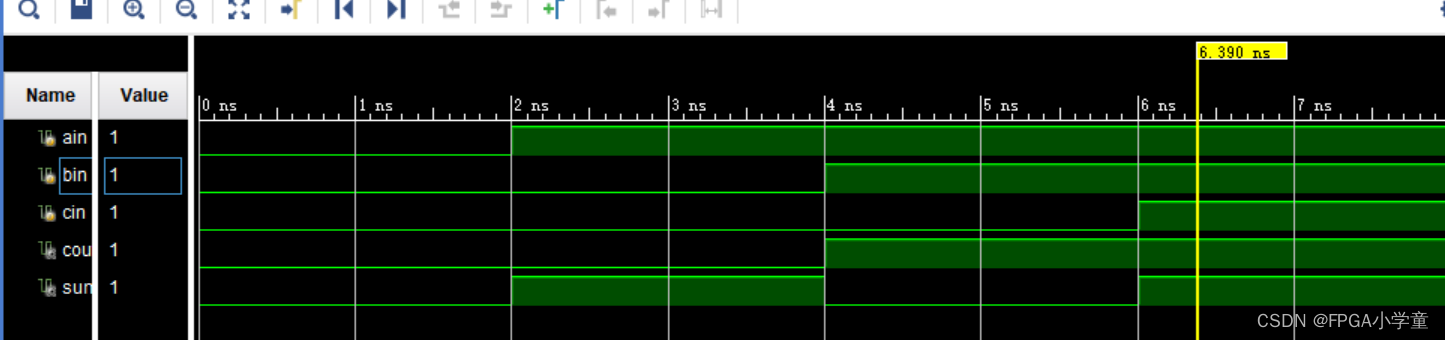

最终的程序RTL图、testbeach、仿真图如下

module adder_sim();

reg ain,bin,cin;

wire cout,sum;

initial begin

ain = 0;

bin = 0;

cin = 0;

#2

ain = 1;

bin = 0;

cin = 0;

#2

ain = 1;

bin = 1;

cin = 0;

#2

ain = 1;

bin = 1;

cin = 1;

#2

$stop;

end

adder adder(

.ain(ain),

.bin(bin),

.cin(cin),

.cout(cout),

.sum(sum)

);

endmodule

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?