前言

所用平台为I.MX6UL。

原理简述

LCD简介

Liquid Crystal Display,液晶显示器。液晶显示器的每个像素由以下几个部分构成:悬浮于两个透明电极(氧化铟锡)间的一列液晶分子层,两边外侧有两个偏振方向互相垂直的偏振过滤片。如果没有电极间的液晶,光通过其中一个偏振过滤片其偏振方向将和第二个偏振片完全垂直,因此被完全阻挡了。但是如果通过一个偏振过滤片的光线偏振方向被液晶旋转,那么它就可以通过另一个偏振过滤片。液晶对光线偏振方向的旋转可以通过静电场控制,从而实现对光的控制。

分辨率

LCD是由像素点组成的(可以理解为放大版的点阵屏),在同等尺寸下,分频率越高,图像越细腻

常见的1080P指的是19201080,也就是2073600个像素点,2K就是25601440个像素点,4K是3840*2160个像素点

显示器左上角是第一个像素点,右下角为左后一个像素点,分x,y轴。

像素格式

一个像素点相当于个RGB小灯,通过控制R、G、B三种颜色的亮度就可以显示颜色。

- RGB888格式:通常一个R、G、B三部分分别使用8bit的数据,一个像素点就是8bit*3=24bit(三个字节)

- ARGB8888格式:在RGB888的基础上增加了8bit的Alpha(透明)通道,总达到32bit,4个字节

- RGB565格式:每个像素用16比特位表示,占2个字节,RGB分量分别使用5位、6位、5位。

- RGB555格式:每个像素用16比特位表示,占2个字节,RGB分量都使用5位(最高位不用)。

- RGB24格式: 每个像素用8比特位表示,占1个字节,注意:在内存中RGB各分量的排列顺序为:BGR BGR BGR ···

- RGB32格式:每个像素用32比特位表示,占4个字节,R,G,B分量分别用8个bit表示,存储顺序为B,G,R,最后8个字保留。

- ARGB32格式:在RGB32的基础上增加了alpha通道,保留的8bit用来表示alpha通道。

RGBLCD接口

| 信号线 | 描述 |

|---|---|

| R[7:0] | 8根红色数据线 |

| G[7:0] | 8根绿色数据线 |

| B[7:0] | 8根蓝色数据线 |

| DE | 数据使能线(DE模式) |

| VSYNC | 垂直同步信号线 |

| HSYNC | 水平同步信号线(HV模式) |

| PCLK | 像素时钟信号线 |

LCD时间参数

图像的形成:从左至右、从上到下的顺序扫描每个像素点(“Z”形运动,并在像素画上对应的像素。

一帧图像是一行一行组成的。

下图为分辨率为1020*600LCD一帧扫描图

- HSYNC是水平同步信号(行同步信号):当产生此信号表示开始新的一行。

- VSYNC是垂直同步信号(帧同步信号):当产生此信号表示开始显示新的一帧图像。

- HBP 水平同步信号前肩 :表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数

- HFP 水平同步信号后肩 :表示一行的有效数据结束到下一个水平同步信号開始之间的VCLK的个数

- VBP 垂直同步信号前肩 :表示在一帧图像开始时,垂直同步信号以后的无效的行数

- VFP 垂直同步信号后肩 :表示在一帧图像结束后,垂直同步信号曾经的无效的行数

这六个时间参数具体就要去查看LCD数据手册。

屏幕时序

行时序:

补充参数:

- HSPW: 是HSYNC信号宽度,也就是HSYNC信号持续时间。HSYNC信号不是一个脉冲,而是需要持续一段时间才是有效的,单位为 CLK

- HOZVAL:显示一行数据所需的时间

行列时序

补充参数:

- VSPW:是 VSYNC 信号宽度,也就是 VSYNC 信号持续时间,单位为 1 行的时间。

- LINE:显示一帧有效数据所需的时间

- 一行的通信过程:LCD控制器IC先发送一个HSYNC高电平脉冲信号,脉冲告诉驱动器下面的信息是一行信息。然后开始这一行信息,这一行信息包括3部分:HBPD+有效行信息+HFPD。其中前肩和后肩都属于时序信息(和LCD屏幕具体有关),有效行信息就是横向分辨率。所以你可以认为一行总共包含4部分:HSPW+HBP+HOZVAL(有效行信息)+HFPD。

- 一帧图像其实就是一列,一列图像由多个行组成,每行都是上面的时序。

- 一帧图像的通信过程:整个帧图像信号分为4部分:VSYNC+VBPD+LINE(帧有效信号)+VFPD。VSVNC是帧同步信号宽度,用来告诉驱动器一帧图像要开始了;VBPD和VFPD分别是垂直同步信号前后肩。

- 整帧所需时间为:T = (VSPW+VBP+LINE+VFP) * (HSPW + HBP + HOZVAL + HFP)

同时这也能解释黑边产生原因,无效行和无效个数一同组成了黑边。

像素时钟

像素时钟就是 RGB LCD 的时钟信号,显示一帧图像所需时钟数为上文提到的T

显存

显存=单个像素的大小*分辨率

通常RGB LCD内部不带内存,需要从其他地方分出一段内存作为显存用。

驱动分析

eLCDIF接口:

用于连接RGB LCD接口的屏幕,特性如下:

- 支持 RGB LCD 的 DE 模式。

- 支持 VSYNC 模式以实现高速数据传输。

- 支持 ITU-R BT.656 格式的 4:2:2 的 YCbCr 数字视频,并且将其转换为模拟 TV 信号。

- 支持 8/16/18/24/32 位 LCD。

支持以下三种接口:

- MPU 接口

用于与LCD屏幕直接传输数据和命令,用于6080/8080接口的LCD屏幕 - VSYNC 接口

VSYNC 接口时序和 MPU 接口时序基本一样,只是多了 VSYNC 信号来作为帧同步 - DOTCLK 接口

DOTCLK 接口就是用来连接 RGB LCD 接口屏幕的, 它包括 VSYNC、 HSYNC、 DOTCLK和 ENABLE(可选的)这四个信号,这样的接口通常被称为 RGB 接口,其时序和上文提到的行类时序很类似。

重要寄存器

配置寄存器LCDIF_CTRL

重要位:

| 位 | 描述 |

|---|---|

| SFTRST(bit31) | 软复位控制位,为1则复位 |

| CLKGATE(bit30) | 正常运行下为0,为1则不会进入到LCDIF |

| BYPASS_COUNT(bit19) | 在DOTCLK模式下必须为1 |

| VSYNC_MODE(bit18) | 为1在VSYNC接口模式 |

| DOTCLK_MODE(bit17) | 为1在DOTCLK接口模式 |

| INPUT_DATA_SWIZZLE(bit15:14) | 输入数据字节交换设置,为0,不交换字节(小端模式);为1交换所有字节;为2半字交换;为3在每个半字内进行字节交换 |

| CSC_DATA_SWIZZLE(bit13:12) | CSC数据字节交换设置,交换方式同上 |

| LCD_DATABUS_WIDTH(bit11:10) | LCD 数据总线宽度,为0总线宽度为16bit;为1总线宽度为8bit;为2总线宽度为18bit;为宽度为24bit |

| WORD_LENGTH(bit9:8) | 输入的数据格式(像素数据宽度),为0每个像素16bit;为1每个像素8bit;为2每个像素18bit;为3每个像素24bit |

| MASTER(bit5) | 为1工作在主模式 |

| DATA_FORMAT_16_BIT(bit3) | 当此位为 1 并且 WORD_LENGTH 为 0 的时候像素格式为 ARGB555,当此位为 0 并且 WORD_LENGTH 为 0 的时候像素格式为 RGB565 |

| DATA_FORMAT_18_BIT(bit2) | 当 WORD_LENGTH 为 2 的时候此位才有效,此位为 0 的话低 18 位有效,像素格为 RGB666,高 14 位数据无效。当此位为 1 的话高 18 位有效,低14为数据无效 |

| DATA_FORMAT_24_BIT(bit1) | 当 WORD_LENGTH 为 3 的时候此位才有效,为0表示全部的 24 位数据都有效.为1数据有效位只有 18 位,每个颜色通道的高 2 位数据会被丢弃掉 |

| RUN(bit0) | 接口运行控制位,为1使能,开始传输数据 |

控制寄存器 LCDIF_CTRL1

重要位:

- BYTE_PACKING_FORMAT(bit19:16),用来决定在 32 位的数据中哪些字节的数据有效,默认值为 0XF,也就是所有的字节有效,当为 0 的话表示所有的字节都无效。

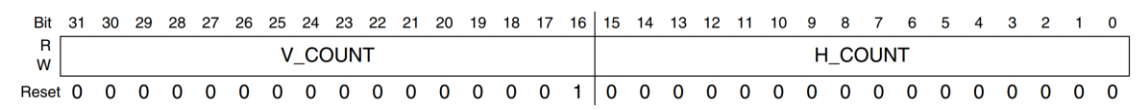

寄存器LCDIF_TRANSFER_COUNT

- 高16位:V_COUNT,LCD 的垂直分辨率

- 低16位:H_COUNT,是 LCD 的水平分辨率

寄存器 LCDIF_VDCTRL0

VSYNC 和 DOTCLK 模式 控制寄存器0

重要位:

| 位 | 描述 |

|---|---|

| VSYNC_OEB(bit29) | VSYNC 信号方向控制位,为0输出,为1输入 |

| ENABLE_PRESENT(bit28) | EBABLE 数据线使能位(DE数据线),为1使能,为0关闭 |

| VSYNC_POL(bit27) | VSYNC 数据线极性设置位,为 0 的话 VSYNC 低电平有效,为1高电平有效 |

| HSYNC_POL(bit26) | HSYNC 数据线极性设置位,为 0 的话 HSYNC 低电平有效,为1高电平有效 |

| DOTCLK_POL(bit25) | DOTCLK 数据线(像素时钟线 CLK) 极性设置位,为0的话下降沿锁存数据,上升沿捕获数据,为1相反 |

| ENABLE_POL(bit24) | EANBLE 数据线极性设置位,为 0 的话低电平有效,为1高电平有效 |

| VSYNC_PERIOD_UNIT(bit21) | VSYNC 信号周期单位,为 0 的话 VSYNC 周期单位为像素时钟。为1的话 VSYNC 周期单位是水平行,如果使用 DOTCLK 模式话就要设置为 1 |

| VSYNC_PULSE_WIDTH_UNIT(bit20) | VSYNC信号脉冲度单位,设置同上 |

| VSYNC_PULSE_WIDTH(bit17:0) | VSPW 参数设置位 |

寄存器 LCDIF_VDCTRL1

VSYNC 和 DOTCLK 模式 控制寄存器1

设置VSYNC总周期:VSYNC 和 DOTCLK 模式 控制寄存器0

寄存器 LCDIF_VDCTRL2

分为高 16 位和低 16 位两部

- 高16bit,HSYNC_PULSE_WIDTH,用来设置 HSYNC 信号宽度,也就是 HSPW

- 低16bit,HSYNC_PERIOD,设置 HSYNC 总周期,就是:屏幕宽度+HSPW+HBP+HFP

寄存器LCDIF_VDCTRL3

重要位:

- HORIZONTAL_WAIT_CNT(bit27:16):此位用于 DOTCLK 模式,用于设置 HSYNC 信号产生到有效数据产生之间的时间,也就是 HSPW+HBP

- VERTICAL_WAIR_CNT(bit15:0):此位用于 DOTCLK 模式,用于设置 VSYNC 信号产生到有效数据产生之间的时间,也就是 VSPW+VBP

寄存器 LCDIF_VDCTRL4

重要位:

- SYNC_SIGNALS_ON(bit18):同步信号使能位,设置为 1 使能 VSYNC、 HSYNC、DOTCLK 信号

- DOTCLK_H_VALID_DATA_CNT(bit15:0): 设置 LCD 的宽度,也就是水平像素数量

寄存器 LCDIF_CUR_BUF 和 LCDIF_NEXT_BUF

LCD显存,分别存放当前帧和下一帧缓冲区,保存在同一地址

8041

8041

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?