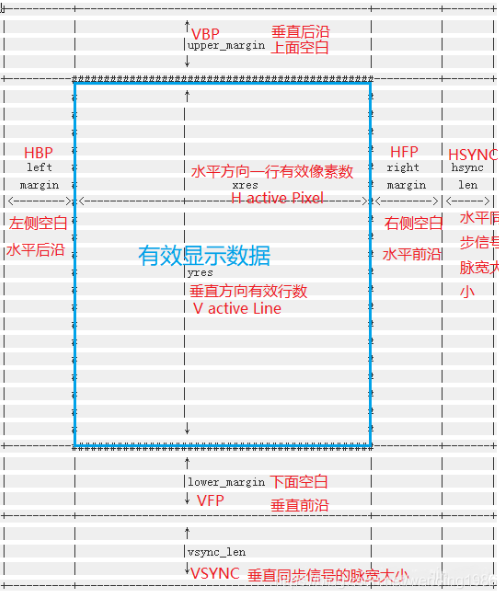

"porch" 沿,(大房子屋檐下的)走廊游廊

"margin" 边缘,(版心外的)空白

"HAdr" Horizontal Address 水平地址(空间),实际值对应的就是xres,水平有效像素数

"VAdr" Vertical Address 垂直地址(空间),实际值对应yres,垂直有效行数

"(VAdr + HAdr)" 有效显示数据从主控传输到显示模组上的时期

"blanking" 消隐

"Hblank" 行消隐 实际就是HFP+Hsync+HBP的时间,因为此期间并未有效显示,看做消隐状态

"Vblank" 场消隐 实际就是VFP+Vsync+VBP的时间,因为此期间并未有效显示,看做消隐状态

"HPW" Hsync Pulse Width 水平同步脉冲宽度 = HSYNC = HWH(Hsync Width)

"VPW" Vsync Pulse Width 垂直同步脉冲宽度 = VSYNC = VWH(Vsync Width)

"HS Blanking" Hsync Blanking 水平同步消隐 = HS Pulse Width + HS Back Porch

"Vs Blanking" Vsync Blanking 垂直同步消隐= Vs Pulse Width + VS Back Porch

"One Horizontal Line"= Hs Blanking (thb) + Horizontal Display Area (thd) + HS Front Porch (thfp)

"th = (thb+thd+thfp)" 一行有多少个像素时钟(Pixel)周期

"One Vertical Frame "= Vs Blanking (tvb) + Vertical Dsiplay Area (tvd) + Vs Front Porch (tvfp)

"tv = (tvb+tvd+tvfp)" 一帧有多少个行(Line)周期

"bpp" bit per pixel 每个像素的位数,主控端设置bpp实际是<根据面板每像素位数>来设置<framebuffer的颜色深度>,也即每像素数据需

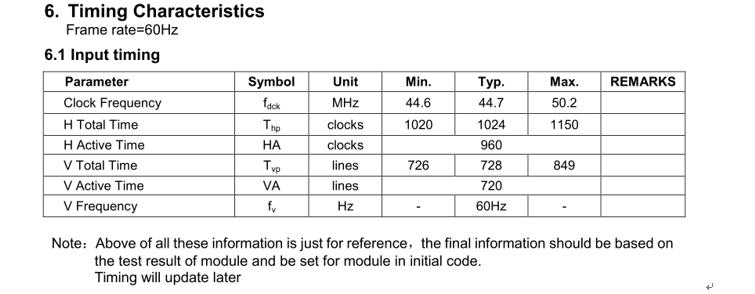

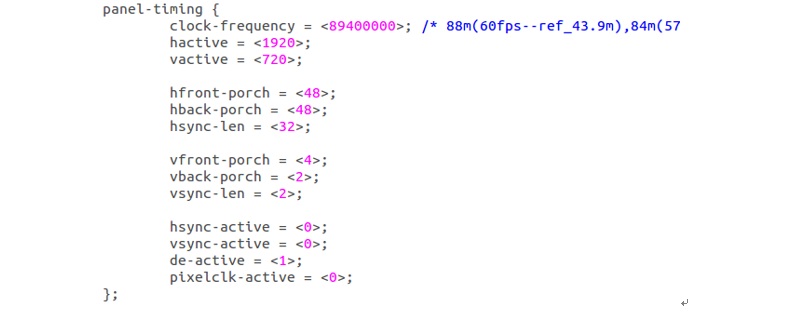

屏幕1

屏幕spec:

由于屏幕的奇偶屏,所以表中的clk都需要乘2,才是真正的屏幕clk,H的时间也得乘2

于spec中没有给出前后肩参数,在设备树中配置前后肩的总和需跟H Total Time V Total Time加起来一致。即

htotal = hactive+hfront-proch+hback-proch+hsync-len=1024*2

vtotal =vactive+vfront-porch+vblack-porch+vsync-len = 728

pclk = htotal * vtotal * fps ;8

pclk = 44.7M * 2 = 89.4M

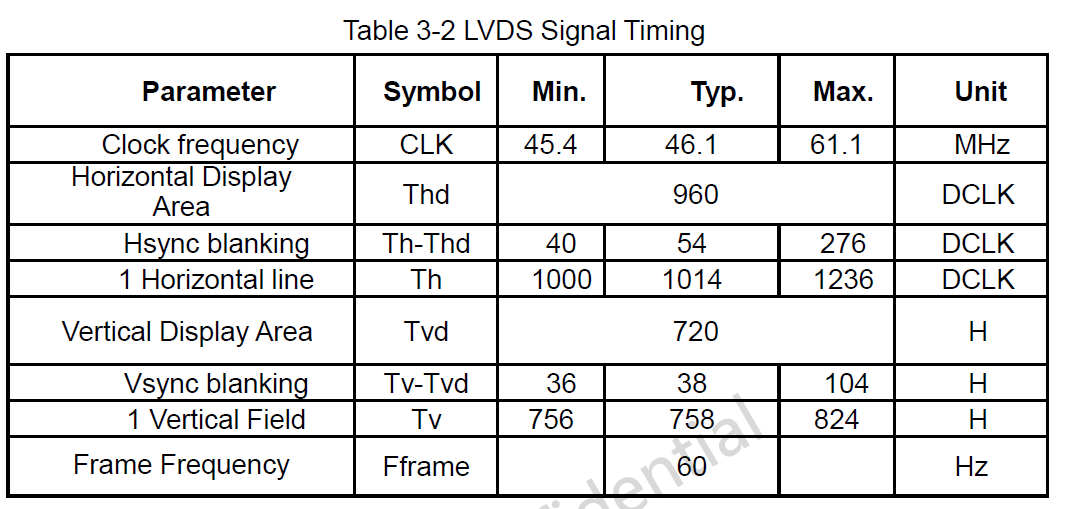

2.屏幕2:

由图中可知

hactive = 1920

htotal = hactive + hbp + hfp + hsyn-len = 2028

hblanking = hbp + hfp + hsyn-len = 108 这里取hbp = 50 hfp = 50 hsyn-len = 8

vacive = 720

vtotal = vactive + vbp + vfp + vsync-len = 758

vbp+vfp+vsync-len = 38 这里取vbp = 17 vfp = 17 vsync-len = 8

pclk = 2024 * 758 * 60 = 92051520

3110

3110

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?