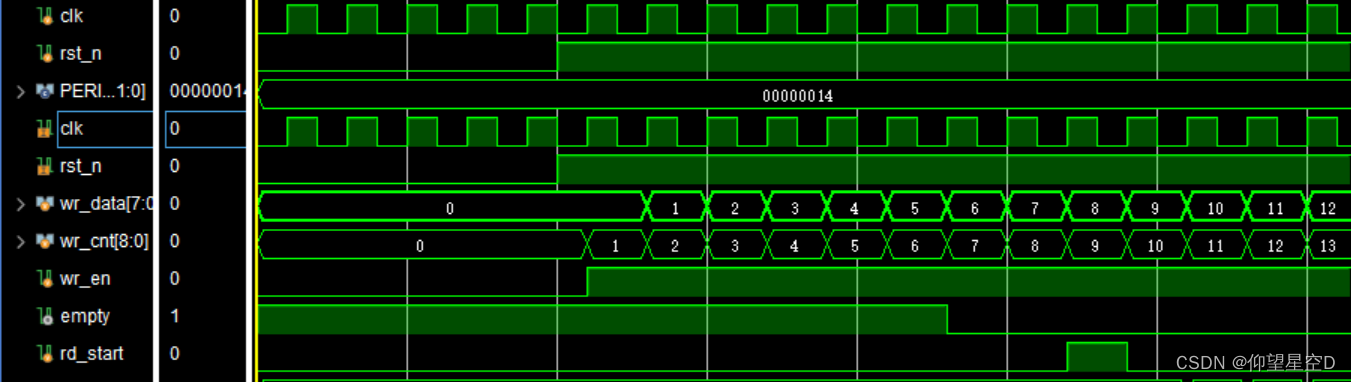

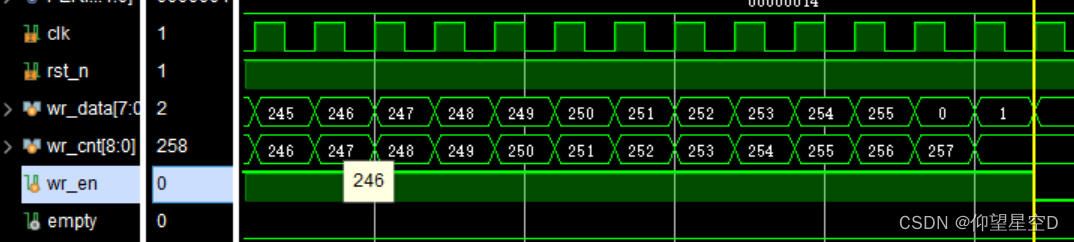

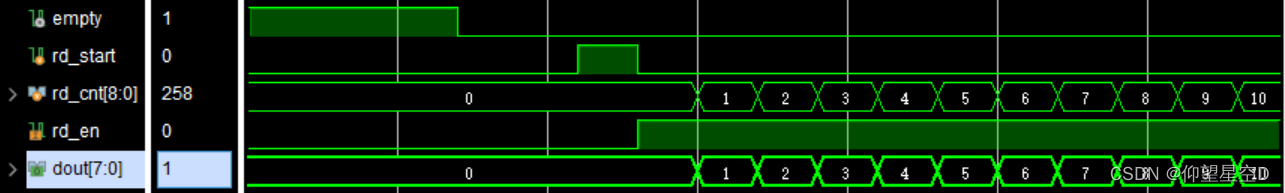

FIFO写入依次递增的数据并读出(先入先出)

ctrl_fifo

module crtl_fifo(

input wire clk,

input wire rst_n

);

reg wr_en,rd_en,rd_start;

wire full,empty;

reg [8:0]wr_cnt,rd_cnt;

reg [7:0]wr_data;

wire [7:0] dout;

reg [1:0]empty_dly;

fifo_generator_1 inst_fifo

(

.wr_clk (clk),

.rd_clk(clk),

.din( wr_data ),

. wr_en (wr_en),

. rd_en ( rd_en),

.dout(dout),

.full(full),

.empty(empty)

);

//写使能

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

wr_en <= 1'b0;

end

else if (wr_cnt== 'd0) begin

wr_en <= 1'b1;

end

else if (wr_cnt== 'd258) begin

wr_en <= 1'b0;

end

end

//wr_cnt控制wr_en的宽度

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

wr_cnt <= 1'b0;

end

else if (wr_cnt!='d258) begin

wr_cnt <= wr_cnt+1;

end

end

//wr_data写入的数据

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

wr_data <= 1'b0;

end

else if (wr_en==1) begin

wr_data <= wr_data +1;

end

end

//empty_dly寻找empty的下降沿,xilinx的移位寄存器不能有复位

always @(posedge clk)

begin

empty_dly<={empty_dly[0],empty};

end

//rd_start,读标志位

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

rd_start <= 1'b0;

end

else if (empty_dly==2'b10) begin

rd_start <= 'b1;

end

else rd_start <= 1'b0;

end

//rd_en读使能

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

rd_en <= 1'b0;

end

else if (rd_start== 'b1) begin

rd_en <= 1'b1;

end

else if (rd_cnt=='d257)

rd_en <= 1'b0;

end

//rd_cnt控制rd_en的宽度

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

rd_cnt <= 1'b0;

end

else if (rd_en==1) begin

rd_cnt <= rd_cnt+1;

end

end

endmodule

Standard 模式:读出的数据比读使能慢一个周期

First-Word Fall-Through 模式:读使能为1就读出数据。

该篇文章详细描述了一个使用Verilog编写的FIFO(First-In-First-Out)控制器,包括写入计数、数据传输、读使能控制以及两种工作模式:标准模式和First-WordFall-Through模式。它展示了如何利用时钟边缘触发控制信号以实现数据的顺序进出。

该篇文章详细描述了一个使用Verilog编写的FIFO(First-In-First-Out)控制器,包括写入计数、数据传输、读使能控制以及两种工作模式:标准模式和First-WordFall-Through模式。它展示了如何利用时钟边缘触发控制信号以实现数据的顺序进出。

957

957

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?