imx6ull主频设置

前言

对于imx6ull系列芯片而言,默认工作频率为396MHZ,但标准工作频率为528MHZ,甚至可以达到696MHZ,本章主要介绍如何将工作频率设置到528MHZ。

一、系统时钟来源

打开开发板原理图:

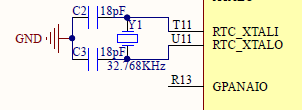

--第一张图为32.768KHz的晶振,为imx6ull的RTC时钟源;

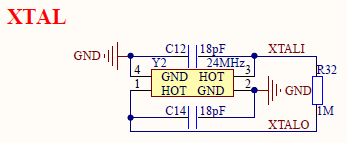

--第二张图为24MHz的晶振,其作为imx6ull内核以及其他外设的时钟源。

二、7路PLL时钟源

1. 介绍

针对不同外设,时钟源也不尽相同。imx6ull共7组PLL,该7组PLL来源于24MHz的晶振。

其中,部分PLL还会延申4路PFD,也是用于外设,此部分后边用到时再讨论。

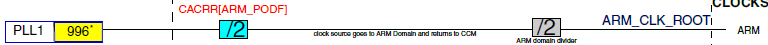

而PLL时钟源经过多路选择器以及分频器实现提供相应外设的工作频率,如下图:

2. 主频设置

★主频,即对ARM PLL进行设置:

①图2为设置主频的原理图,由图可知,若PLL1为996MHz,则经过2分频,得到的主频频率为498MHz,而我们所需的主频为528MHz,故需将PLL1设置为528 * 2 = 1056MHz,设置位于CCM_ANALOG_PLL_ARM寄存器的[DIV_SELECT];

②DIV_SELECT有计算公式:PLL output = Fref * DIV_SEL / 2 ,所以DIV_SEL结果为88;

- - PLL output为pll1时钟频率1056MHz,Fref为时钟源晶振24MHz。

③图1为PLL1产生源,此需通过多路选择器选择PLL1 Clk,才能将时钟信号传给图2所示路径,多路选择器开关位于CCSR寄存器中,此时选择时钟源需为pll1_main_clk。

需要注意的是,当我们对pll1_main_clk进行设定时,我们需保证arm的正常运行,即内核的正常工作,故需先将其切换为step_clk,等待设置完成后,再将其切换为pll1_main_clk。

图1 – PLL1时钟选择(章节18的18.5.1.5.1中)

图2 – ARM PLL

3. 代码编写

void imx6ull_init(void)

{

/* 对pll1_main_clk编辑之前,先将主频时钟源切换至step_clk */

if(CCM->CCSR & (1 << 2) == 0)

{

CCM->CCSR &= ~(1 << 2);

CCM->CCSR |= (1 << 2);

}

CCM_ANALOG->PLL_ARM &= ~(0x7F << 0) /* DIV_SELECT相关位清零 */

CCM_ANALOG->PLL_ARM |= ((1 << 13) | (88 & 0x7F)); /* 1左移13位为了使能时钟 , 88 = DIV_SEL */

CCM->CCSR &= ~(1 << 2); /* 重新切换至pll1_main_clk */

CCM->CACRR |= (1 << 0); /* 2分频 */

}

总结

①主频为ARM的工作频率,事关整个内核的运行。故在对其进行主频设定的时候,需将主频时钟切换为24MHz晶振(step_clk)确认内核正常工作,当设置完成后,再重新切回(pll1_main_clk)。

②PLL:Phase Locked Loop -> 锁相环,一般的晶振由于工艺和成本,很难做出较高的频率,所以通过PLL可实现输出稳定高频的时钟信号。

③PFD:鉴频鉴相器。比较两个输入信号的频率和相位即可得到与相位差有关的输出。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?