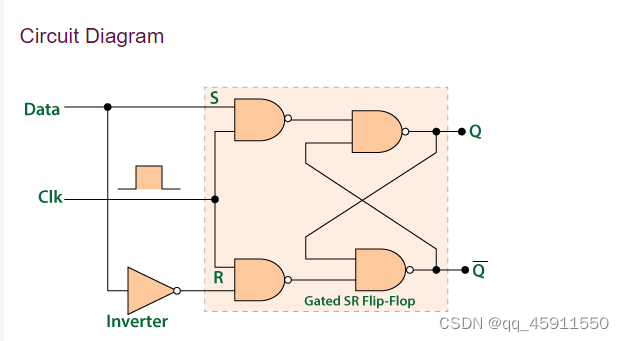

1. D flip-flop

1.1 structure

1.1.1 just use nand gate

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dffst is

Port ( d,clk : in STD_LOGIC;

q,qb : inout STD_LOGIC);

end dffst;

architecture dffstar of dffst is

component nand21

port(a,b: in STD_LOGIC;

y:out STD_LOGIC);

end component;

signal d1,s1,r1:STD_LOGIC;

begin

n0: nand21 port map(d,clk,s1);

n1: nand21 port map(d,d,d1);

n2: nand21 port map(d1,clk,r1);

n3: nand21 port map(s1,qb,q);

n4: nand21 port map(r1,q,qb);

end dffstar;

--— nand gate

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity nand21 is

Port ( a,b : in STD_LOGIC;

y : out STD_LOGIC);

end nand21;

architecture Behavioral of nand21 is

begin

y <= a nand b;

end Behavioral;

1.1.2 use not_gate and nand gate

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity dff_st is

Port ( d,clk : in STD_LOGIC;

q,qb : inout STD_LOGIC);

end dff_st;

architecture dffstar of dff_st is

component nand21

port(

a,b: in STD_LOGIC;

y:out STD_LOGIC);

end component;

component not_gate

port(

a: in STD_LOGIC;

y: out STD_LOGIC

);

end component;

signal d1,s1,r1:STD_LOGIC;

begin

n0: nand21 port map(d,clk,s1);

n1: not_gate port map(d,d1);

n2: nand21 port map(d1,clk,r1);

n3: nand21 port map(s1,qb,q);

n4: nand21 port map(r1,q,qb);

end dffstar;

-- nand gate

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity nand21 is

Port ( a,b : in STD_LOGIC;

y : out STD_LOGIC);

end nand21;

architecture Behavioral of nand21 is

begin

y <= a nand b;

end Behavioral;

-- not_gate

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity not_gate is

port(

a: in STD_LOGIC;

y: out STD_LOGIC

);

end not_gate;

architecture Behavioral of not_gate is

begin

y <= not a;

end Behavioral;

1.1.3 use not_gate and_2 gate

-- File: D_and_not.vhd

library ieee;

use ieee.std_logic_1164.all;

entity D_and_not is

port(

D : in std_logic;

CLK : in std_logic;

Q : inout std_logic;

Q_bar : inout std_logic

);

end D_and_not;

architecture structural of D_and_not is

component not_gate

port(

A : in std_logic;

Y : out std_logic

);

end component;

component and_2

port(

A : in std_logic;

B : in std_logic;

Y : out std_logic

);

end component;

signal not_D, d_and_clk, d_and_clk_not, d_and_clk_not_and, not_d_and_clk, not_d_and_clk_not, not_d_and_clk_not_and : std_logic;

begin

U1: not_gate port map(A => D, Y => not_D);

U2: and_2 port map(A => D, B => CLK, Y => d_and_clk);

U3: not_gate port map(A => d_and_clk, Y => d_and_clk_not);

U4: and_2 port map(A => d_and_clk_not, B => Q_bar, Y => d_and_clk_not_and);

U5: not_gate port map(A => d_and_clk_not_and, Y => Q);

U6: and_2 port map(A => not_D, B => CLK, Y => not_d_and_clk);

U7: not_gate port map(A => not_d_and_clk, Y => not_d_and_clk_not);

U8: and_2 port map(A => not_d_and_clk_not, B => Q, Y => not_d_and_clk_not_and);

U9: not_gate port map(A => not_d_and_clk_not_and, Y => Q_bar);

end structural;

-- File: and_2.vhd

library ieee;

use ieee.std_logic_1164.all;

entity and_2 is

port(

A : in std_logic;

B : in std_logic;

Y : out std_logic

);

end and_2;

architecture behavior of and_2 is

begin

Y <= A and B;

end behavior;

-- File: not_gate.vhd

library ieee;

use ieee.std_logic_1164.all;

entity not_gate is

port(

A : in std_logic;

Y : out std_logic

);

end not_gate;

architecture behavior of not_gate is

begin

Y <= not A;

end behavior;

1.1.4 simulation result of quartus and modelsim

2. JK flip-flop

2.1 structure

using D flip-flop as a component to build JK flip-flop, D flip flop could be behavior coding style.

718

718

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?