电流测试

我们可以通过电流来判断芯片的工作状态时,首先先了解下芯片的电流是如何产生的。

静态电流

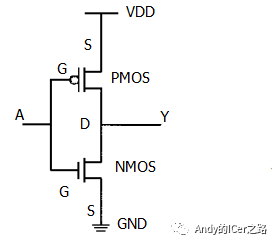

理论上,CMOS结构的芯片静态时几乎不耗电

- CMOS基本结构:Pmos + Nmos 串联

- 当逻辑电平稳定时:

➜ 要么Pmos导通,Nmos断开

➜ 要么Nmos导通,Pmos断开

➜ 整体不会形成直流通路 ➜ 所以静态电流接近0

如下,利用经典的反相器来解释这一原理:

| 输入 | 动作 | 输出 | 结论 |

|---|---|---|---|

| 高电平 | PMOS关,NMOS开,**VDD (断了) ➜ **GND (通过NMOS) | 低电平 | 只有NMOS开,但没有VDD到GND直接导通 ➜ 所以没有直流电流 |

| 低电平 | PMOS开,NMOS关,**VDD *(通过PMOS) ➜ **GND (断了) | 高电平 | 只有PMOS开,但还是没有VDD到GND直接通路 ➜ 静态电流近乎0 |

结论:

-

逻辑电平稳定时(比如芯片没动静的时候)

-

➜ 要么PMOS通,NMOS断

-

➜ 要么NMOS通,PMOS断

-

➜ 电流不会从VDD直接流到GND ➜ 所以理论上****静态功耗几乎为0

然而,实际上由于工艺问题,芯片上总会有微小的漏电,特别是先进工艺如7nm以下的芯片制成,这个漏电会更加严重,漏电产生的原因如下:

(1)亚阈值电流(Subthreshold Leakage)

- NMOS/PMOS在**理论"关断"*时,实际上还是有*微小导通 ➜ 因为MOS管的阈值并不是硬开硬关

(2)二极管反向漏电

- MOS管的漏极/源极和衬底之间,会形成PN结,PN结反向偏置时,也会有少量漏电流

(3)栅氧化层漏电

- 现代工艺栅氧层超薄(特别是7nm、5nm以下),电场一高 ➜ 电子会穿隧 ➜ 也有漏电流

动态电流

然而,上述是指芯片在静态的情况下的漏电流。当芯片在工作的时候,芯片内部的电流会增大,这主要是由于芯片内部的寄生电容开始放电导致的。

在芯片中,每个mos管和连线都会物理上带有电容,这是无法避免的。这些电容主要来自MOSFET 栅极和漏/源极之间 , 天然就有电容结构,还有金属连线之间的电容,金属层和层之间(M1对M2、M3…)也像电容板,而芯片工作时的电平反转,其实就是给这些寄生电容充电/放电。

信号翻转时(比如0 ➜ 1),电容要充电**(芯片内部线长有电容),翻转瞬间 ➜ PMOS和NMOS都短时间同时导通,这时候就会产生瞬时电流,从VDD ➜ GND这就是动态功耗

动态功耗的公式:

P=CV²f

其中P代表动态功耗,C代表电容,V代表电压,f代表工作频率。

电容代表芯片的电容负载,反映芯片的大小和复杂度,电压代表芯片电压,即电源电压,频率代表芯片的工作频率,即芯片每秒处理的指令数。

从公式可以看出,如果电容和电压增大,动态功耗也会增大:如果频率增大,动态功耗也会增大。因此,减小芯片的电容、电压和频率是减小动态功耗的关键

芯片测试中是如何测试静态和动态电流的?

各类电流测试

| 测试项 | 作用 | 测试时机 | 从CMOS原理解释 |

|---|---|---|---|

| IDDQ | 静态电流测试 (Quiescent IDD) | 芯片静态时 | 检查有没有短路、漏电。CMOS静态时电流应接近0 |

| IDD | 工作电流测试 | 芯片运行时 | 逻辑翻转时,电容充放电 ➜ 电流上升 |

| IDDT | 动态电流测试 (Transient IDD) | 芯片特定激励时 | 电流波动,检测信号是否在切换 |

| Leakage | 漏电测试 | 电源脚或IO脚 | MOSFET栅氧穿透、电源脚短路、芯片损坏时 ➜ 漏电流升高 |

IDDQ —— 静态电流测试(最经典的失效检测法)

作用:

- 检查芯片内部有没有短路、泄漏路径

- 传统CMOS逻辑静态时,IDDQ应为几微安或几十微安

- 如果测到mA级别 ➜ 说明有短路、漏电

从CMOS原理看:

- CMOS的静态电流 ≈ 漏电流(次级路径)

- 如果有某个短路缺陷,比如:

- Nmos和Pmos 都导通 ➜ 电源直接拉通 ➜ 电流暴涨

ATE设置:

| 参数 | 说明 | 典型设定 |

|---|---|---|

| VDD Supply | 供电电压 | 0.8V ~ 1.2V(核心) |

| Force Pattern | 特定静态逻辑Pattern | 全0或全1,或Scan链特殊值 |

| Measure Range | uA ~ mA级别 | |

| Limit | 设定上限 | 如 IDDQ < 100uA |

IDD —— 正常工作时的电源电流

作用:

- 测试芯片在正常运作时,总功耗是否在预期范围

- IDD变化 ➜ 反映芯片内部逻辑是否在运行

从CMOS原理看:

- 芯片运行时 ➜ 信号翻转 ➜ 电容充放电

- 功耗P = C × V² × f ➜ 电流跟频率直接相关

- 频率升高 ➜ 电流增加

- 负载电容大 ➜ 电流也大

常用于:

- 功耗敏感芯片(手机SoC、IoT)

- 检查芯片有没有「锁死」、「时钟丢失」之类的失效

- 比如:芯片跑起来 ➜ IDD从10mA变成30mA ➜ 说明逻辑活动正常

- 如果ID不变 ➜ 可能芯片没跑动

ATE设置:

| 参数 | 说明 | 典型设定 |

|---|---|---|

| VDD Supply | 供电电压 | 0.8V ~ 1.2V |

| Run Pattern | 向芯片加载Scan Shift/逻辑Pattern | 动态Pattern,如Scan shift 1000 cycles |

| Measure Range | mA ~ 几百mA | |

| Limit | 设定动态功耗上下限 | 如 10mA < IDD < 30mA |

IDDT —— 动态电流检测(专门检测「信号活动」)

作用:

- 通过观察电流波动,检测芯片内部信号是否有切换

- 可以间接检测时钟、数据链是否活跃

从CMOS原理看:

- 动态电流 ➜ CMOS电容充放电导致

- 如果某个时钟链死了 ➜ 该部分电流下降 ➜ IDDT变低

常用于:

-

Scan链检测:看Scan Shift时,IDDT是否如预期波动

-

时钟链检测:时钟失效 ➜ IDDT波动消失

IDD 和IDDT 一般区别不大。

Leakage —— 漏电流检测(最基础电流检测)

作用:

- 检查芯片IO脚、电源脚有没有异常漏电

- 比如:芯片Pad与地/电源短路,或者ESD损坏

从CMOS原理看:

- MOS管有亚阈值电流、隧穿电流

- ESD损伤时 ➜ 短路路径形成 ➜ 漏电升高

ATE设置:

| 参数 | 说明 | 典型设定 |

|---|---|---|

| Force Voltage | 施加的电压 | 0.8V ~ 1.2V(核心电压),或2.5V、3.3V(IO电压) |

| Measure Range | 测量电流范围 | nA ~ uA级别 |

| Limit (Pass/Fail) | 电流门限判断 | 比如 Leakage < 1uA 为Pass |

良品芯片:Leakage通常在几十nA~几百nA

坏品芯片:Leakage达到uA甚至mA ➜ 短路或损伤

tips:关于芯片制程和IDDQ以及IDD的关系

芯片制程越先进,动态 电流越小,静态 电流越大

| 功耗类型 | 制程变小(例如从28 nm→7 nm→5 nm) | 原因 |

|---|---|---|

| 动态功耗 | 减小 | 电容 C 更小,工作电压 V 也更低 → Pdynamic=C·V²·f↓ |

| 静态功耗 | 增大 | 栅氧层超薄、阈值电压降 → 漏电流(亚阈值、隧穿)飙升 |

1968

1968

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?