目录

11、OpenShort测试

(1)为什么要做OpenShort测试

“开路/短路测试”(opens/shorts test),也被称为连续性测试或接触测试。这种测试的目的是验证在设备测试期间,所有的信号引脚(signal pins)都能与待测设备(DUT,Device Under Test)建立电气接触,并且没有信号引脚之间发生短路,也没有信号引脚与电源或地线短路。

-

开路/短路测试的目的:

- 确保所有信号引脚在测试时都能建立电气接触。

- 确保没有信号引脚之间发生短路。

- 确保没有信号引脚与电源或地线短路。

-

设备成本与测试时间的关系:

设备成本与测试每个设备所需的时间直接相关,减少每个设备的平均测试时间是降低成本的有效方法。 -

快速识别不良设备:

开路/短路测试能够迅速判断设备是否存在短路引脚、缺失的键合线(bond wires)、由静电损伤的引脚、制造缺陷等问题。 -

测试系统相关问题的诊断:

如果测试结果异常,开路/短路测试还可以帮助诊断测试系统本身的问题,如晶圆测试探针卡(wafer test probe card)或设备测试插座(device test socket)是否正确接触。

(2)OpenShort测试的方法

有一种特定的开路/短路测试方法,称为“串行/静态开路/短路测试”(Serial/Static opens and shorts test)。

-

测试条件:

- 开路/短路测试的条件通常不会在器件规格书或数据手册中明确定义,但大多数标准器件类型都有适用的标准值。

-

测试步骤:

- 首先,将所有设备引脚(包括电源和地引脚)接地。

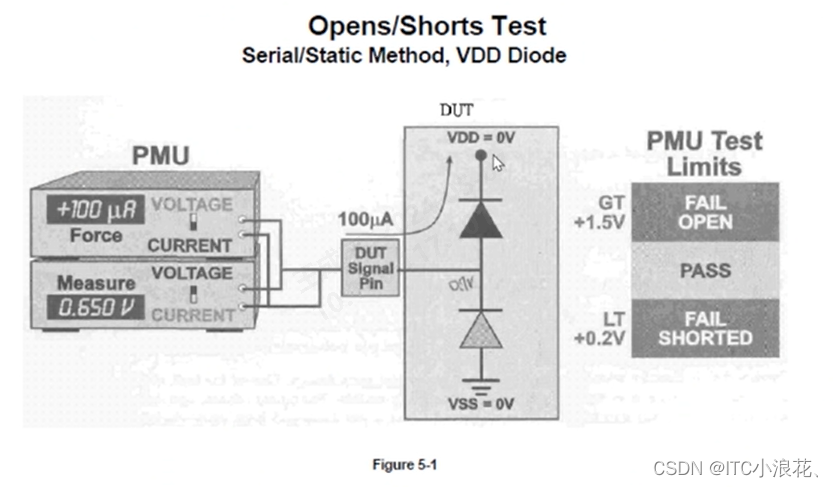

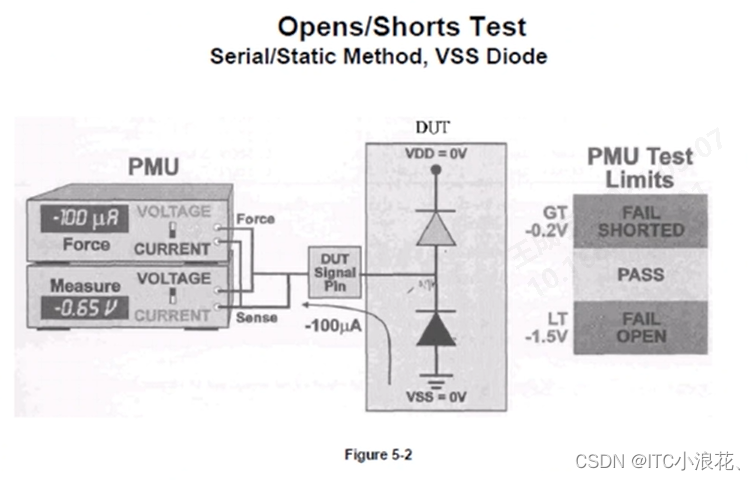

- 然后,将电源管理单元(PMU)连接到单个设备引脚,并施加电流,以正向偏置其中一个保护二极管。(见图5-1和图5-2)

- 负电流会使二极管正向偏置到地(ground),而正电流会使二极管正向偏置到VDD(电源电压)。

- 施加的电流应在100μA到500μA之间,这个范围对于大多数情况是足够的。

图5-1

- 接地所有引脚(包括VDD引脚)。

- 设置电压钳制为3.0伏特。

- 使用电源管理单元(PMU),一次对一个引脚施加+100微安培(μA)的电流。

- 测量产生的电压。

- 如果测量到的电压大于+1.5伏特,则测试失败(开路)。

- 如果测量到的电压小于+0.2伏特,则测试失败(短路)。

图5-2

- 接地所有引脚(包括VDD引脚)。

- 设置电压钳制为-3.0伏特。

- 使用电源管理单元(PMU),一次对一个引脚施加-100微安培(μA)的电流。

- 测量产生的电压。

- 如果测量到的电压大于-0.2伏特,则测试失败(短路)。

- 如果测量到的电压小于-1.5伏特,则测试失败(开路)。

测试结果:

数据记录格式:

- Pin:被测试的引脚编号。

- Force/rng:施加的电流范围。

- Meas/rng:测量的电压范围。

- Min:电压测量的最小值限制。

- Max:电压测量的最大值限制。

- Result:测试结果。

测试结果示例:

- Pin1:施加-0.100mA到2mA的电流,测量范围是-641mV到8V,最小电压限制是-1.500V,最大电压限制是-200mV,测试结果是PASS(通过)。

- Pin2:测试结果FAIL(失败),表明可能发生了开路。(触发钳制电压)

- Pin3:施加0.100mA到2mA的电流,测试结果是PASS(通过)。

- Pin4:测试结果FAIL(失败),表示可能发生了短路。

故障排除步骤:

- 开始故障排除前,启用数据记录器并观察测量结果。

- 测量结果将有三种可能性:

- 显示工作二极管的测量电压,大约为0.65V。

- 结果将表明短路状况,大约为0V。

- 结果将表明开路状况,这将受到钳制电压的限制。如果没有设置钳制电压,测量结果将是测试硬件范围所允许的最高电压。不钳制电压可能会进一步损坏待测设备(DUT)。

-

电压测量:

- 一旦二极管正向偏置,就可以感应到保护结构上的电压降(通常是0.65伏特)。

- 感应到的电压可能会因不同的技术和设计而变化,但对于大多数基于硅的器件来说,0.65V是一个合适的值。

-

电压钳制:

- 由于PMU将被编程以强制电流,因此必须设置一个电压钳制器来限制在测试开路引脚时产生的电压。

- 开路/短路测试的典型钳制值为3V。

- 当测试开路引脚时,测量结果将是钳制电压(3V)。

-

串行/静态测试的优势:

- 这种测试方法产生的是直流(DC)测量值。

- 当发生故障时,可以从数据记录的结果中检查确切的测量电压。

- 电压值可以清楚地表明故障是由短路条件还是开路条件引起的。

-

串行/静态测试的劣势:

- 需要在每个引脚上进行单独的直流测量,这会增加测试所需的时间。

12、Kelvin Test

开尔文测试(Kelvin Test)是一种用于检测电路中电阻或电导的精确测量方法,也叫四端点测量技术、四端测试法。它特别适用于测量低值电阻,如电机绕组、电缆、接地电阻、开关接触点以及其他类型的低电阻连接。开尔文测试通过消除测量引线带来的误差,提供了一种更为精确的测量方式。

(1)万用表如何测量电阻

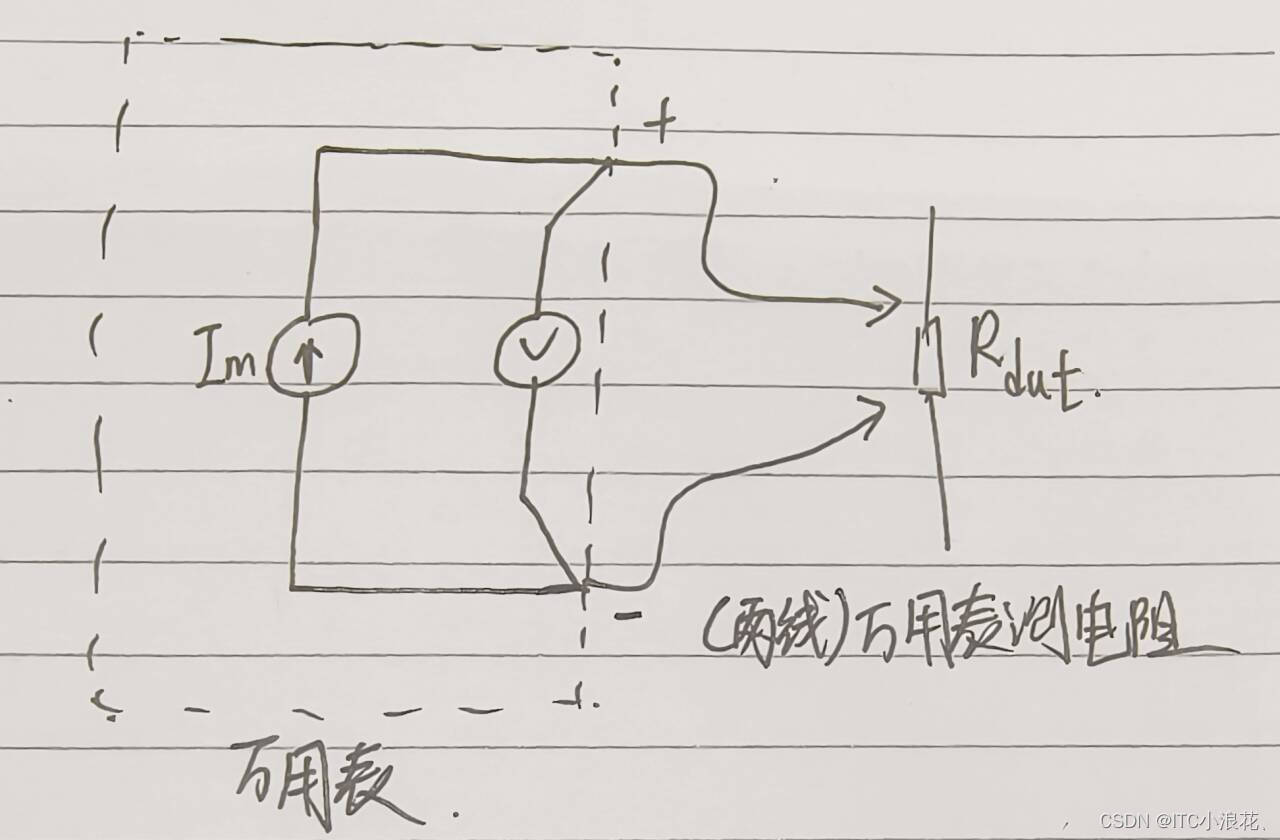

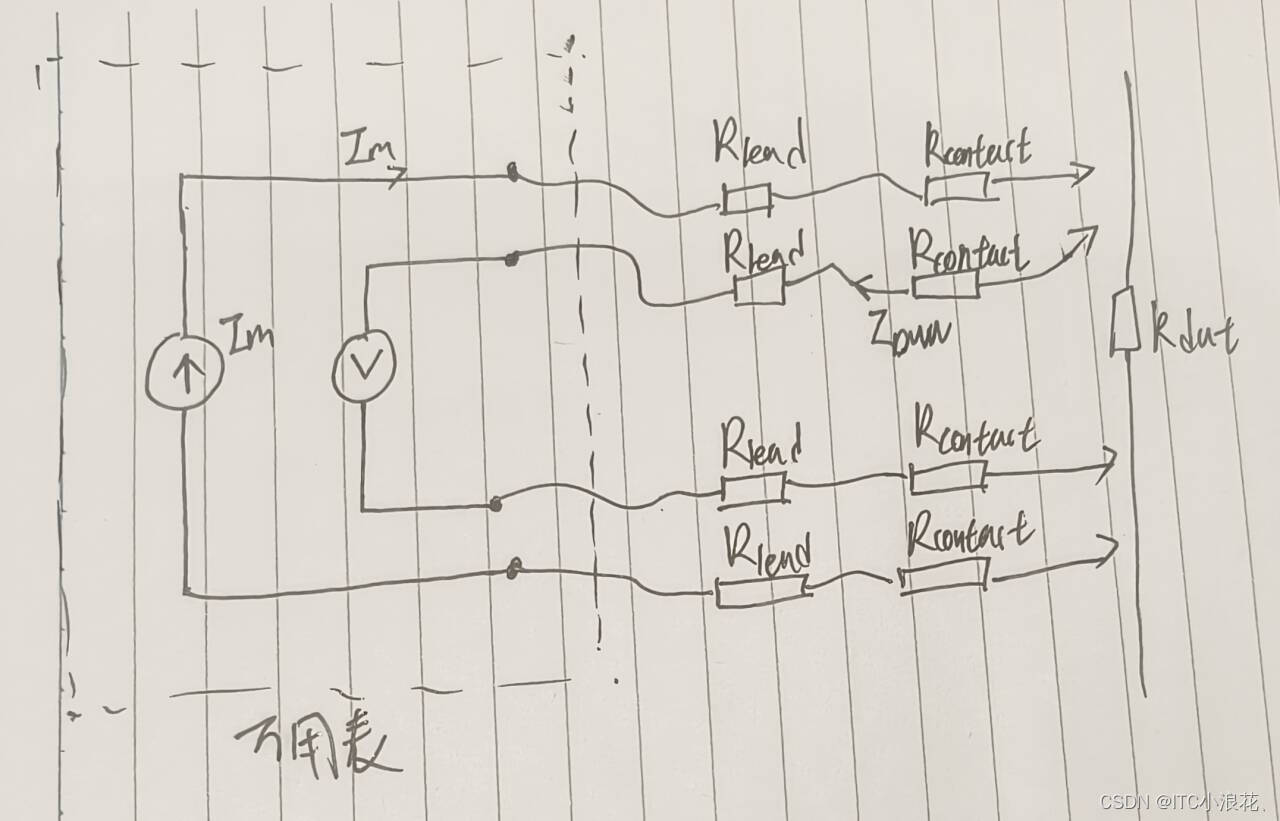

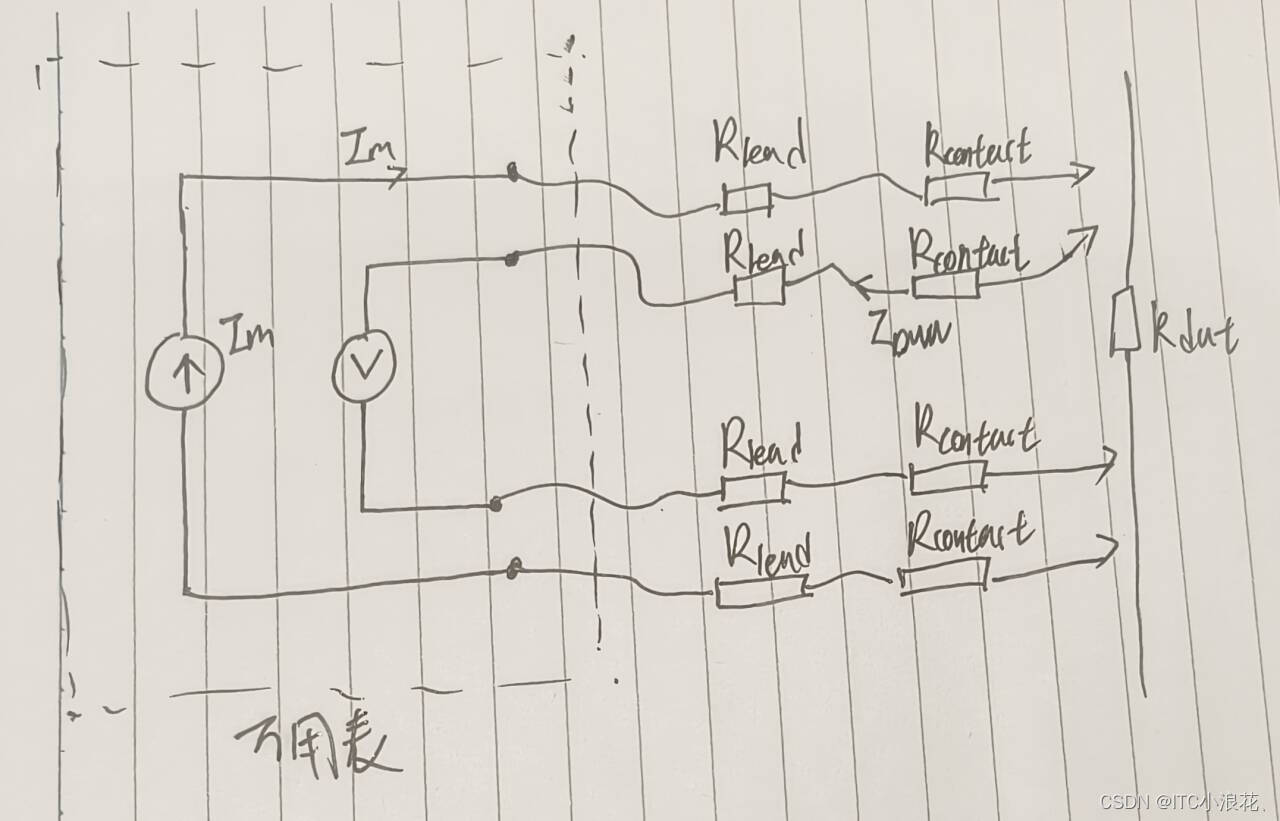

理解四线测电阻得先理解两线测电阻,两线测电阻时电路图如下:

万用表测量电阻的标准步骤:

-

准备万用表:确保万用表处于良好的工作状态,并且已经校准。

-

选择适当的量程:根据待测电阻的预期值选择合适的量程。量程的选择应确保测量的准确性,同时避免对万用表或待测电阻造成损害。

-

连接测试线:将万用表的红色测试线(通常表示正极)连接到待测电阻的一个端点,黑色测试线(表示负极)连接到另一个端点。

-

输入电流:万用表将向待测电阻 𝑅𝑑𝑢𝑡Rdut 输入一个已知大小的电流 𝐼𝑚Im。这个电流的大小取决于万用表选择的量程,较低的量程会产生较大的电流,例如1毫安或几个毫安;而较高的量程则产生较小的电流。

-

测量电压:万用表内置的电压测量功能将准确测量通过待测电阻 𝑅𝑑𝑢𝑡Rdut 两端的电压。

-

计算电阻:使用欧姆定律 𝑅=𝑉𝐼𝑚R=ImV 计算待测电阻的值,其中 𝑉V 是测量到的电压,𝐼𝑚Im 是通过电阻的电流。

-

读取和记录结果:读取万用表上显示的电阻值,并进行记录。

-

断开连接:测量完成后,断开测试线,并将万用表设置回至安全状态或关闭电源,以延长设备寿命。

-

分析结果:根据测量结果分析电阻值是否在预期范围内,或是否需要进一步检查。

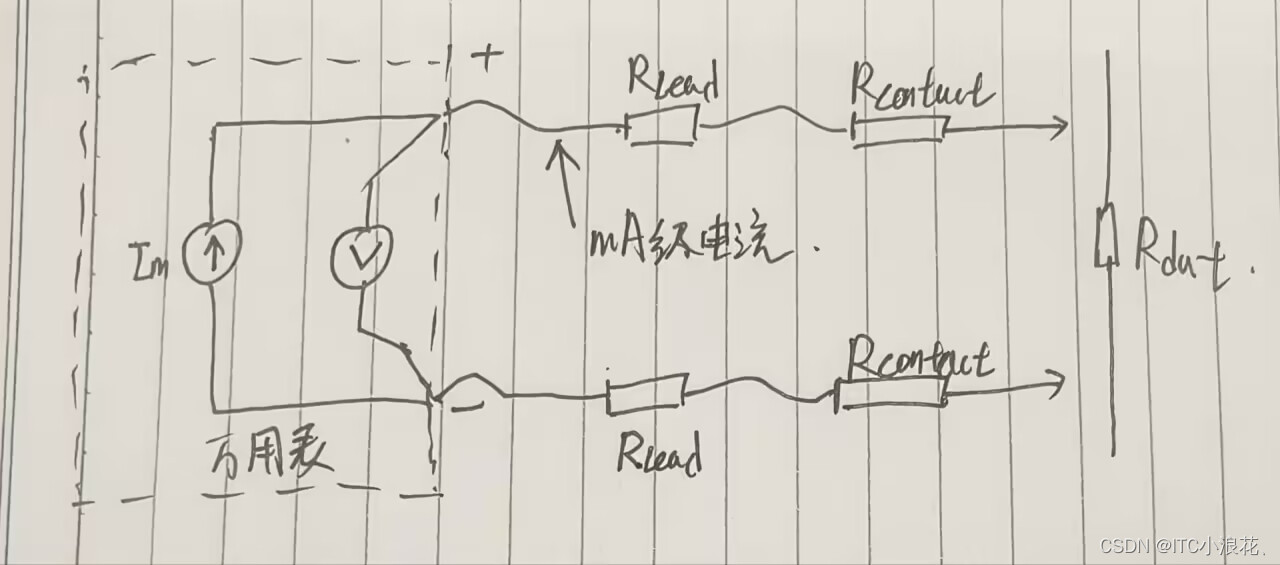

(2)误差

当进行低电阻测量,尤其是待测电阻值接近或小于1Ω时,测试的准确性会受到几个因素的影响,其中包括表笔自身的电阻(𝑅𝑙𝑒𝑎𝑑Rlead)和接触电阻(𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡Rcontact)。以下是对您提供信息的润色和详细说明:

表笔电阻的影响: 当测量非常低的电阻值(1Ω或更小)时,万用表的表笔电阻 𝑅𝑙𝑒𝑎𝑑Rlead 不可忽略,因为它会直接串联到测量电路中,从而影响测量结果。

-

接触电阻的重要性: 接触电阻 𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡Rcontact 也可能相对较高,可能达到几百毫欧姆,它与表笔的清洁度、接触力度和接触表面的条件有关,这些因素都会对测量精度产生显著影响。

-

万用表读数的计算: 万用表显示的电阻值实际上是待测电阻 𝑅𝑑𝑢𝑡Rdut 加上两倍的表笔电阻和两倍的接触电阻的总和,即: 万用表显示结果=𝑅𝑑𝑢𝑡+2×𝑅𝑙𝑒𝑎𝑑+2×𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡万用表显示结果=Rdut+2×Rlead+2×Rcontact

(3)举例1

让我们通过一个具体的例子来阐释两线法测量电阻时可能遇到的局限性,并通过数字对比来直观展示问题所在。

假设条件如下:

- 表笔自身的电阻 𝑅𝑙𝑒𝑎𝑑=0.7Ω

- 接触电阻 𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡=0.2Ω

- 待测电阻 𝑅𝑑𝑢𝑡=0.3Ω

- 万用表的精度为 ±0.1%

计算万用表的测量结果:

𝑅𝑚𝑒𝑎𝑠=(0.7Ω×2)+(0.2Ω×2)+0.3Ω±0.0021Ω

𝑅𝑚𝑒𝑎𝑠=2.1Ω±0.0021Ω

其中,±0.0021Ω 是万用表的误差,它是 (0.7Ω×2+0.2Ω×2+0.3Ω)×±0.1%的计算结果。

如果不计入表笔电阻和接触电阻,理想的测量结果应该是:

𝑅𝑖𝑑𝑒𝑎𝑙=0.3Ω±0.0021Ω

通过比较,我们可以发现实际测量值仅为𝑅𝑚𝑒𝑎𝑠的0.3Ω ±0.0021Ω≈0.7%,而𝑅𝑚𝑒𝑎𝑠则是 𝑅𝑖𝑑𝑒𝑎𝑙的大约7倍。这说明,两线法测量结果的误差是非常大的,以至于几乎无法使用。

误差的根源:

误差之所以如此之大,是因为在两线测量法中,所测量的电压包含了由表笔电阻𝑅𝑙𝑒𝑎𝑑和接触电阻 𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡引起的电压降。

解决方案:

为了解决这一问题,可以采用四线法测量电阻,这种方法通过独立控制电流注入和电压测量,从而有效地消除了表笔电阻和接触电阻对测量结果的影响。四线法,也称为开尔文测试法,能够提供更精确的电阻测量,尤其适合于测量低电阻值。

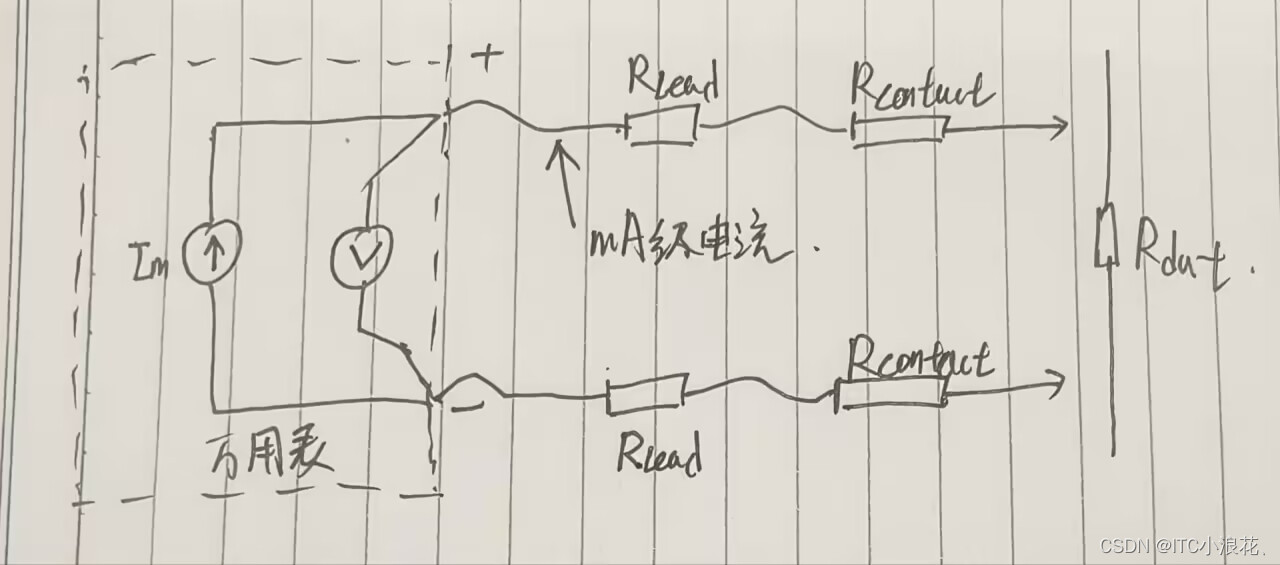

(4)四线测电阻法

四线法测电阻技术,也称为开尔文测电阻法,通过将电流注入线和电压测量线分开,显著提高了电阻测量的准确性。

四线法测电阻的原理:

-

独立的电流和电压路径:在四线法中,存在两对线缆——一对用于向待测电阻 𝑅𝑑𝑢𝑡Rdut 提供恒定电流,另一对用于测量该电阻两端的电压。

-

忽略接触电阻和表笔电阻:由于电流注入线和电压测量线是分开的,因此表笔自身的电阻 𝑅𝑙𝑒𝑎𝑑Rlead 和接触电阻 𝑅𝑐𝑜𝑛𝑡𝑎𝑐𝑡Rcontact 对测量结果的影响可以忽略不计。这是因为这些电阻不再包含在电压测量的路径中。

-

直接测量待测电阻的压降:使用四线法,我们直接测量的是通过待测电阻 𝑅𝑑𝑢𝑡Rdut 时产生的电压降,这提供了一个更真实的电阻值。

-

提高测量精度:通过消除了表笔电阻和接触电阻的影响,四线法能够提供更高的测量精度,特别适用于低电阻值的测量。

四线法测电阻之所以能够提供比两线法更高的测量精度,关键在于电压测量线的大输入阻抗。尽管电压测量线和表笔本身也存在一定的电阻和接触电阻,但由于电压表的输入阻抗极高,通常可达几百千欧姆至10兆欧姆,这使得流过电压表的电流微乎其微,通常在纳安或皮安的量级。

在两线法中,电压表测量的是流过大电流(毫安级)的表笔电阻、接触电阻以及待测电阻的总压降,这些因素共同构成了测量误差的来源。而在四线法中,尽管同样测量了表笔电阻、接触电阻和待测电阻的总压降,但由于电压表的大输入阻抗,流过其的电流极小,相对于流过待测电阻的电流(通常为毫安级)可以忽略不计。

因此,当待测电阻非常小,仅为几个欧姆或更小时,四线法能够显著降低测量误差,提供更为精确的测量结果。这一点是理解四线法优势的核心所在。

(5)举例2

让我们通过一个具体数值的例子来直观展示四线法测量电阻的高精度优势。

假设条件:

- 待测电阻的阻值为 𝑅𝑑𝑢𝑡=0.3Ω

- 万用表输出的电流为 𝐼𝑚=1𝑚𝐴

计算待测电阻两端的电压降:

𝑉𝑑𝑢𝑡=𝐼𝑚×𝑅𝑑𝑢𝑡=1𝑚𝐴×0.3Ω=0.3mV

计算进入电压表的电流:

假设电压表的输入阻抗为 𝑍𝑖𝑛=10𝑀Ω,则进入电压表的电流 𝐼𝑑𝑣𝑚为:

𝐼𝑑𝑣𝑚≈𝑉𝑑𝑢𝑡/𝑍𝑖𝑛=0.3𝑚𝑉/10𝑀Ω=30𝑝𝐴

估算电压表引起的压降(误差):

对于 30𝑝𝐴的电流,电压表引起的压降(即误差)将会非常小,小于1𝑛𝑉。因为:

Δ𝑉𝑒𝑟𝑟𝑜𝑟=𝐼𝑑𝑣𝑚×𝑍𝑖𝑛<30𝑝𝐴×10𝑀Ω

Δ𝑉𝑒𝑟𝑟𝑜𝑟<1𝑛𝑉

分析误差的影响:

1nV 的压降相对于待测电阻两端的0.3𝑚𝑉压降是极其微小的,可以认为对测量结果的影响是微不足道的。

结论:

由于电压表具有极高的输入阻抗,流过其的电流极小,导致电压表引起的压降(即测量误差)相对于待测电阻的压降来说可以忽略不计。因此,四线法能够提供非常精确的测量结果,特别适合于测量低阻值电阻,如几个欧姆或更小的电阻值。

13、DC测试(一)

在半导体行业中,DC测试(直流测试)是一种用于检测半导体器件或集成电路(IC)的电气特性的测试方法。DC测试主要关注器件在直流条件下的行为,包括其静态特性,例如:

-

电流-电压(I-V)特性:测试器件在不同电压下的电流响应,以确定其导通、截止行为和漏电流水平。

-

阈值电压(Vth):对于场效应晶体管(如MOSFETs),测试其开启和关闭的电压阈值。

-

通道长度调制效应:评估当漏极电流变化时,晶体管通道长度的变化对器件特性的影响。

-

饱和区、线性区和亚阈值区特性:分析晶体管在不同操作区域的电气行为。

-

负载特性:测量器件在不同负载下的输出电压和电流。

-

电容效应:评估寄生电容对器件性能的影响。

-

温度效应:测试温度变化对器件特性的影响。

-

噪声特性:测量器件的噪声水平,这对于模拟和射频应用尤为重要。

DC测试对于确保半导体器件满足设计规格和性能要求至关重要。它通常在半导体制造的各个阶段进行,包括:

- 设计验证:在设计阶段,验证器件设计是否符合预期的电气特性。

- 工艺监控:在生产过程中,监控制造工艺是否稳定并符合质量标准。

- 最终测试:在封装前对单个器件进行测试,确保它们在出厂前满足所有电气参数要求。

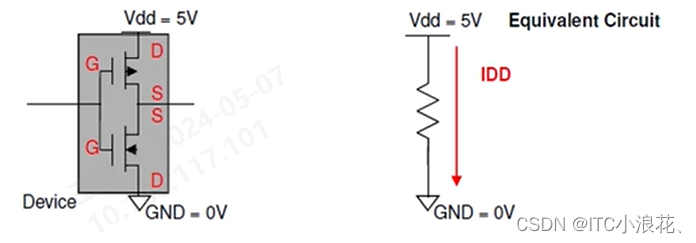

IDD(或ICC)测试,它用于测量CMOS(互补金属氧化物半导体)电路或TTL(晶体管-晶体管逻辑)电路中的特定电流。

-

IDD/ICC的定义:IDD(或ICC)是指在CMOS电路中从漏极(Drain)流向漏极的电流,或者在TTL电路中从集电极(Collector)流向集电极的电流。

(1)IDD/ICC测试的类型

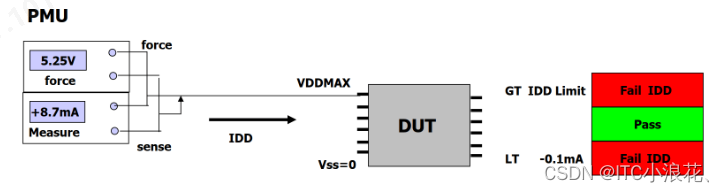

1:Gross IDD/ICC Tests

粗略IDD/ICC测试,可能用于检测明显的电流泄漏问题。

测 试 步 骤:

1. 给芯片的电源管脚force一个VDDmax电压

2. 给芯片的所有输入管脚force高电平/低电平

3. 或者执行复位的操作。

4. 等待5-10ms。

5. 测试VDD的电流 。

Gross IDD调试技巧 :

要开始故障排除,请打印数据记录并观察测量结果。

如果有已知良好的芯片(通常称为标准或黄金 DUT),请对其进行测试并观察测量结果。

结果将是三种可能性之一。

1. 流正确,测试结果合格。

2. 电流大于最大限值,测试结果不合格。

3. 电流小于最小限值,测试结果为失败。

排查问题步骤:

Ø 可以从测试插座中取出芯片并空测。 空测的结果应为零电流;

Ø 如果不是0,则电流正在被 DUT 以外的其他物体消耗。

Ø 对于没有 DUT 的非零电流,请移除测试硬件的某些组件,直到找到问题根源。(如,移除负载板并运行测试)

Ø 也可以使用电阻器来代替DUT,并可以验证测量系统的准确性。

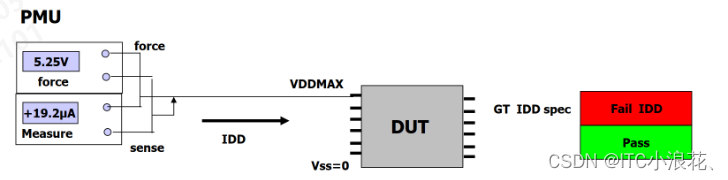

2:Static IDD/ICC Tests

静态IDD/ICC测试,通常在没有信号切换的情况下进行,以测量电路的静态功耗。

测试目的 :

Static 静态,表示测量是在 DUT 未激活时进行的。

测量的是流入 VDD 引脚的总电流一般需要 DUT 运行在最低功耗的模式下。

确保 DUT 消耗的电流不会超过规范中的可用值。这对于电池供电的设备很重要。

识别 CMOS 器件的工艺问题。

测试注意事项:

1. 应准确地对 DUT 进行预处理,使其达到消耗 IDD 电流最少的状态。

2. 如果IDD电流较小,应给予额外的延迟时间。

3. 使用继电器断开外部旁路电容器,以避免测得的IDD 电流偏低的问题。

4. 将 DUT 保持在静态条件下测量流入电源引脚的电流量,并与 IDD静态电流的指标进行比对。

测试步骤:

1. 给芯片的电源管脚force一个VDDmax电压。

2. 根据芯片功能,通过pattern将芯片预置到static模式。

3. 等待1-5ms。

4. 测试VDD的电流。:

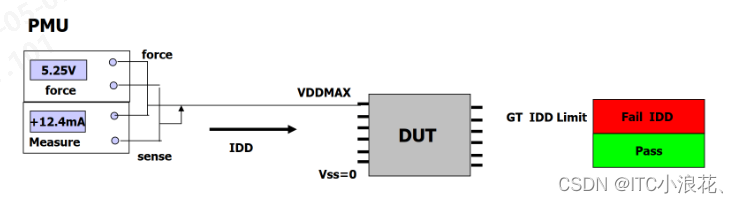

3:Dynamic IDD/ICC Tests

动态IDD/ICC测试,涉及信号切换,以测量电路在工作时的平均电流消耗。

测试目的 :

动态IDD是器件的运行IDD。

IDD 动态电流测试可确保当 DUT 工作时,DUT 消耗的电流不会超过器件规格中规定的值。

该测试测量流入电源引脚的总电流。

执行测试向量时,通常以 DUT 的最大工作频率进行。

将所得电流测量结果与 IDD 动态器件规格进行比较。

测试注意事项:

1. 当 DUT 在最大工作频率下由连续模式驱动时,测量动态 IDD。

2. VIL、VIH、VDD、Fmax 影响测试结果。

3. 重复测试时,动态 IDD 应产生一致的结果

Dynamic IDD的测试是将芯片预处理为最大功耗的情况下,测试其IDD的最大漏电流。

设计人员应该准备合适的向量序列以完成对器件的预处理,将器件带入最高功耗的工作模式,如果向量的效果不理想,则需要进一步完善,精准的预处理序列也是进行动态IDD 测试的关键。

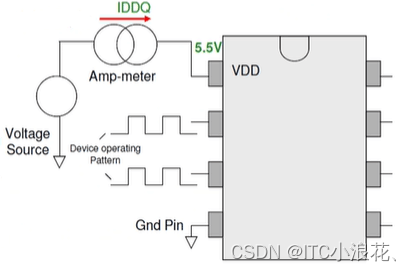

4:Quiescent IDD/ICC Tests

空闲IDD/ICC测试,测量电路在没有输入信号或在空闲状态时的电流消耗。

测试目的:

随着处理器尺寸的缩小,漏电流的缺陷变得更加严重,

IDDQ 测试可以检测到电路核心内的微小缺陷,而这些缺陷

是其他方式无法检测到的。

1. 将 VDDmax 应用到 VDD 引脚(使用电流钳位)。

2. 将 DUT 预先设置为某种工作状态(打开/关闭某些功能部分,例如蓝牙和 Wi-Fi)。

3. 测量流入 VDD 引脚的电流:

• 高于规格值:失败

• 低于规格值:通过

4. 重复测试不同的工作状态。

14、DC测试(二)

(1)输出电压和电流

VOL 表示低电平(L)输出(O)时的最高电压(V)限制(不会被识别成逻辑 1)。

IOL 表示低电平(L)输出(O)时灌电流(I,sink)的驱动能力。

它们共同衡量的是引脚 Buffer 在输出低电平时的阻抗,保证在适当输出的电压下能吸收恒定的电流值。

VOH 表示高电平(H)输出(O)时的最低电压(V)限制(不会被识别成逻辑 0)。

IOL 表示高电平(H)输出(O)时拉电流(I,source)的驱动能力。

它们共同衡量的是 Buffer 在输出高电平时的阻抗,保证在适当输出的电压下能输出恒定的电流值。

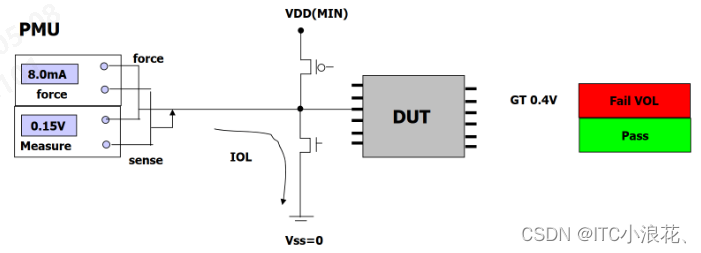

1:VOL/IOL 测试 - 串行静态法

测试流程如下:

- 需要先通过预处理,将待测引脚设置为低电平输出。

- 向引脚施加恒定的 IOH,等待 1-5 毫秒再测量(在 PMU 设 delay)。

- 检测引脚电压

- 高于 VOL(+0.4V):Fail

- 其他区间:Pass

需要注意的事项:

- IOL 是一个正电流值,因为它是从 PMU 流向 DUT。

- 因为施加的是恒流,所以需要设置电压钳,如果测出电压比钳位电压还低,有可能是逻辑设成了高电平,触发了对电源保护二极管正偏。

- VDDmin 参数表示能使 DUT 正常进行测试的最小供电电压,再小将无法得出准确的测试结果。

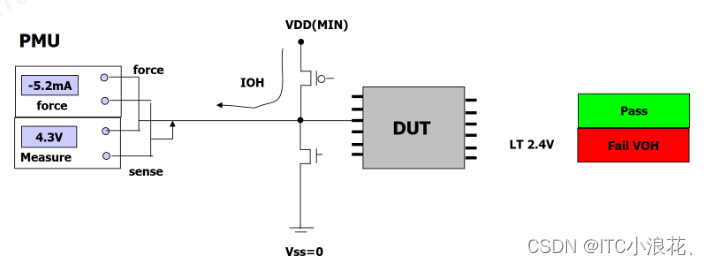

2:VOH/IOH 测试 - 串行静态法

测试流程如下:

- 需要先通过预处理,将待测引脚设置为高电平输出。

- 向引脚施加恒定的 IOH,等待 1-5 毫秒再测量(在 PMU 设 delay)。

- 检测引脚电压

- 低于 VOH(+2.4V):Fail

- 其他区间:Pass

需要注意的事项:

- 因为 IOL 是从 PMU 流向 DUT,所以它是一个负值。

- 因为施加的是恒流,所以需要设置电压钳,如果测出电压比钳位电压还高,有可能是引脚逻辑设成了低电平,触发了对地保护二极管正偏。

- VDDmin 参数表示能使 DUT 正常进行测试的最小供电电压,再小将无法得出准确的测试结果。

(2)输入电压电流

IIL (Input Current Low): 指的是输入引脚在低电平逻辑状态下,允许的最大拉电流。这是衡量输入引脚在低电平状态下向外部电路提供电流的能力。

IIH (Input Current High): 指的是输入引脚在高电平逻辑状态下,允许的最大灌电流。这是衡量输入引脚在高电平状态下从外部电路吸收电流的能力。

VIH:芯片输入引脚为高电平时的最小电压。

测量方法:

- 设置芯片的VDD引脚电压至VDDmin。

- 逐渐降低输入引脚电压,直到芯片功能开始失败,此时的电压即为VIH。

设置芯片输入引脚电压为VIH,

验证芯片功能, 如果芯片功能PASS,则PASS,

反之则FAIL, 找VIH的方式是输入电压从VDD往低做SHMOO测试。

VIL:芯片输入引脚为低电平时的最大电压。

测量方法:

- 在VDDmin和VDDmax条件下,分别设置芯片的VDD引脚电压。

- 逐渐增加输入引脚电压,直到芯片功能开始失败,此时的电压即为VIL。

设置芯片输入引脚电压为VIL,

验证芯片功能, 如果芯片功能PASS,则PASS,

反之则FAIL, VIL要测试两次,分别在VDD=VDDmax和VDD=VDDmin时测试。

找VIL的方法是输入电压从0V往高做SHMOO测试。

(需要在VDDmin和VDDmax条件下分别进行。首先设置芯片的VDD引脚电压至VDDmin或VDDmax,然后逐渐增加输入引脚电压,直到芯片功能开始失败。此时记录的电压值即为VIL。)

SHMOO测试: 描述中提到了SHMOO测试,这是一种逐步调整输入电压的方法,用于确定VIH和VIL的准确值。在实际操作中,应确保:

- 对于VIH,从VDDmin开始,逐渐降低输入电压,直到芯片功能失败。

- 对于VIL,从0V开始,逐渐增加输入电压,直到芯片功能失败。

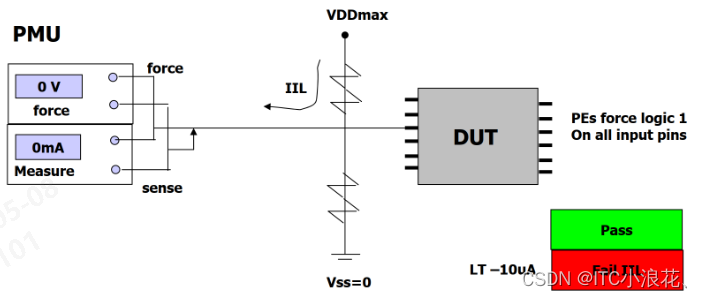

1: IIL测试 - 串行静态法

测试流程如下:

- 首先要供 VDDmax(最差情况)的电源给 DUT。

- 将 DUT 所有输入引脚设高电平(VIH)。

- 使用 PMU 将单个输入引脚拉低到 VSS。

- 等待 1~5 微秒,检测电流值。

- 低于 IIL(-10µA):Fail(灌进 DUT 的电流超标)

- 其他区间:Pass

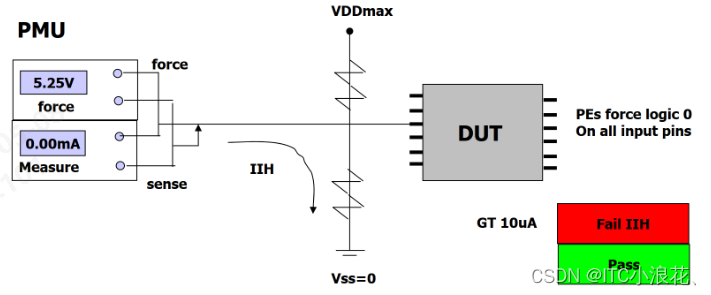

2: IIH测试 - 串行静态法

测试流程如下:

- 首先要供 VDDmax 的电源给 DUT。

- 将 DUT 所有输入引脚设低电平(VIL)。

- 使用 PMU 将单个输入引脚拉高到 VDDmax。

- 等待 1~5 微秒,检测电流值。

- 高于 IIH(+10µA):Fail(流出 DUT 的电流超标)

- 其他区间:Pass

(3)高阻态

Z态( 高阻态 )

高阻态的定义:高阻态这是一个数字电路里常见的术语,指的是电路的一种输出状态,既不是高电平也不是低电平。

高阻态可做开路理解,你可以把它看作输出(输入)电阻非常大。它的极限可以认为悬空,也就是说理论上高阻态不是悬空,它是对地或对电源电阻极大的状态。而实际应用上与引脚的悬空几乎是一样的。

IOZH:

指的是当一个高电平(H)施加在一个处于高阻态(Z)的输出管脚(O)上,管脚上产生的漏电流(I)。

IOZL:

指的是当一个低电平(L)施加在一个处于高阻态(Z)的输出管脚(O)上,管脚上产生的漏电流(I);

测试目的:

1. 测量输出引脚到地/VDD 的电阻。

2. 确认双向和高阻抗输出能够实现高阻抗或关闭状态。

3. 识别 CMOS 器件中的处理问题。

1、IOZH测试流程如下:

1.首先需要给器件供 VDD 的电源。

2.将器件引脚预设为高阻状态,使用

PMU 强制将引脚拉高。

3.测量引脚的电流值

1. 低于 -IOZ(-2µA):Fail

2. 高于 +IOZ(+2µA):Fail

3. 其他区间:Pass

2、IOZL测试流程如下:

1.首先需要给器件供 VDD 的电源。

2.将器件引脚预设为高阻状态,使用

PMU 强制将引脚拉低。

3.测量引脚的电流值

1. 低于 -IOZ(-2µA):Fail

2. 高于 +IOZ(+2µA):Fail

3. 其他区间:Pass

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?