在介绍引脚之前,我们先来了解一下Intel 8086 的I/O 地址空间:

CPU与外部设备之间通过IO接口(端口)进行连接

端口:接口中的寄存器

端口号:端口中寄存器的地址编号

用低16位地址为其编号,共有64K个端口号。

Intel 8086 的引脚功能(难点)

CPU引脚生成系统总线:ABUS、DBUS、CBUS联接ROM、RAM、I/O 接口形成微型计算机。8086CPU的40条引脚信号可按功能分可分为四类,它们是:

- 地址总线

- 数据总线

- 控制总线

- 其它(时钟与电源)

1、指令周期、总线周期和时钟周期

- 指令周期(Instruction Cycle) : 执行一条指令所需要的时间称为指令周期,不同指令的指令周期不等长。

- 总线周期(Bus Cycle) : CPU与外部交换信息总是通过总线进行的,CPU的每一个这种信息输入、输出过程需要的时间称为总线周期,每当CPU要从存储器或输入输出端口存取一个字节或字就需要一个总线周期。一个指令周期由一个或若干个总线周期组成。

- 时钟周期(Clock Cycle) :时钟脉冲的重复周期称为时钟周期,由计算机的主频决定。

2, Intel 8086微处理器的最小/最大模式

-

最小模式:

在系统中只有一个微处理器。最小模式下的引脚功能:

(1),AD15~AD0 ,地址/数据复用引脚

数据总线:双向、三态信号

地址总线:输出、三态信号

(2),A19/S6~A16/Ss,地址/状态总线复用,输出,三态

(3),M/IO,存储器/输入输出操作选择控制信号,输出,三态

高电平:CPU和存储器进行数据传输。

低电平:CPU和I/О设备进行数据传输。

-

ALE,地址锁存允许信号,输出

实现地址信息与数据信息的分时复用。

-

DT/R,数据发送/接收控制信号,三态,输出

-

DEN,数据允许信号,输出,三态

与总线收发器联络

-

INTR,可屏蔽中断请求信号,输入

-

NMI,非屏蔽中断请求信号,输入

-

INTA,中断响应信号,输出,三态

-

READY,准备就绪,输入信号

当被访问的部件无法在8086CPU规定的时间内完成数据传送时与CPU进行联络的信号。

-

TEST ,测试输入信号

-

RESET,复位输入信号

复位信号高电平至少应保持4个时钟周期,随着RESET变为低电平,CPU就开始执行再启动过程。CPU复位之后,从FFFFOH单元开始读取指令字节。

-

HOLD,总线保持请求信号,输入

-

HLDA,总线保持响应信号,输出

其它设备要获得系统总线的控制权与CPU的一对联络信号。

-

CLK,时钟输入端

为微处理器提供基本的定时脉冲

-

VCC ,电源输入

要求接上正电压(+5V±10%)

-

GND,地线

最大模式与最小模式之间的主要区别是:在最大模式下,需要增加一个转换控制信号的电路,用来对CPU 发出的控制信号进行变换和组合,即8288总线控制器。

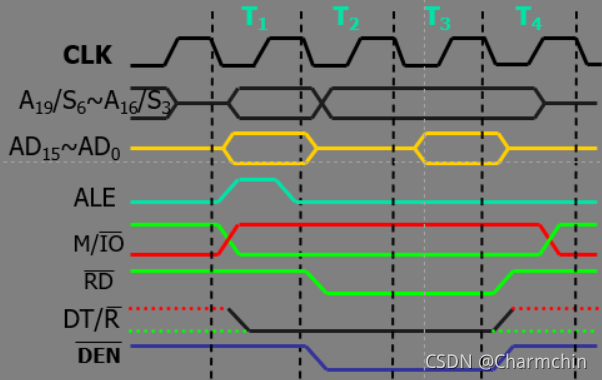

3,Intel 8086 微处理器基本时序

工作时序:微型计算机的工作是在时钟的驱动下进行的,微机的所有操作都是通过时钟节拍一步步给出不同信号来完成,这种时钟作用下的信号过程称为工作时序。

T1:地址周期

T2:数据准备周期

T3:数据读取周期

T4:结束周期

本文详细介绍了Intel8086微处理器的I/O地址空间,以及CPU与外部设备的交互方式。在最小模式下,8086的引脚功能包括地址/数据复用、存储器/输入输出操作选择等,并详细阐述了如ALE、M/IO等关键信号的作用。此外,还解析了8086的指令周期、总线周期和时钟周期,以及基本工作时序T1至T4。最后,讨论了最大模式与最小模式的区别,并提到了8288总线控制器的角色。

本文详细介绍了Intel8086微处理器的I/O地址空间,以及CPU与外部设备的交互方式。在最小模式下,8086的引脚功能包括地址/数据复用、存储器/输入输出操作选择等,并详细阐述了如ALE、M/IO等关键信号的作用。此外,还解析了8086的指令周期、总线周期和时钟周期,以及基本工作时序T1至T4。最后,讨论了最大模式与最小模式的区别,并提到了8288总线控制器的角色。

7848

7848

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?