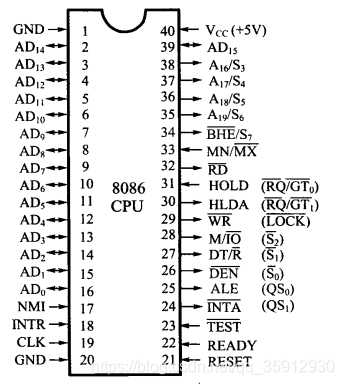

40引脚的双列直插式(Dual-In-line Package,DIP)封装

(1) A D 15 ∼ A D 0 AD_{15} \sim AD_0 AD15∼AD0 地址/数据总线(Address Data Bus )

-

对于8086 功能:CPU访问内存或I/O设备时,先从AD线上给出地址线,将地址信号用锁存器锁存,再在AD线上传送数据。

-

对于8088 功能:

- A D 7 ∼ A D 0 AD_{7} \sim AD_0 AD7∼AD0既可以传送地址,又可以传送数据。

- A 15 ∼ A 8 A_{15} \sim A_8 A15∼A8只用来传输地址信息。

(2) A 19 / S 6 ∼ A 16 / S 3 A_{19}/S_6 \sim A_{16}/S_3 A19/S6∼A16/S3 地址状态线 ( Address/Statues )

- 在 T 1 T_1 T1周期作为高4位地址线,存储器操作时需锁存,I/O操作时,高4位无效,仅有低16位即可。

- 在 T 2 ∼ T 3 T_2 \sim T_3 T2∼T3周期,作状态信号使用。 S 6 S_6 S6始终未低电平; S 5 S_5 S5=1时允许可屏蔽中断, S 5 S_5 S5=0时禁止可屏蔽中断。 S 4 , S 3 S_4,S_3 S4,S3用来指出当前正在访问那个段寄存器。

| S 4 S_4 S4 S 3 S_3 S3 | 状态 |

|---|---|

| 00 | ES |

| 01 | SS |

| 10 | CS |

| 11 | DS |

(3) M / I O ‾ M/ \overline{IO} M/IO 存储器或I/O端口控制信号(Memory/Input and Output)

- 高电平时,表示CPU正在访问存储器;

- 低电平时,表示CPU正在访问I/O端口。

(4) W R ‾ \overline{WR} WR 写控制信号( Write )

- 功能:低电平时允许CPU对存储器或I/O端口进行写入操作。

(5) R D ‾ \overline{RD} RD 读控制信号 ( Read )

- 功能:低电平时允许CPU从存储器或I/O端口读出数据。

(6) R E S E T RESET RESET 复位信号 ( Reset )

-

功能:

- CPU立刻停止当前所有的操作,总线无效;

- DS、ES、SS、FLAGS、IF清0,CS:IP = FFFFH:0000H

- 指令队列变空,禁止中断。

-

特点:

CPU转到FFFF0H处执行指令。

(7) D E N ‾ \overline{DEN} DEN:数据允许信号 ( Data Enable )

- 功能:低电平有效时,允许CPU发送和接受数据

(8) L O C K ‾ \overline{LOCK} LOCK 总线封锁信号

- 功能:低电平有效时,CPU不允许其他主控者获得对总线的控制权。

(9) R E A D Y READY READY 准备就绪信号 ( Ready )

- 功能:该信号为0时,表示被访问的存储器或I/O端口没有准备好,CPU采集到后,在 T 3 T_3 T3周期结束后自动插入等到周期 T W T_W TW,直至READY信号变为1,才进入 T 4 T_4 T4周期。

(10) T E S T ‾ \overline{TEST} TEST 测试信号 ( Test )

- 低电平时,执行WAIT后,程序继续往下运行。

- 高电平时,CPU停止取下条指令而进入等待状态,重复测试 T E S T ‾ \overline{TEST} TEST引脚,直至变为0为止。

(11) B H E ‾ / S 7 \overline{BHE}/S_7 BHE/S7 高8位总线允许/状态信号

- 功能:低电平时,高位数据总线 D 15 ∼ D 8 D_{15} \sim D_8 D15∼D8有效。状态位 S 7 S_7 S7始终为1。

(12) D T / R ‾ DT / \overline{R} DT/R 数据发送/接收信号 ( Data transmit/Receive )

- 高电平时,CPU向外部发送数据,执行写操作;

- 低电平时,CPU接受外部传送过来的数据,执行读操作。

(13) A L E ALE ALE 地址锁存允许信号(Adress Latch Enable)

- 功能:下降沿有效,锁存 A D 15 ∼ A D 0 AD_{15} \sim AD_0 AD15∼AD0的地址信息。

(14) S S 0 ‾ \overline{SS_0} SS0 8088最小模式信号

(15) M N / M X ‾ MN/\overline{MX} MN/MX 最小最大模式选择信号

(16) R Q ‾ / G T 0 ‾ \overline{RQ}/\overline{GT_0} RQ/GT0 ( Request/Grant )

(17) R Q ‾ / G T 1 ‾ \overline{RQ}/\overline{GT_1} RQ/GT1 总线请求信号输入/总线请求允许信号输出

中断有关

(1) I N T R INTR INTR 可屏蔽中断请求信号 ( Interrupt Request )

- INTR=1,表示外设向CPU提出了中断请求:

- 若IF = 1,则CPU暂停执行下条指令,转入中断响应周期,去执行中断服务程序。

- 若IF = 0,则不响应中断。

CPU在执行每条指令后的最后一个时钟周期都要对INTR信号进行检测,检查是否有中断请求

(2) N M I NMI NMI 不可屏蔽中断请求信号 ( Non-MaskableInterrupt )

- 功能:CPU一旦检测道NMI引脚上有正跳变信号,则执行完当前指令后,即转入类型为2的不可屏蔽中断处理程序去执行。

(3) I N T A ‾ \overline{INTA} INTA 中断响应信号 ( Interrupt Acknowledge )

- 功能:在CPU相应外部可屏蔽中断请求后,向外设发出的回答信号。

其他

(1) C L K CLK CLK 时钟信号 ( clock )

(2) V c c V_{cc} Vcc 电源输入

- 功能:提供+5V工作电源。

(3) G N D GND GND 接地引脚( ground )

- 要求:必须接地。

(4)

H

O

L

D

HOLD

HOLD 总线保持请求信号 ( Hold Request )

(5)

H

L

D

A

HLDA

HLDA 总线保持响应信号 ( Hlod Acknowledge )

- 功能:在DMA操作时使用。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?