目录

实施Chiplet技术面临的主要挑战包括:

-

互连技术。Chiplet技术需要开发新型互连技术,以便将小芯片组合在一起。目前,这项技术也尚未完全成熟,需要更多研究和开发。

-

封装技术。Chiplet技术需要开发新型封装技术,以便将不同功能不同工艺制造的小芯片封装在一起。目前,这项技术尚未完全成熟,需要更多研究和开发。

-

生产流程。实施Chiplet技术需要重新设计生产流程,以便将小芯片组合成完整的集成电路。这可能需要许多先进的生产设备和技术,并且需要对现有的生产流程进行重大改造。

-

软件技术。实施Chiplet技术还需要开发相应的软件技术,以便将小芯片集成到一个完整的系统中,并进行编程和配置。这可能需要开发新的软件工具和技术,并且需要对现有的软件技术进行重大升级。

-

测试技术。测试需要在产品的整个生命周期中不断进行,Chiplet技术集成多个不同芯片,需要先测试单个芯片,如何测试封装后的完整系统。必须要有一种封装后测试的方法,并在整个器件的不同使用寿命周期中再次测试。

-

标准。要使Chiplets成长为可行策略,就需要一个生态系统,而生态系统是围绕标准建立的。

让多个小芯片裸片互联起来并最终异构集成成为一个大芯片,面临诸多技术挑战,这其中互连和封装是最需攻克的两大“关卡”。

一、互连技术

可以说,如何让裸片与裸片之间高速互联,是Chiplet技术落地的关键,这对芯片设计公司以及全产业链来说均是一大全新挑战。

由光互联论坛(OIF)定义的电气I/O标准显示,在超短距离和极短距离链路上(裸片与裸片互联)数据传输速率高达112Gbps。芯片设计公司在设计裸片与裸片之间的互联接口时,首要保证的是高数据吞吐量,另外,数据延迟和误码率也是关键要求,还要考虑能效和链接距离。

在互连方面,设计厂商各出奇招。国外厂商,Marvell在推出模块化芯片架构时采用了Kandou总线接口; NVIDIA推出的用于GPU的高速互联NV Link方案;英特尔免费向外界授权的AIB高级接口总线协议;AMD推出的Infinity Fabrie总线互联技术,以及用于存储芯片堆叠互联的HBM接口;Xilinx正在开发OpenHBI,一种源自HBM标准的片间互连/接口技术;Momentum 正在推动铜混合键合,使用微小的铜对铜连接来连接封装中的芯片;光互连论坛正在开发一种称为CEI-112G-XSR的技术,为小芯片实现高速传输的芯片到芯片连接。

国内方面,也有厂商在此展开动作。芯动科技推出了国产自主标准的INNOLINK Chiplet IP和HBM2E等高性能计算平台技术,支持高性能CPU/GPU/NPU芯片和服务器;为了让IP更具象、更灵活的被应用在Chiplet里面,芯原提出了IP as a Chip(IaaC)的理念,旨在以Chiplet实现特殊功能IP从软到硬的“即插即用”,解决7nm、5nm及以下工艺中性能与成本的平衡,并降低较大规模芯片的设计时间和风险。……这些都是芯片设计公司在致力实现高速互联上的不同尝试。关于接口互连这个问题,东西太多了,准备单独开一章记录。

在IC CHINA 2020大会上,芯原董事长戴伟民特别强调了封装和互联对Chiplet的重要性,特别是芯片互联,需要一个一致性协议问题,就涉及到了标准。戴伟民呼吁,国内的Chiplet联盟成员共同参与制定Chiplet技术的互联相关标准。

2021 年 5 月,中国计算机互连技术联盟(CCITA)在工信部立项了《小芯片接口总线技术要求》,由中科院计算所、工信部电子四院和国内多个芯片厂商合作展开标准制定工作。

2022年8月,国际巨头华为、AMD、英特尔积极布局Chiplet并推出相关产品,与此同时,科技巨头们还共同成立了Chiplet标准联盟,正式推出了通用Chiplet的高速互联标准“UCle”。

二、封装技术

而在封装层面,英特尔和台积电在内的巨头都在布局。以下都是概述没图,不好懂,想要看先进封装技术的可以移步:

(21条消息) 傻白入门芯片设计,先进封装技术(五)_好啊啊啊啊的博客-CSDN博客

(20条消息) 傻白入门芯片设计,典型的2D/2D+/2.5D/3D封装技术(六)_好啊啊啊啊的博客-CSDN博客

(1)英特尔

英特尔在异构互联的道路上已进行了长期投入,多年前就推出了EMIB技术,最近又推出了Foveros3D立体封装技术。EMIB技术和Foveros3D立体封装技术都是芯片封装技术,它们都可以将多个芯片连接在一起,形成一个完整的系统芯片。但是,它们在实现方式上有一些区别。

EMIB(Embedded Multi-die Interconnect Bridge)技术:一种嵌入式多芯片互连桥技术,它将多个芯片嵌入在一个封装器中,并在它们之间建立连接,来实现芯片之间的互联。EMIB技术的优势在于,它可以更加紧凑地组织芯片,并可以在芯片之间建立更密集、更灵活的连接,从而提高芯片的性能和效率。

Foveros3D立体封装技术:不同于以往单纯连接逻辑芯片、存储芯片,Foveros可以把不同逻辑芯片堆叠、连接在一起,并在它们之间建立立体连接,从而实现立体的互联,可以“混搭”不同工艺、架构、用途的IP模块、各种内存和I/O单元。Foveros3D立体封装技术的优势在于,它可以更加紧凑地组织芯片,并可以在芯片之间建立更密集、更灵活的连接,从而提高芯片的性能和效率。基于Foveros 3D封装技术,英特尔推出了酷睿处理器“Lakefield”,其中,CPU、GPU核心采用的是10nm工艺,I/O部分所在的基底层则是22nm工艺制造。

(2)台积电

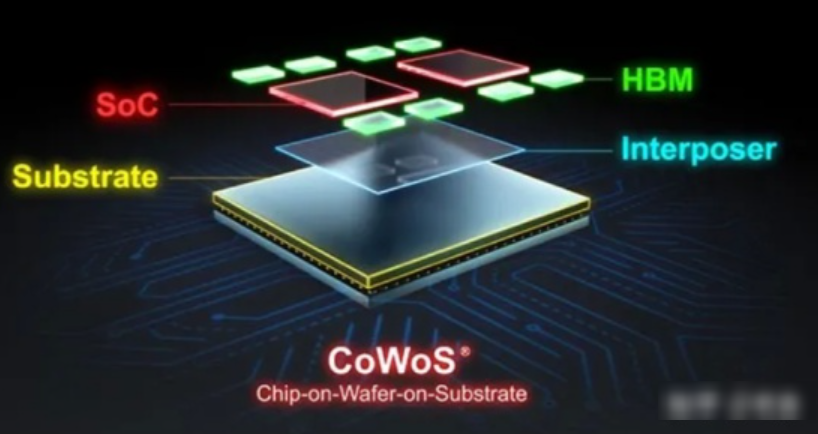

台积电作为代工巨头,自然也在重兵押注。一年前,台积电曾展示一款基于ARM内核、采用Chiplet概念设计的芯片产品,利用了台积电7nm工艺、LIPINCON互联和CoWoS封装技术制造。LIPINCON是一种高速串行总线,它是台积电多年前就开始研发的裸片之间数据互联接口技术。CoWoS是台积电推出的 2.5D封装技术,称为晶圆级封装,通过芯片间共享基板的形式,将多个裸片封装在一起,主要用于高性能大芯片的封装。

台积电基于Chiplet理念的成功设计向业界传递了一种示范效果,对于想使用Chiplet理念来设计芯片但又没有能力自研芯片接口的Fabless厂商,采用台积电现成的接口LIPINCON IP无疑将极具吸引力。

三、生产流程

实施Chiplet技术需要重新设计生产流程,以便将小芯片组合成完整的集成电路。Chiplet技术与传统的芯片设计方式有所不同。传统的芯片设计方式是将所有的电路元件集成在一个工艺层上,并通过一系列的生产流程将它们组合成完整的芯片。而Chiplet技术则是将电路元件分解成较小的部分,并将这些部分组合成完整的芯片。因此,实施Chiplet技术需要重新设计生产流程,以便更好地处理这种分解和组合的过程。

重新设计生产流程可能需要许多先进的生产设备和技术,并且需要对现有的生产流程进行重大改造。这些技术和流程的开发和实施都需要投入大量的时间和资源,因此它是实施Chiplet技术的主要挑战之一。

总而言之,实施Chiplet技术需要重新设计生产流程,以便将小芯片组合成完整的集成电路。这需要攻克的技术挑战主要包括:

-

设计新的生产流程,以便能够将多个小芯片组合成一个完整的集成电路。

-

购置新的生产设备,以便能够满足生产要求,并能够实现高质量的封装和互联。

-

对现有的生产流程进行重大改造,以便能够支持新型的Chiplet技术。

-

训练生产人员,以便能够操作新型设备和流程,并保证生产质量。

因此,生产流程是实施Chiplet技术的一个重要挑战,需要重新设计生产流程,购置新的生产设备,并对现有的生产流程进行重大改造。

四、软件技术

Chiplet技术需要开发新型软件技术,以便将芯粒组合在一起,并将它们与外部设备进行交互。这需要攻克的技术挑战主要包括:

-

开发新的软件工具和技术(EDA工具),以便将多个芯粒组合成一个完整的集成电路。

-

对现有的软件技术进行升级,以便能够支持新型的Chiplet技术。

-

编写新的程序代码,以便将多个芯粒集成到一个完整的系统中,并进行配置和编程。

-

与外部设备进行交互,以便能够实现完整的系统功能。

因此,软件技术是实施Chiplet技术的一个重要挑战,需要开发新的软件工具和技术,并对现有的软件技术进行升级。

五、测试技术

测试需要在产品的整个生命周期中不断进行。测试方法因应用而异,也因器件而异。然而,仍有一些常见的问题需要解决。可测试性是一个挑战,特别是一旦这些小系统被封装在一起,只有数量较少的测试引线可以延伸到封装外。因此,测试必须分阶段进行,先测试单个的芯片,然后测试封装后的完整系统。对于任何给定的芯片,即使测试完成了,仍然可能有百万分之三的部件会失败。如果在同一个系统中有20个不同的芯片,整体失败率会成倍增长,所以失败的概率非常高。有多种方法可以克服这些问题进行测试,但最终还是要有正确的接口。必须确保每个芯片都有正确的协议,以便测试信号可以从封装I/O一直传递到顶部芯片并得到收集,这是一个挑战。

此外,还有挑战在于找出在某些应用场景中什么测试方法是足够好的,这个问题并没有完全解决。从可靠性的角度来看,这让事情变得更加复杂。在3D封装中,也需要进行可测性设计(DFT)。必须有一种封装后测试的方法,并在整个器件的不同使用寿命周期中再次测试。这可能是一个重大挑战。例如,一家供应商可能想要使用另一家公司的芯片。但这家公司可能不想分享芯片的内部工作原理,而这对系统的全面特性至关重要。但即使他们愿意分享数据,芯片仍然需要经过验证和测试。

六、标准

要使Chiplets成长为可行策略,就需要一个生态系统,而生态系统是围绕标准建立的。这些标准现在开始出现,对Chiplet的需求正在增加,但对大多数公司来说,这种转变进行缓慢,需要被验证的标准开发出来。目前有很多供应商在研究开发Chiplets,但在谁来定义电子接口,什么是维护标准,需要多少ESD保护,以及在组装过程中,如何将其传输到测试机构和组装工厂等问题上没有统一的标准。使用Chiplets的一个大挑战是理解有关芯片和互连的所有信息并建立标准,特别是当使用更多的第三方Chiplets时。

大多数专家认为,芯片行业别无选择,只能朝这个方向发展。但是,从50年来将所有部件(包括整个PCB)都压缩到一个芯片上,到将单独的芯片堆叠在一个先进的封装中,并确保它们在封装系统的预期寿命内可靠工作,这将需要创新,大量的文档,以及在整个过程中如何对芯片进行表征、测试、检查、测量和处理的更多标准。

到目前为止,行业发展只是触及了技术表面。人们正在为这些Chiplet进行研究工作,但还没有一个标准可以让设计师建立一个由几个可以相互交流的Chiplet组成的系统。英伟达有他们所谓的NVLink,AMD有他们的Infinity Fabric,高通有QLink,英特尔有AIB等等。现在,随着生态系统的演变,有必要制定标准,来定义元数据格式中所有必要的特征,如何捕获这些特征和将这些特征存储在什么地方。这与在硬件/软件接口IP管理上遇到的问题类似,而且很多都在进行中。虽然现在可以追踪单个的Chiplets,但行业需要一种标准的方式来标记所有这些信息,从而达成一致。这对于理解如何在三维空间设计器件,并提高器件的整体可靠性有很大帮助。

Chiplet需要一个标准化的接口。标准的好处是有很多东西可供选择。然而,随着越来越多的厂商试图整合该领域,并解决将制造和封装与电气标准相结合的问题,这种情况开始发生变化。他们需要协议来确保跨系统的数据完整性。除此之外,还有一大堆其他问题需要解决,比如物理布局、电力输送网络、测试、调试、监控等。其中一些案例正在研究中。

参考资料:

1349

1349

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?