封装是将芯片的“裸芯”通过膜技术及微细加工技术,固定在框架或基板上,完成粘贴及连接,通过引出接线端子,完成对外的电器互联。随着集成电路产业的发展,流片加工工艺越来越先进,单片集成度越来越高,引出端数目也越来越多,传统四周排布 PAD 的方式,无论是 in-line 或是 stagger,都可能无法满足间隔要求。同时,很多大规模电路功耗较大、所集成的外设速率越来越高,例如高速 SERDES 接口,传输速率高达 12.5GHz,致使传统的引线键合(wire bond)封装技术,由金线带来的寄生参数无法满足设计指标要求,从而必须采用倒装焊封装技术手段,来满足较多的引出端数目、较大的供电能力,以及超高的速率要求。

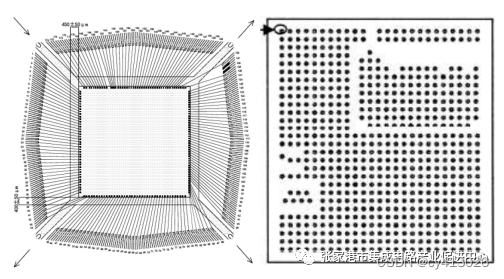

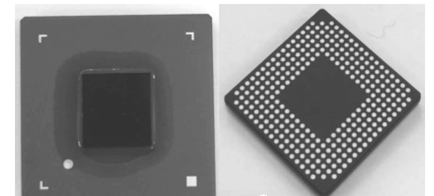

Wire bond 封装和倒装焊封装的区别,一是,前者引出端为四周引出方式,倒装焊封装的引出端为内部二维矩阵排布,二者的封装键合图如图 1 所示。

图 1 引线封装和倒装焊封装示意图

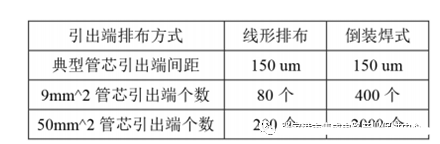

二是,倒装焊封装由四周排布扩展至二维矩阵排布,从而使得引出端数量大幅增加,理论引出端数量对比见表 1。

表 1 封装技术引出端理论数量对比

待封装的是一颗超大规模集成电路芯片,集成了 12.5Gbps 高速 Serdes 硬核,DDR 硬核,LVDS 接口,以及业务处理所需的数据接口。实现工艺为中芯国际(SMIC)65nm,面积达到了 7000 mm×7500mm,管芯引出端数量接近 700 个,封装形式为 CBGA272。

由于整个芯片封装过程中,需要物理版图工程师、Foundry 工程师,与封装厂商三部分高度协同设计。不同身份的设计师,在数据交互时,各自理解不同,容易产生工作冗余迭代,影响效率。所以,将芯片封装过程所涉及的工作内容进行了梳理,展开来进行阐述。

管芯设计内容

此部分主要工作由物理版图设计师完成,针对倒装焊设计与传统引线键合设计的区别进行了阐述。

1)版图布局设计

如图 2 所示,倒装焊封装的 IO 虽然是二维矩阵式(area-IO)排布,但需要注意的是在物理设计时,引出端可以依旧选择四周排布的方式(peripheral-IO)。

图 2 芯片 TOP 层版图

例如本芯片集成的 Serdes 核为硬核形式,IP 设计师给出了图形信息以供走线互连。其他部分的 IO 将按照传统布局方式进行连接。另外,由于本芯片功耗未超过 1W,压降效果不明显,故无需像 FPGA 管芯的设计,从内部做垂直形状的 IO。

2)重布线层设计

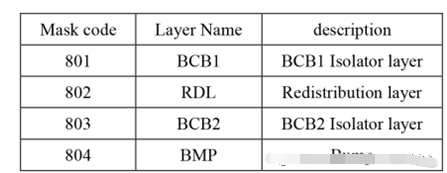

重布线层(RDL,Redistribute Layer)。其为倒装焊设计独有的层,用来对管芯引脚重新走线,最大化的增加引出端数量。在 SMIC 65nm 加工工艺中,重布线层的掩膜板层命名见表 2。

表 2 SMIC 掩膜板代码和层命名规则

在设计时,需要参考 SMIC 的设计规则,主要规则如表 3 和图 3 所示。

表 3 SMIC RDL 层布线规则

图 3 RDL 层设计规则图

表 3 显示了具体规则数值。例如 RDL 布线间距(trace space)不得小于 12um,每个 bump 间距(bump pitch)不得小于 150um 等等规则。

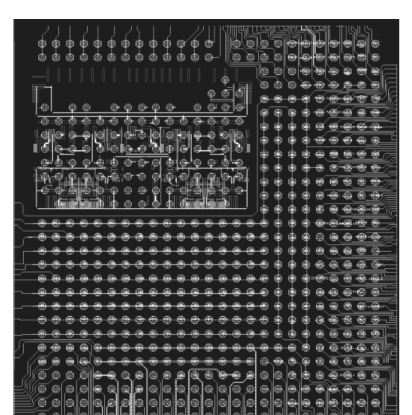

本芯片的目标设计时,结合 BGA272 的封装形式,其 RDL 层布线如图 4 所示。

图 4 芯片 RDL 层版图

完成了整个重布线层版图设计,形成了最终的 GDSII 文件,就可以提交流片数据。

3)版图数据提交

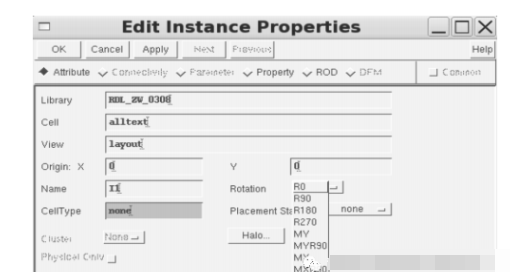

图 5 显示了版图工具中翻转、镜像的设置界面,基此,单颗管芯设计完成后,要提交的版图数据包括:一是需要整理出整颗管芯的尺寸,每个引出端的坐标,是否预留了划片道等信息。二是将该信息交付到流片工程师,完成整版的拼版,此时需要注意的是倒装焊由于是“倒装”的焊接到基板上,需要特别注意是否存在版图镜像、翻转的操作。

图 5 版图工具中翻转、镜像的设置界面

封装设计内容

1)封装信息交互

当完成了目标的 RDL 设计之后,就可以提交流片厂商进行 Wafer 的加工生产了,并进行相关封装信息交互。流片厂商会反馈各种信息,其中有些是需要提供给后道封装的。包括晶片初始厚度、目标减薄厚度,划片道宽度、焊盘尺寸与开口尺寸等信息。

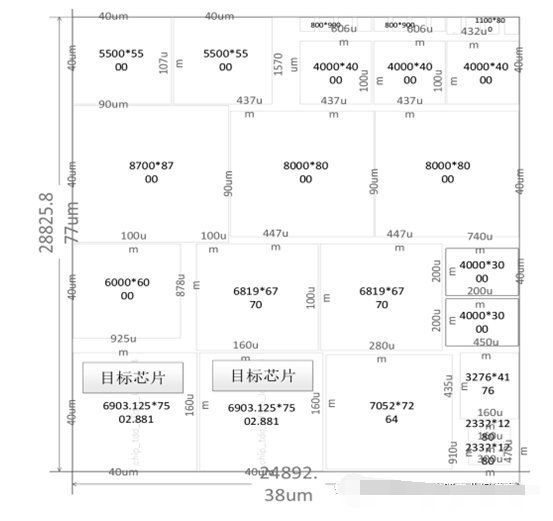

2)UBM 层制作注意事项

凸块底部金属(UBM)层一般为第三方加工厂制作,需要基于整张 Wafer 进行 MASK 设计,需要精度较高的 Floorplan 图(见图 6),以及倒装焊目标芯片的 IO 坐标。将在版图中测量出的间距信息提供至 UBM 厂商,完成 0.01um 级别精度的 MASK 制作。

图 6 UBM 厂商所需的 layout 图

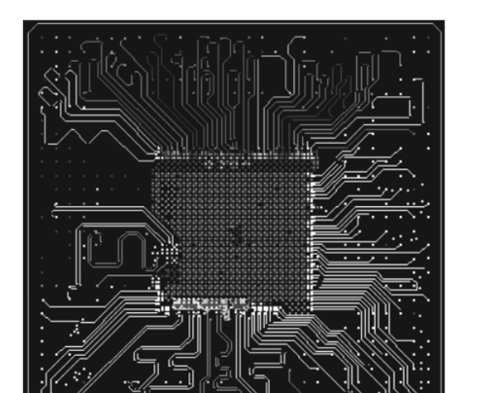

3)基板及外壳制作内容

图 7 是基板走线示意图,从中看出,基板(substrate)设计,与高速 PCB 设计规则类似,主要需要考虑电地及信号的走线,避免串扰,尽可能的降低层数,以便节省成本。

图 7 基板走线示意图

完成了基板设计,如图 8 所示,要结合封装形式进行仿真。

图 8 封装仿真模型

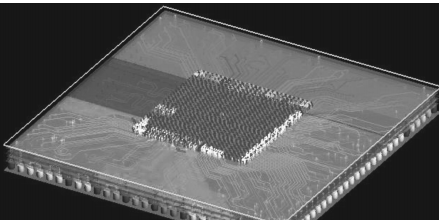

4)封装芯片成品

最终完成封装形式为 CBGA272 的倒装焊封装的芯片实物(见图 9),完成了 bump 植柱,未植焊接球。

图 9 芯片实物照片

总结

毫无疑问,技术没有先进和落后一分,只有是否适用于当前产品。倒装焊封装设计复杂度较高,带来了更长的设计周期,增加了研发成本;加工步骤的增多,带来了生产成本的增加;先进的片内封装技术,例如 UBM、基板,都需要进行锡料焊接,虚焊等因素导致良率降低,并且测试排查手段只能通过 X 光进行观测,反馈迭代周期、成本都较长。

当决定采用倒装焊封装后,每个环节的衔接交互都需要格外谨慎,保障芯片最终达到设计目标。

责任编辑人:CC

4955

4955

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?