一、常用系统函数

- $rose(boolean expression or signal_name)

当信号/表达式由上一个时钟周期的‘0’变成当前周期的‘1’时返回真。

- $fell(boolean expression or signal_name)

当信号/表达式由上一个时钟周期的‘1’变成当前周期的‘0’返回真。

- $stable(boolean expression or signal_name)

当信号/表达式的值和上一个时钟周期相同返回真。

- $changed(boolean expression or signal_name)

当信号/表达式的值改变返回真。(=== ~$stable())

- $past(signal_name,number of clock cycles)

可以得到信号在几个时钟周期之前的值。在默认情况下,它提供信号在前一个时钟周期的值。

- $isunknown(expression)

检验表达式的任何位是否是X或者Z。

- $onehot(expression)

在任意给定的时钟沿,表达式只有一位为高。

safe_gnts = $onehot(gnt)

- $onehot0(expression)

在任意给定的时钟沿,表达式只有一位为高或者没有任何位为高。

safe_or_no_gnts = $onehot0(gnt)

- $countones(expression)

计数等于1的位。

num_gnts = $countones(gnt)

- $countbits(expression, val1, val2,...)

计数指定位的出现次数。

num_gnts = $countbits(gnt, 1'b1)

- expression inside list

当且仅当表达式在列表中返回真。

safe_opcode = opcode inside {ADD,SUB,MUL}二、在“时序逻辑”中判断多个序列/信号的行为关系

(1)表示序列间的关系:

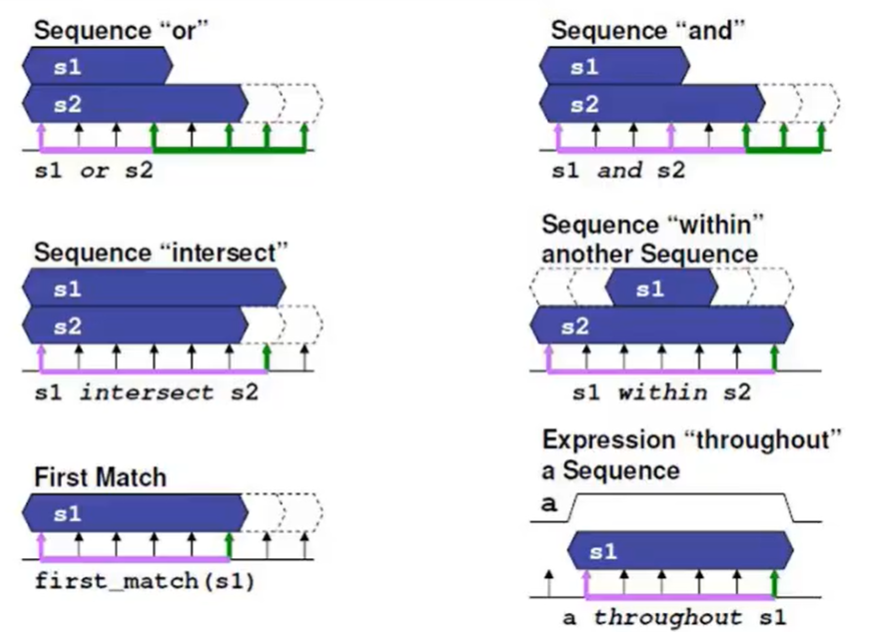

- s1 and s2: 当两个序列都成功时整个属性才成功。两个序列必须具有相同的起始点,但是可以有不同的结束点。检验的起始点是第一个序列的成功时的起始点,而检验的结束点是使得属性最终成功的另一个序列成功时的点。

- s1 or s2:只要其中一个序列成功,整个属性就成功。

- s1 intersect s2:断定两个序列在相同时刻开始,且结束于同一时刻。(两个序列的长度必须相等)

- s1 within s2:表示在s2的整个序列内出现过s1。

- s1 throughout s2:表示在s2整个序列内,s1一直成立。(蕴含只在时钟边沿检验前提条件一次,然后就开始检验后续算子部分,因此它不检测先行算子是否一直保持为真。为了保证某些条件在整个序列的验证过程中一直为真,可以使用“throughout”运算符。)

(2)延迟的用法:

- a ##2 b 断定a事件发生后2个单位时间内b事件一定会发生。

- a ##[1:3] b 断定a事件发生后1~3个单位时间内b事件一定会发生。

- a ##[1:$] b $表示无穷大。断定a事件发生后b事件一定会发生。

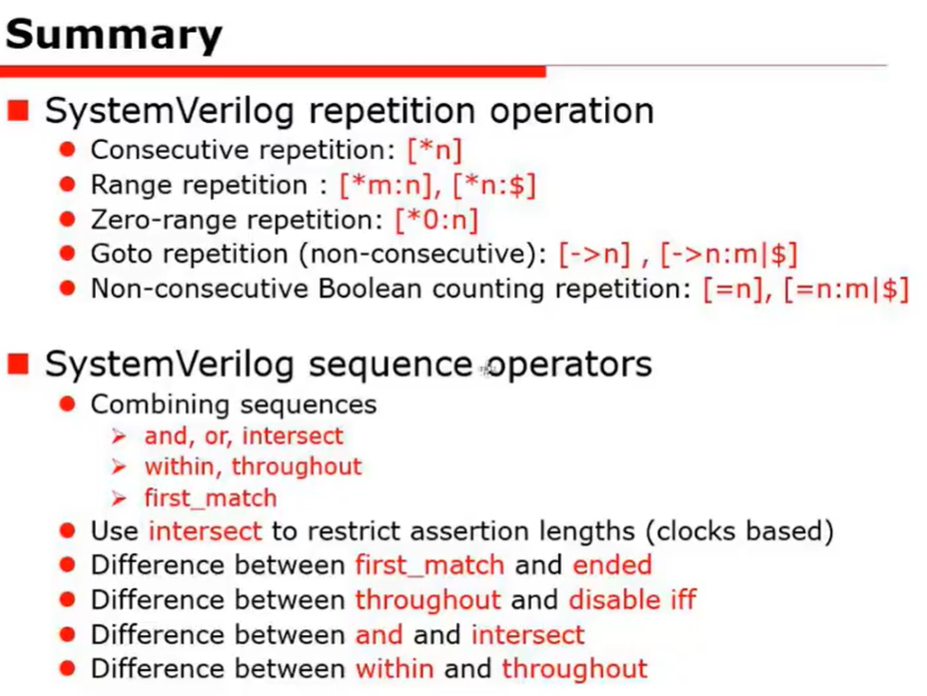

(3)重复运算符:

- 连续重复运算符:

a[*n]:信号a在连续n个时钟周期内都成立。

a[*n:m]:表示a连续出现n到m次,这里n,m为常数。

- 跟随重复运算符:

a[->3] a连续或间断地出现3次为高,在最后一个a结束的时间点。

- 非连续重复运算符:

a[=3]表示在信号a出现了3次之后的任意时间点。

非连续重复与跟随重复相似,除了它并不要求信号的最后一次重复匹配发生在整个序列匹配前的那个时钟周期。

(4)蕴含操作符:

蕴含等效于一个if-then结构。蕴含的左边叫作“先行算子”(antecedent),右边叫作“后续算子”(consequent)。先行算子是约束条件。当先行算子成功时,后续算子才会被计算。如果先行算子不成功,那么整个属性就默认地被认为成功。这叫作“空成功”(vacuous success)。蕴含结构只能被用在属性定义中,不能在序列中使用。

蕴含可以分为两类:交叠蕴含(Overlapped implication)和非交叠蕴含(Non-overlapped implication)。

- 交叠蕴含:

|->: s1 |-> s2 表示s1为真的同一时刻,s2必须为真,s1为假的时候,s2可真可假。

相当于:

if a

b;

else

succeed;

- 非交叠蕴含:

|=>: s1 |=> s2 表示在s1为真的下一个时钟周期s2必须为真,s1为假的下一个时钟周期,s2可真可假。

等价于:s1 |-> ##1 s2

(5)“disable iff”构造

在某些设计情况中,如果一些条件为真,则我们不想执行检验。换句话说,这就像是一个异步的复位,使得检验在当前时刻不工作。SVA提供了关键词“disable iff”来实现这种检验器的异步复位。

“disable iff”的基本语法如下:

disable iff(expression)<property definition0>

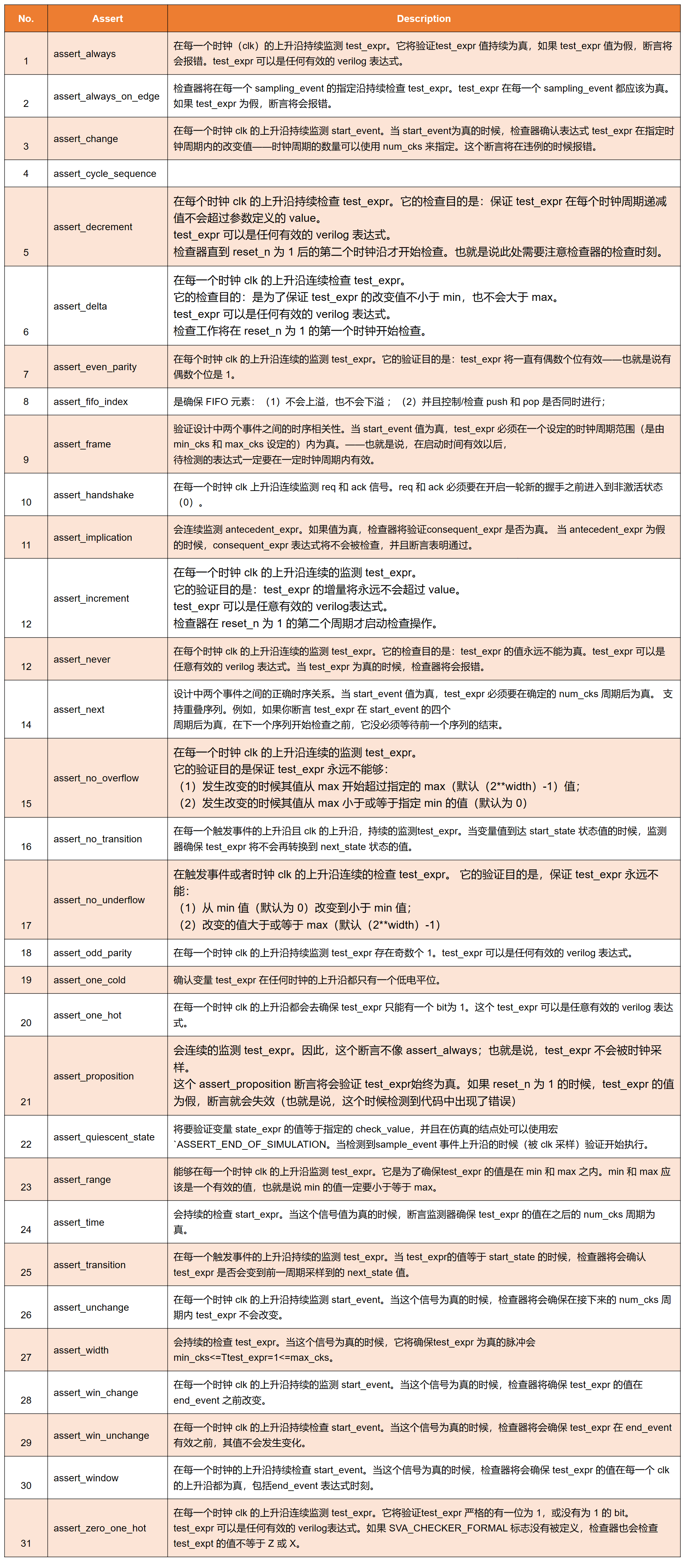

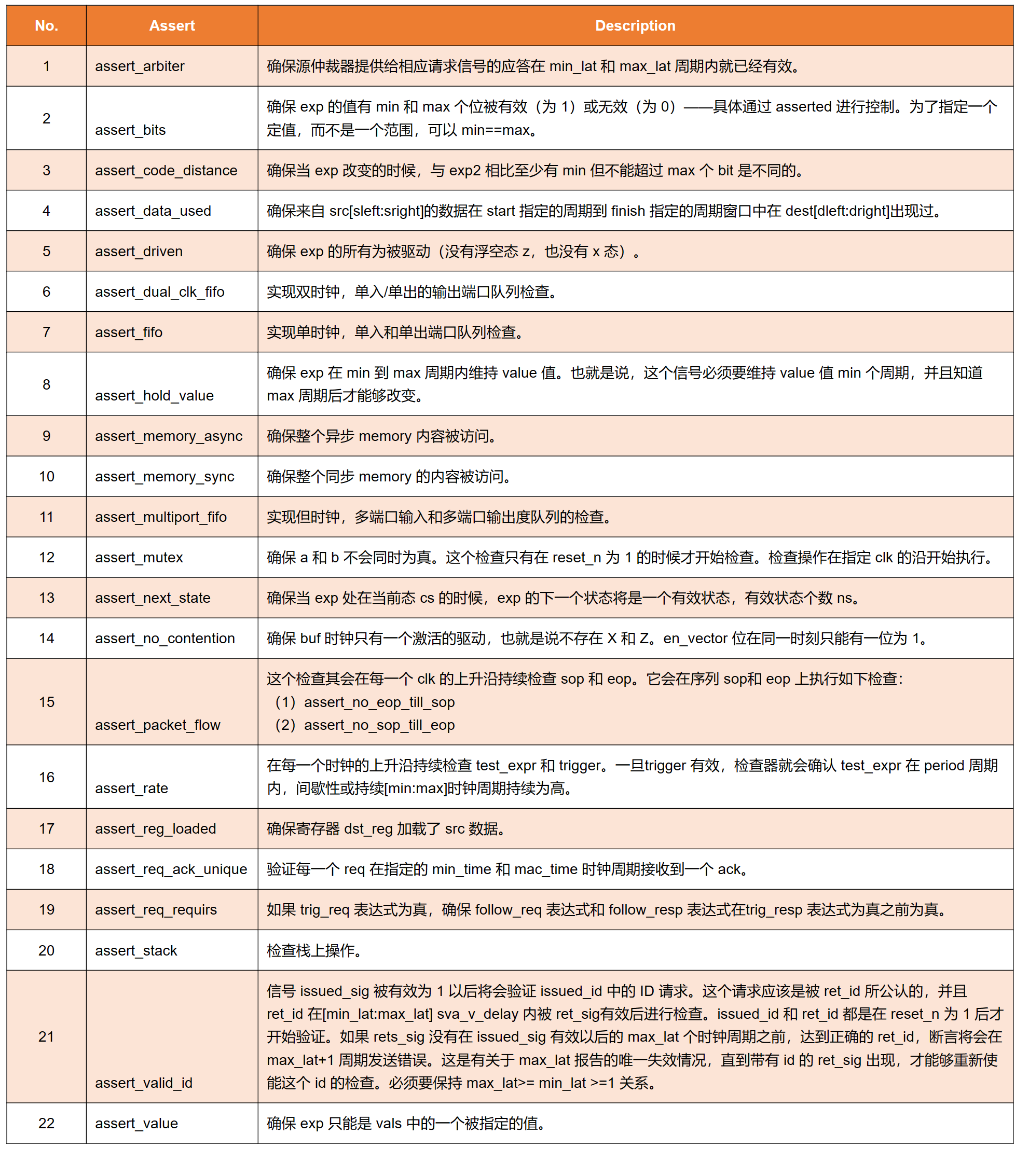

二、检查器

(1)检查器列表

(2)高级检查器

参考链接:

(64条消息) [SV]SystemVerilog 断言(SVA)检查器库(OVL)_ovl断言_元直数字电路验证的博客-CSDN博客

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?