描述

制作一个四选一的多路选择器,要求输出定义上为线网类型

状态转换:

d0 11

d1 10

d2 01

d3 00

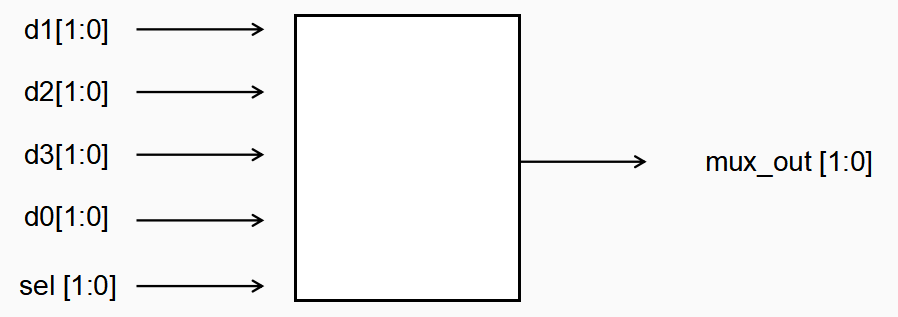

信号示意图:

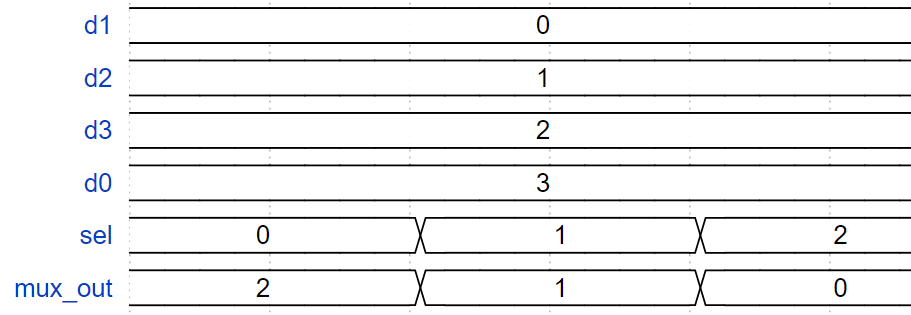

波形示意图:

输入描述:

输入信号 d1,d2,d3,d4 sel

类型 logic

输出描述:

输出信号 mux_out

类型 logic

解答:

问题分析:

输入四个值(d0,d1,d2,d3)加一个选项(sel),从四个中选择出一个结果作为输出(mux_out):

根据波形图:已知,d1=0;d2=1;d3=2;d0=3;且sel=0,mux_out=2;sel=1,mux_out=1;sel=2,mux_out=0;

观察可知,sel与四个输入值没有任何关系,于是观察状态转换,将转换值记为state,上面可变为:

为了便于观察则:

sel=0,state=d3,mux_out=d3=2;sel=1,tate=d2,mux_out=d2=1;sel=2,state=d1,mux_out=d1=0;

因为他输出与输出对齐的,所以为组合逻辑;

代码如下:

`timescale 1ns/1ns

module mux4_1(

input logic [1:0] d1,d2,d3,d0,

input logic [1:0] sel ,

output logic [1:0] mux_out

);

//*************code***********//

assign mux_out = (sel == 'd0) ? d3 : (sel == 'd1) ? d2 : (sel == 'd2) ? d1 :d0;

//*************code***********//

endmodule测试代码如下;

`timescale 1ns/1ns

module testbench();

logic clk=0;

always #5 clk = ~clk; // Create clock with period=10

logic [1:0]d1=0;

logic [1:0]d2=0;

logic [1:0]d3=0;

logic [1:0]d0=0;

logic [1:0]sel=0;

logic [1:0]mux_out;

initial begin

d1 <= 0;

d2 <= 1;

d3 <= 2;

d0 <= 3;

#10

sel <= 0;

#10

sel <= 1;

#10

sel <= 2;

#10

sel <= 3;

end

mux4_1 u1_mux4_1 (

.d0(d0),

.d1(d1),

.d2(d2),

.d3(d3),

.sel(sel),

.mux_out(mux_out)

);

endmodule

914

914

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?