笔记五是简单介绍DDS IP核的使用,它是可以产生任意频率正弦波的模块。此笔记同时输出波形和相位,一般可以不输出相位。

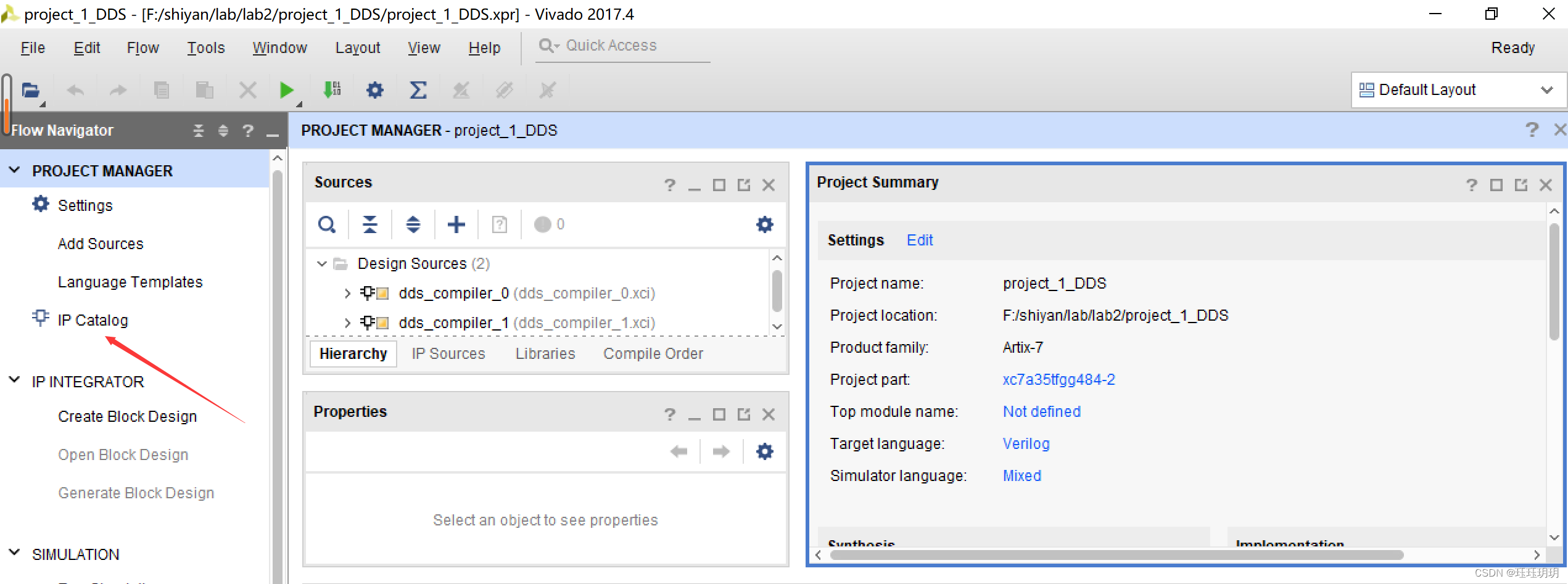

1. 打开VIVADO,点击IP Catalog

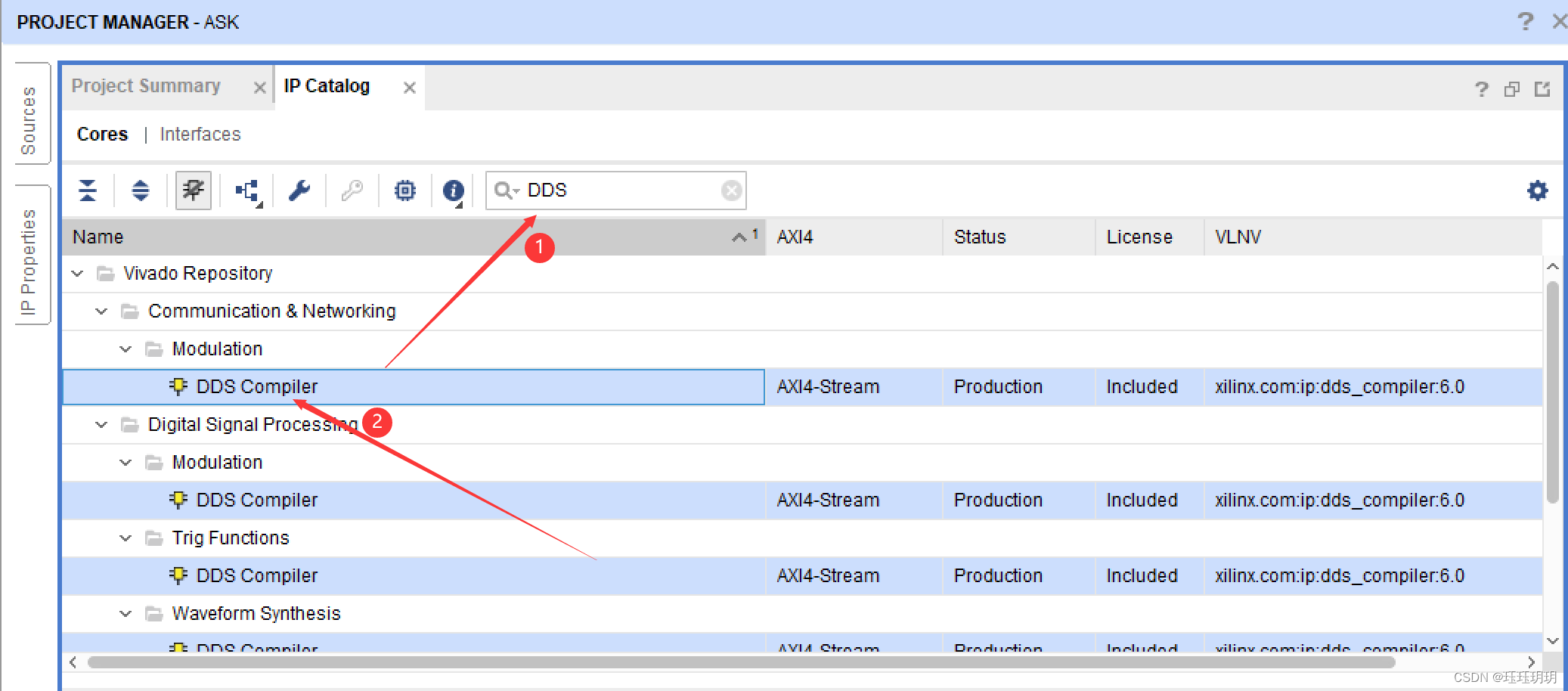

2.搜索DDS,选择DDS Compiler

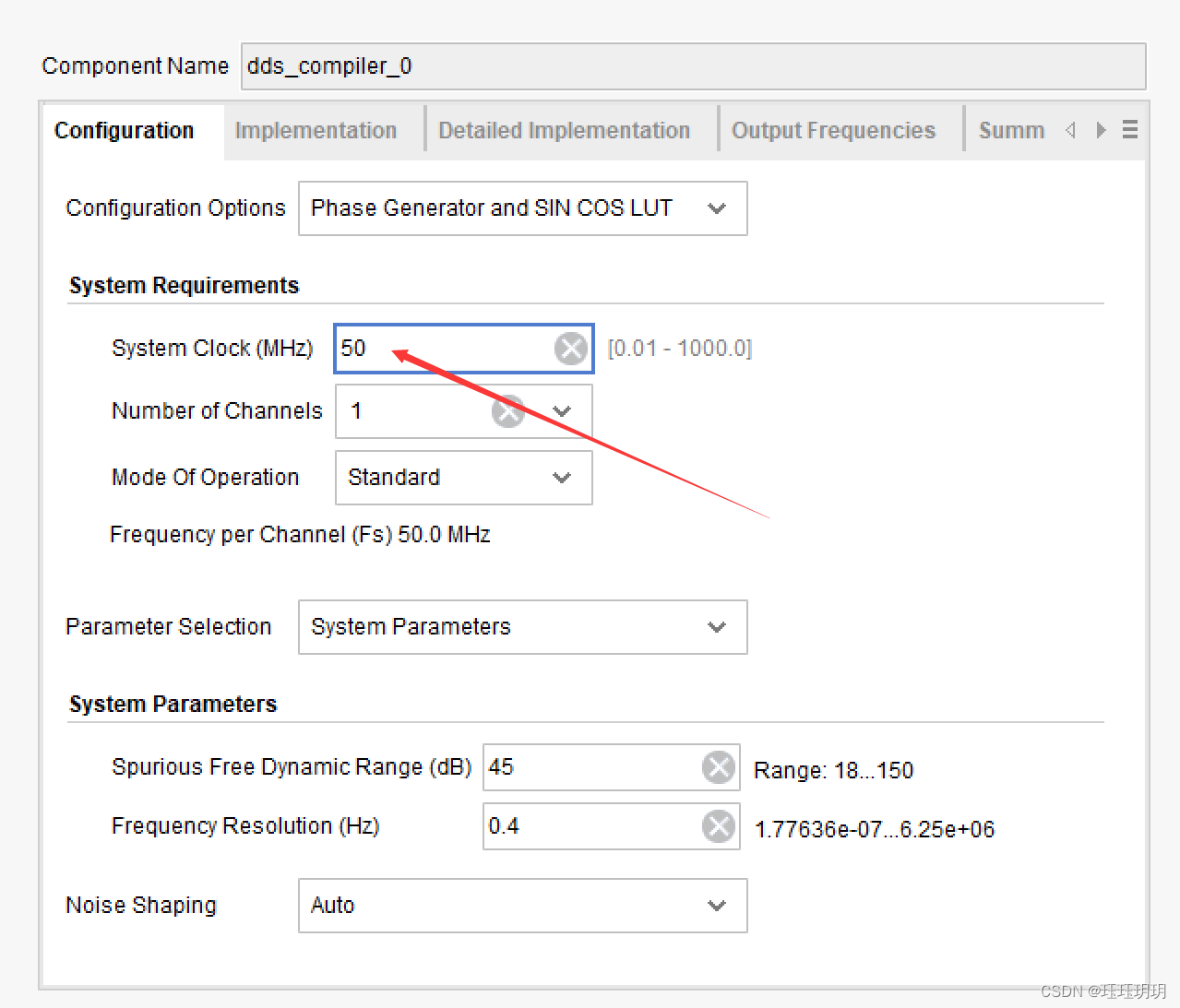

3. 配置参数

(1) 设置主频频率 50MHz

(2) 选择sine,并且勾选Has Phase Out(相位输出)

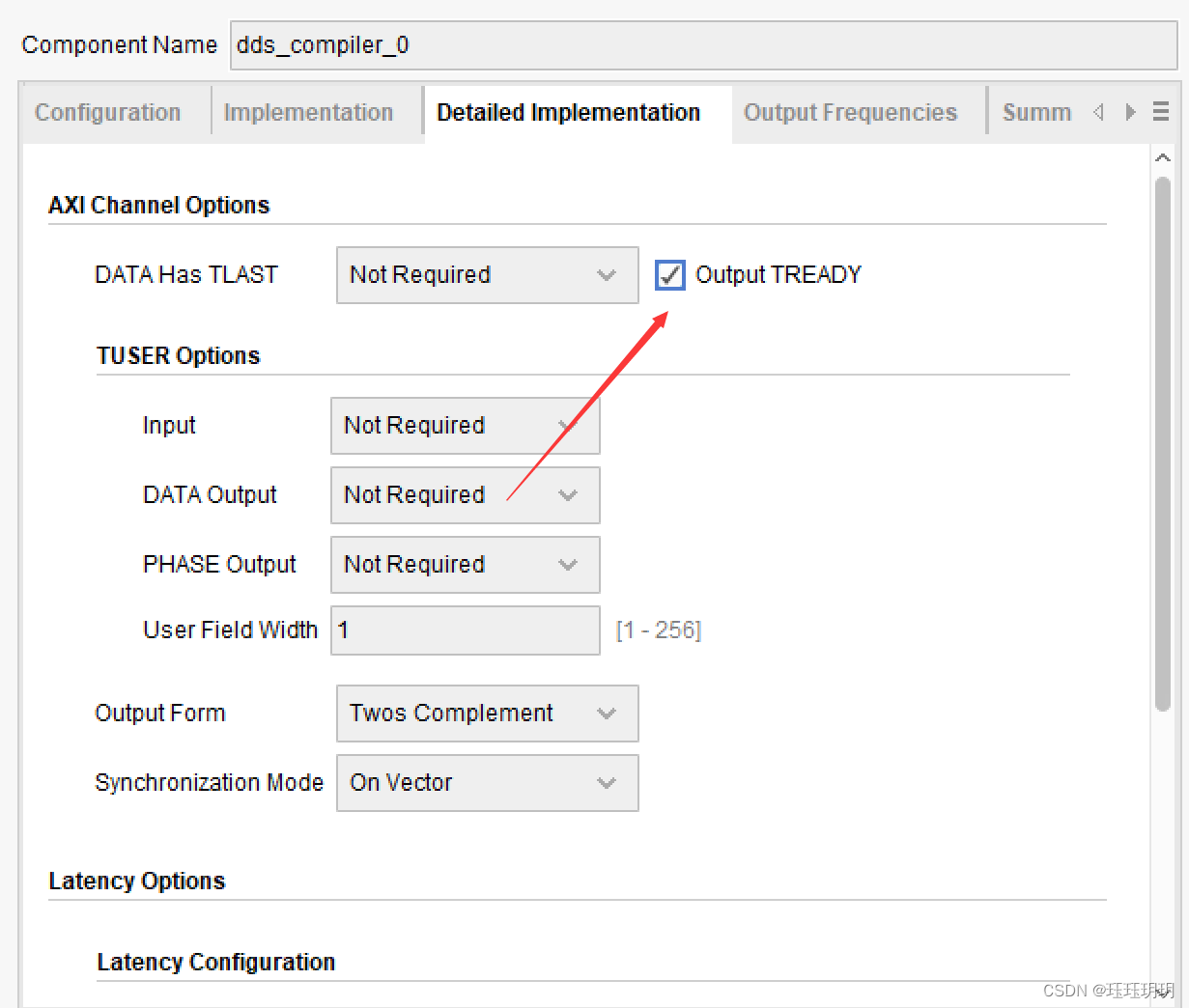

(3) 勾选Output TREDAY

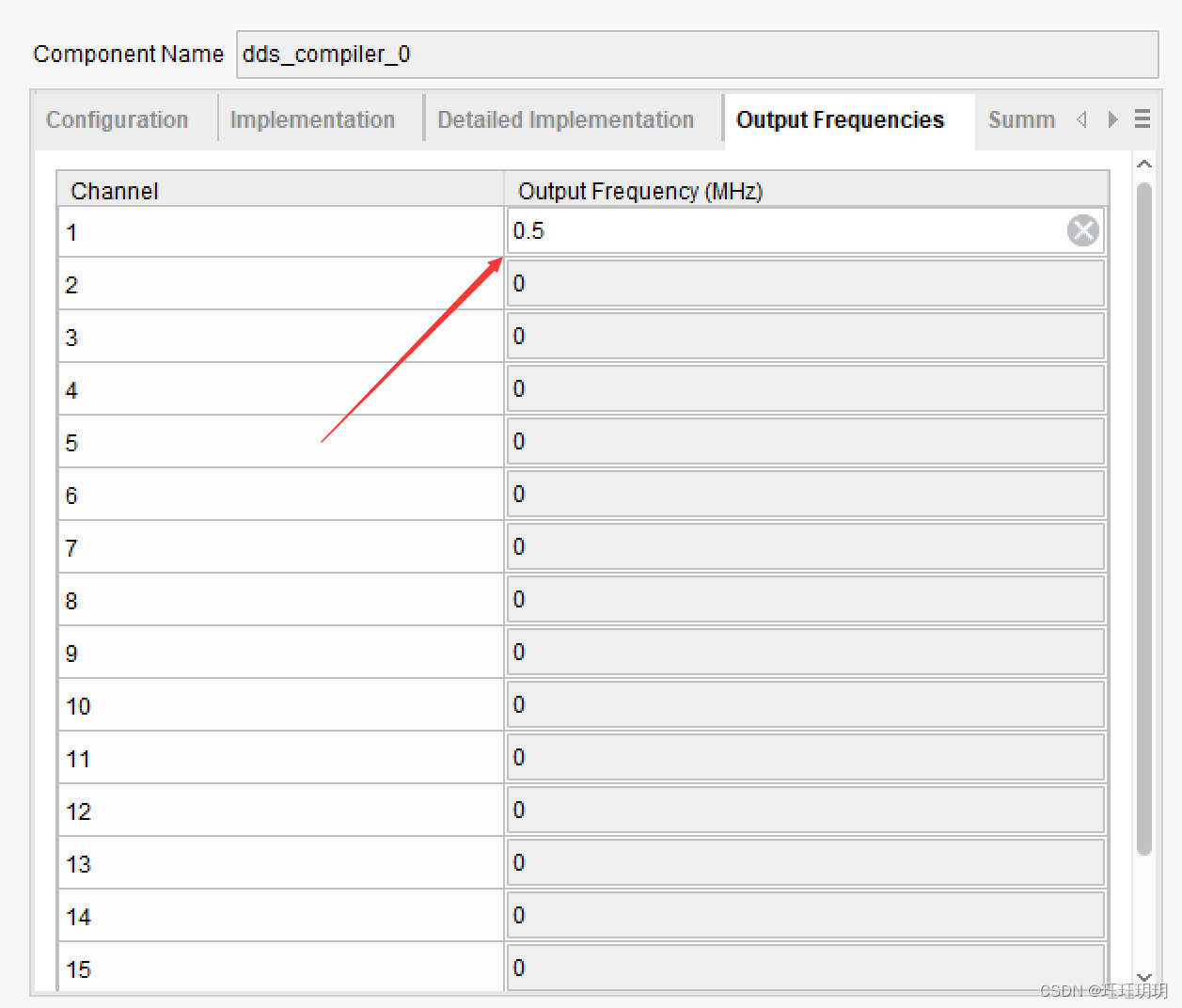

(4) 输入频率

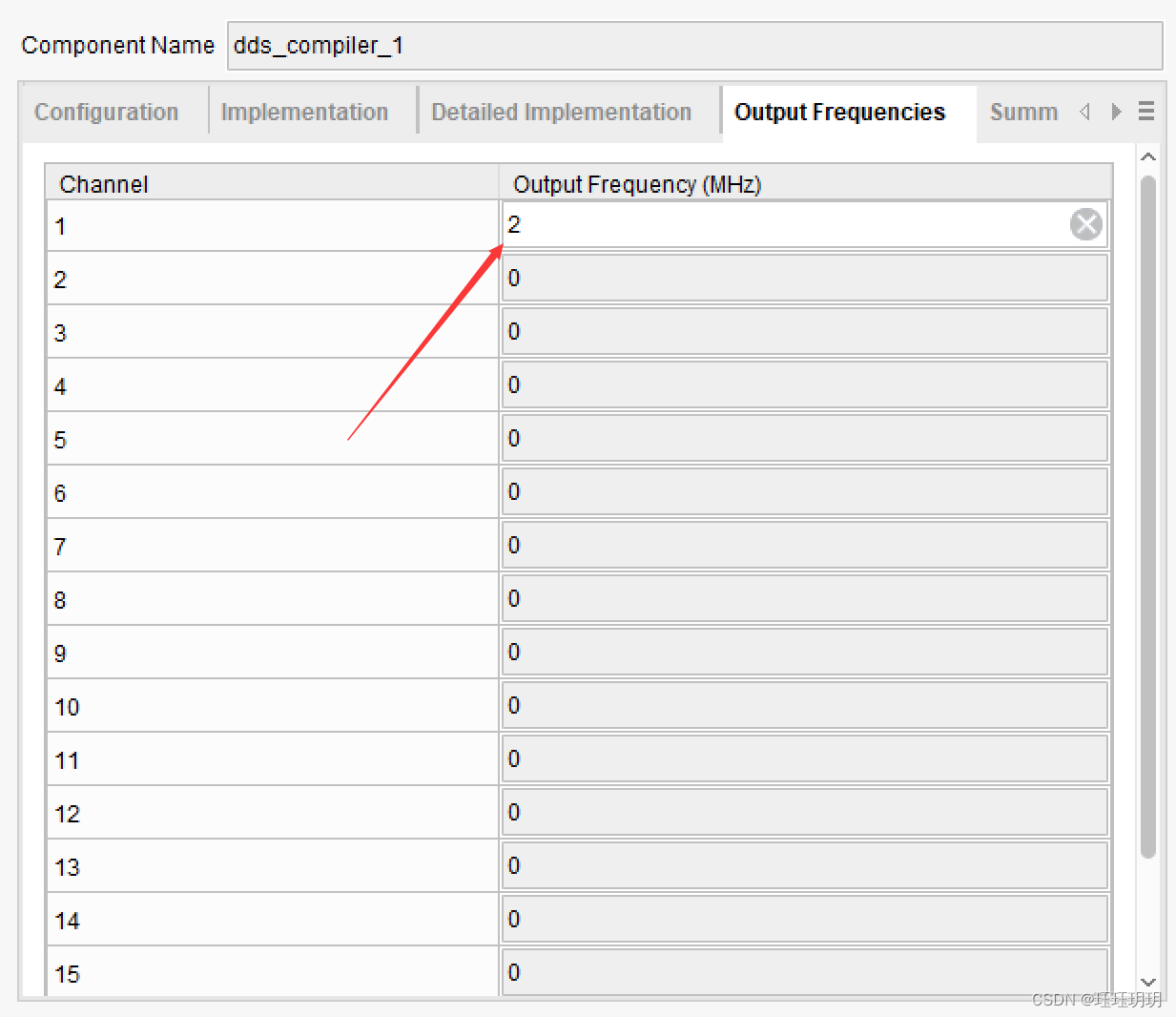

(5) 同上述步骤,再加一个DDS IP核

4. 测试文件

module tb_dds;

// 时钟clk

reg clk;

// 数据准备信号

reg m_axis_data_tready_1;

reg m_axis_data_tready_2;

// 相位准备信号

reg m_axis_phase_tready_1;

reg m_axis_phase_tready_2;

// 数据输出有效信号

wire m_axis_data_tvalid_1;

wire m_axis_data_tvalid_2;

// 相位输出有效信号

wire m_axis_phase_tvalid_1;

wire m_axis_phase_tvalid_2;

// 输出频率和相位

wire [31:0] dout_pha_1;

wire [7:0] dout_fre_1;

wire [31:0] dout_pha_2;

wire [7:0] dout_fre_2;

// 例化

dds_compiler_0 U1 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_1), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready_1), // input wire m_axis_data_tready

.m_axis_data_tdata(dout_fre_1), // output wire [7 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_1), // output wire m_axis_phase_tvalid

.m_axis_phase_tready(m_axis_phase_tready_1), // input wire m_axis_phase_tready

.m_axis_phase_tdata(dout_pha_1) // output wire [31 : 0] m_axis_phase_tdata

);

dds_compiler_1 U2 (

.aclk(clk), // input wire aclk

.m_axis_data_tvalid(m_axis_data_tvalid_2), // output wire m_axis_data_tvalid

.m_axis_data_tready(m_axis_data_tready_2), // input wire m_axis_data_tready

.m_axis_data_tdata(dout_fre_2), // output wire [7 : 0] m_axis_data_tdata

.m_axis_phase_tvalid(m_axis_phase_tvalid_2), // output wire m_axis_phase_tvalid

.m_axis_phase_tready(m_axis_phase_tready_2), // input wire m_axis_phase_tready

.m_axis_phase_tdata(dout_pha_2) // output wire [31 : 0] m_axis_phase_tdata

);

// 初始化

initial

begin

clk = 0; // 时钟clk为0

m_axis_data_tready_1 = 1; // 数据准备信号为1

m_axis_phase_tready_1 = 1; // 相位准备信号为1

m_axis_data_tready_2 = 1; // 数据准备信号为1

m_axis_phase_tready_2 = 1; // 相位准备信号为1

end

always #10 clk = ~clk; // clk周期为20ns

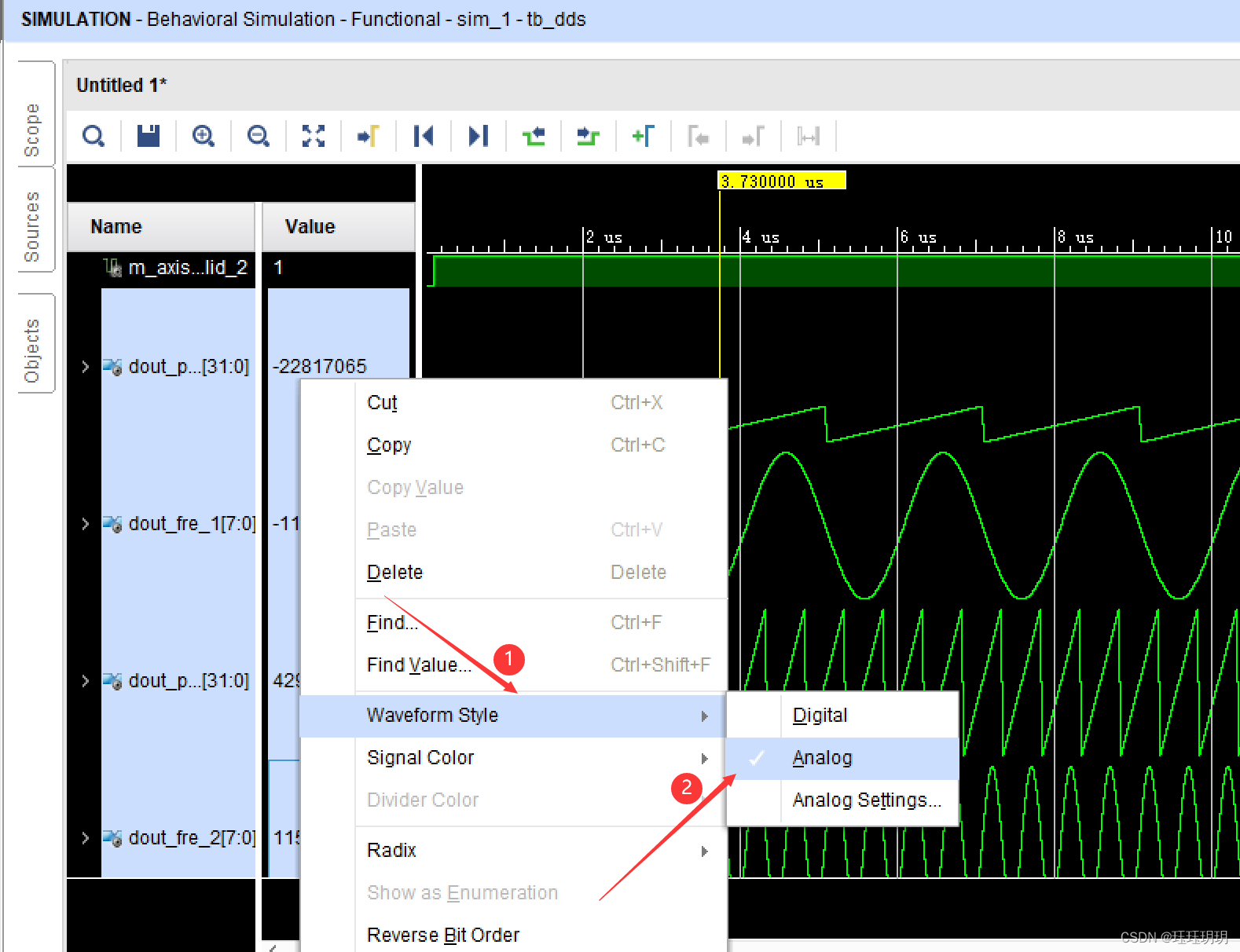

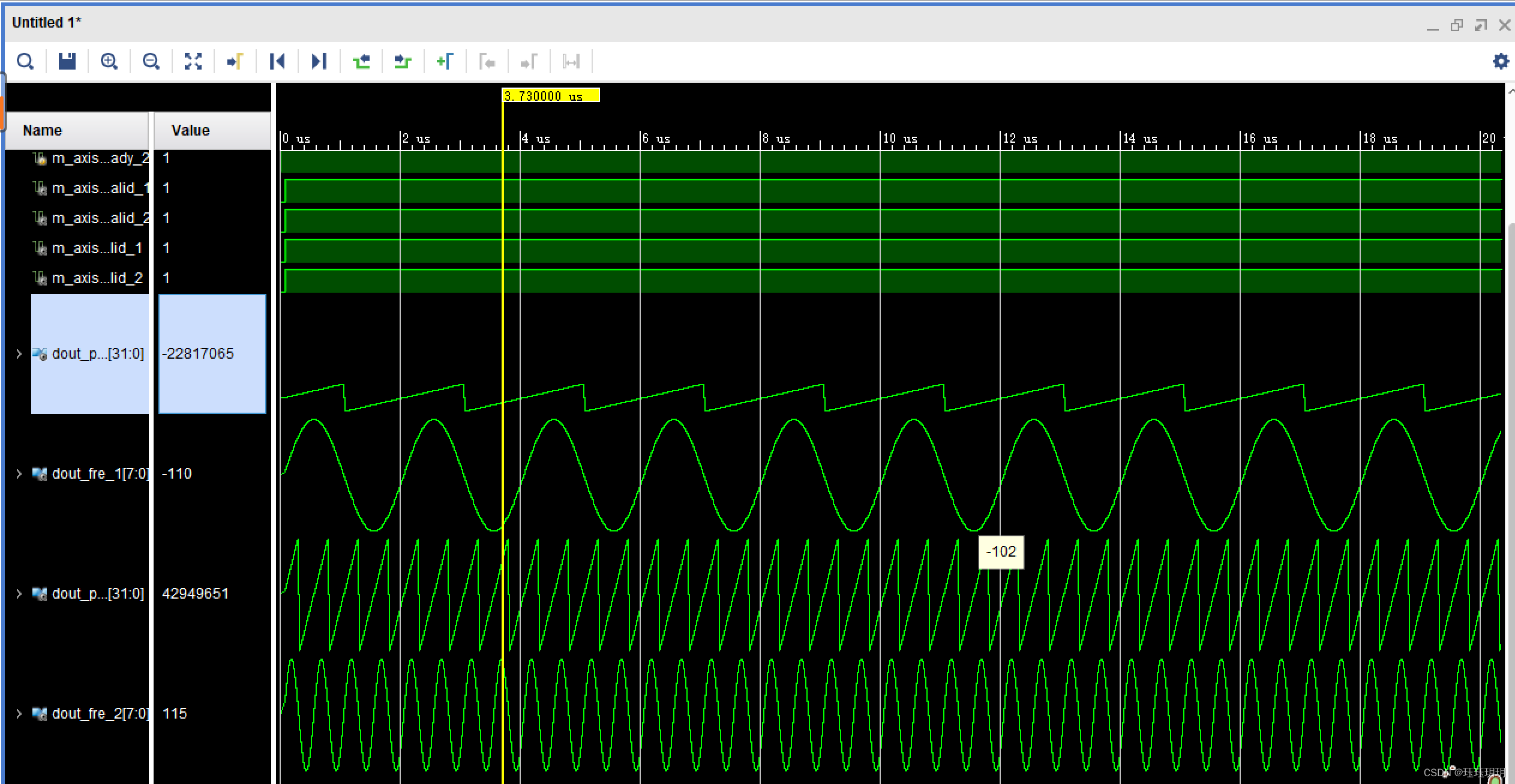

endmodule5. 结果展示

4341

4341

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?