module exa0609(

clock,red,amber,green

);

input clock;

output red,green,amber;

wire clock;

reg red,green,amber;

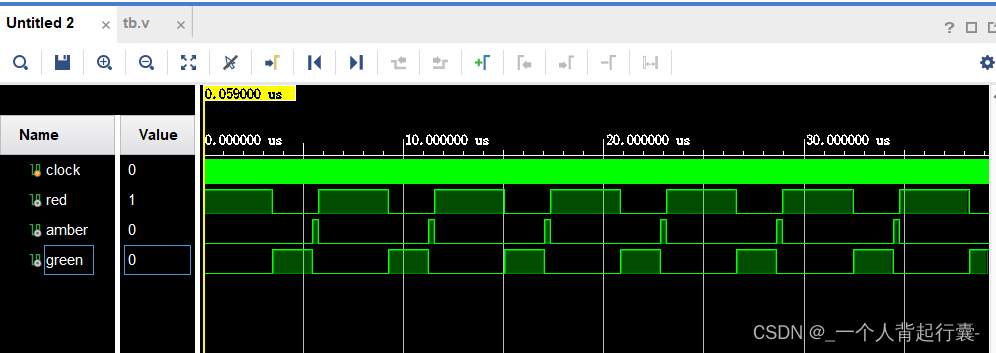

parameter on=1,off=0,red_tics=350,amber_tics=30,green_tics=200;

initial red=off;

initial amber=off;

initial green=off;

//交通灯控制时序

always

begin

red=on;

light(red,red_tics);

green=on;

light(green,green_tics);

amber=on;

light(amber,amber_tics);

end

task light;

output color;

input [31:0]tics;

begin

repeat(tics)

@(posedge clock)

color=off;

end

endtask

endmodule

module tb();

reg clock;

wire red,amber,green;

initial begin

clock=1'b1;

end

always #5 clock=~clock;

exa0609 uut(

.clock(clock),

.red(red),

.amber(amber),

.green(green)

);

endmodule

9660

9660

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?