首先创建一个工程项目,接着添加设计文件,然后进行编译、仿真和调试。具体步骤如下:

(1)在Windows资源管理器中,新建一个子目录

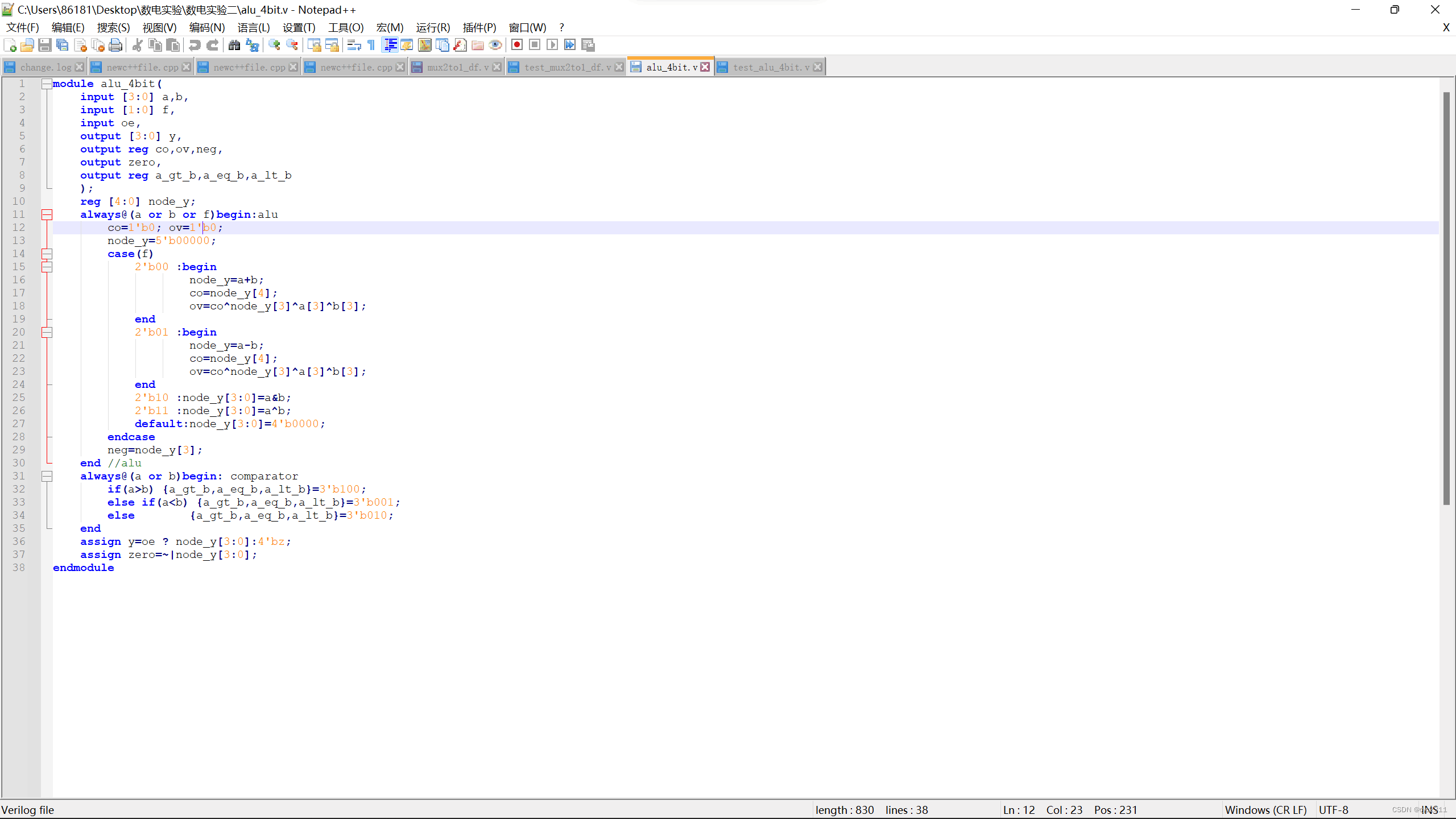

(2)打开一个文本编辑器(例如,Notepad++),输入设计块和激励块源代码,并将它们保存在新建的子日录中,文件名分别为alu_4bit.v 和test_alu_4bit.v, 如图

alu_4bit.v

test_alu_4bit.v

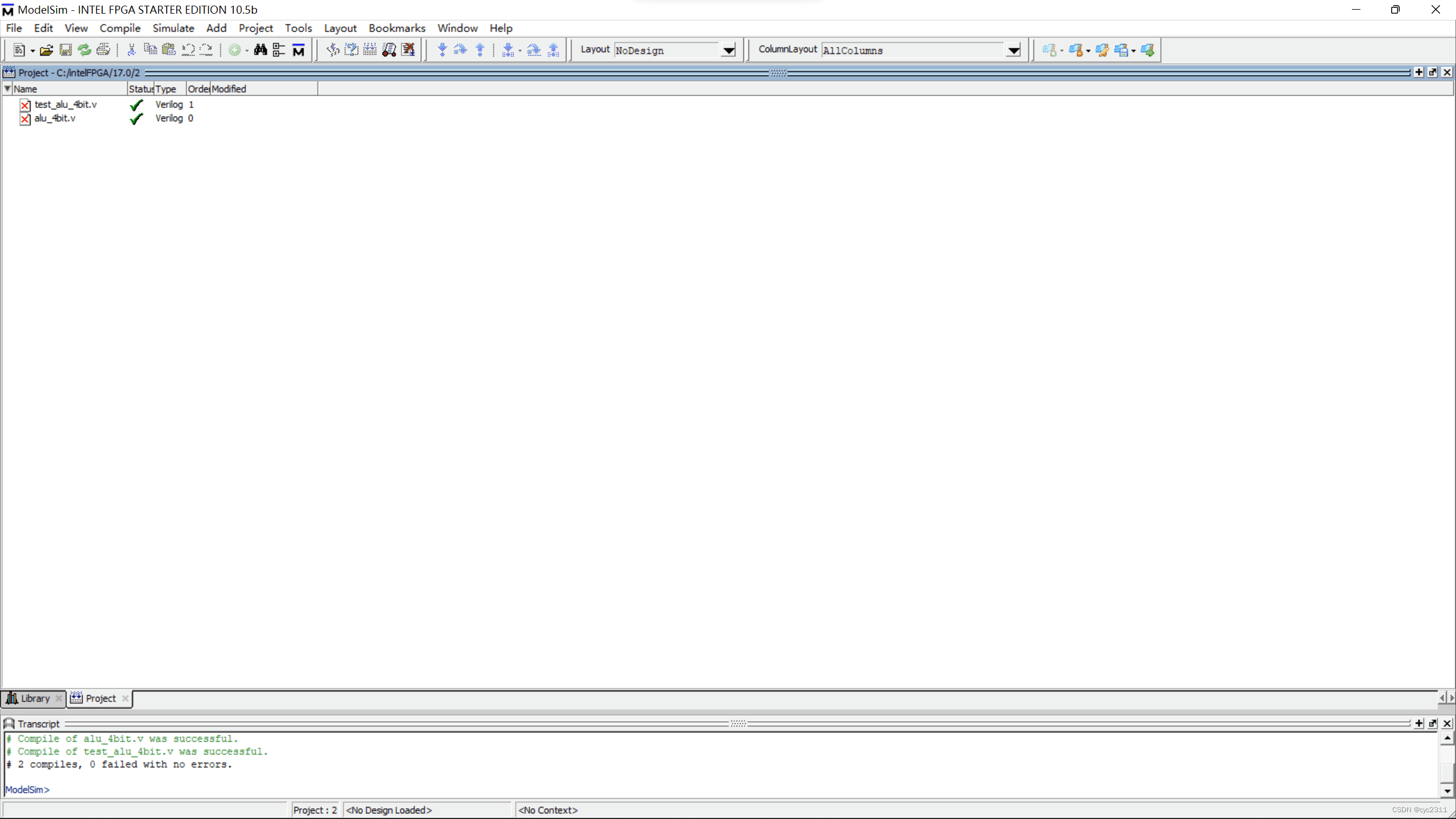

(3)打开ModelSim软件,创建一个新的工程设计项目( test_alu_4bit) ,添加已经存在的源文件(alu_4bit.v 和test_alu_4bit.v)。

(4)在Project子窗口中,编译所有的源文件。如果编泽成功,则代码文件的Status栏显示为绿色的“✓"。如果编译出错,则会给出相关错误信息,修改代码,然后再重新编译,直到没有编译错误,如图

(5)将设计载入仿真器,开始仿真。编译成功之后,仿真器通过调用VerilogHDL的顶层模块将设计载人到仿真器中,弹出与仿真相关的子窗口,且设置仿真时间从0时刻开始。

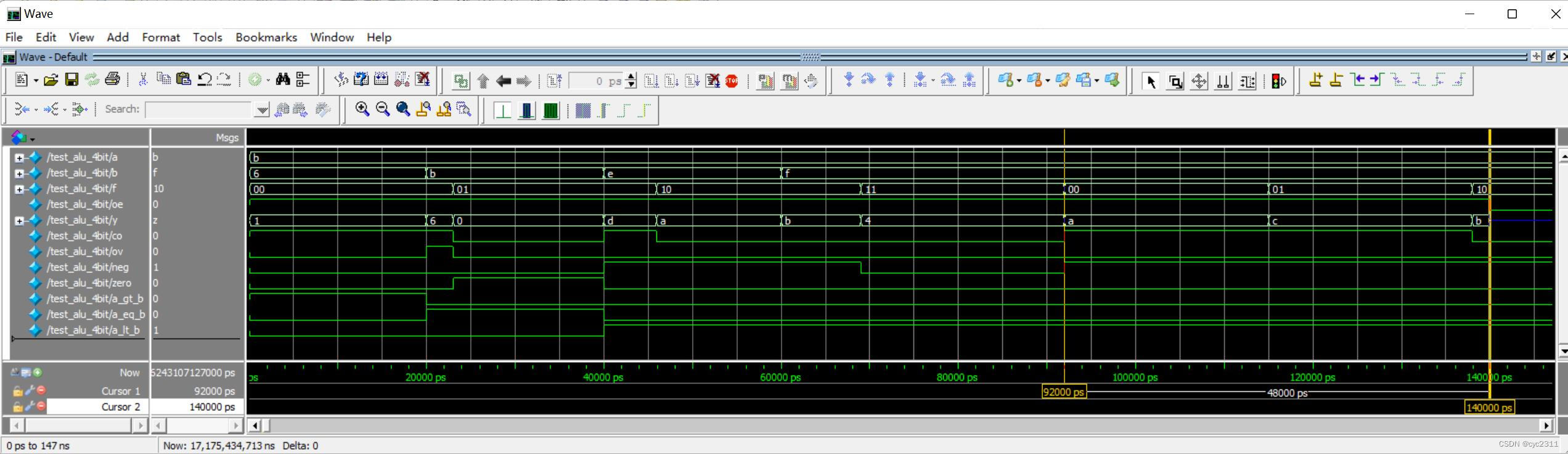

(6)将需要观察的信号添加到Wave子窗口中。把信号a,b,y右键找到Radix-Hexadecimal然后点击,信号f右键Radix-Symbolic点击,其余的都修改成Radix-Unsigned。

(7)执行仿真命令,得到如图所示的输入、输出波形;

(8)结束仿真,退出ModelSim仿真器。

视频实验链接

https://v.youku.com/v_show/id_XNTkxODYwNDgzNg==.html?x&sharefrom=android&sharekey=6c34060a41a855e068ba324bedc117939

密码:12345678A

450

450

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?