Verilog数字系统设计三

复杂组合逻辑实验1

前言

随着人工智能的不断发展,机器学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。以下是本篇文章正文内容,分别使用门级原语和always 语句设计8位数字比较器,如果输入A[7:0]小于等于输入B[7:0]则输出1,否则输出0,并写出测试代码进行测试。要求编制测试模块对实现的逻辑功能进行完整的测试。

一、8位比较器是什么?

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

二、编程

1.要求:

分别使用门级原语和always 语句设计8位数字比较器,如果输入A[7:0]小于等于输入B[7:0]则输出1,否则输出0,并写出测试代码进行测试。要求编制测试模块对实现的逻辑功能进行完整的测试;

2.assign语句实现:

assign代码如下:

//assign Eight digit comparison

module compare8 ( out,a,b);

output out;

input [7:0] a,b;

assign out = (a<b||a==b)?1:0;

endmodule

测试代码如下:

module compare8_tb();

reg [7:0] a_t;

reg [7:0] b_t;

wire out_t;

compare8 Compare8(

.out(out_t),

.a(a_t),

.b(b_t));

initial

begin

//a==b out=0

a_t=8'b00000000;

b_t=8'b00000000;

//a>b out=1

#20

a_t=8'b00100000;

b_t=8'b00010000;

//a<b out=1

#20

a_t=8'b00001000;

b_t=8'b00010000;

end

endmodule

3.always块实现:

always代码如下:

// always Eight digit comparison

module compare8_2 ( out,a,b);

output out;

reg out;

input [7:0] a,b;

always @(a or b)

if(a>b)

out=0;

else

out=1;

endmodule

测试代码如下:

module compare8_2tb();

reg [7:0] a_t;

reg [7:0] b_t;

wire out_t;

compare8_2 myCompare8_2(

.out(out_t),

.a(a_t),

.b(b_t));

initial

begin

//a=b out=1

a_t=8'b00000000;

b_t=8'b00000000;

//a>b out=0

#20

a_t=8'b00100000;

b_t=8'b00010000;

//a<b out=1

#20

a_t=8'b00001000;

b_t=8'b00010000;

//a=b out=1

#20

a_t=8'b00010000;

b_t=8'b00010000;

end

endmodule

4.门级原语实现:

always代码如下:

// always Eight digit comparison

module compare8_3(out,a,b);

input [7:0] a,b;

output out;

//a[7]=>a[0],b[7]=>b[0]

not u0(na0,a[0]);

and u1(rs0,na0,b[0]); //a[0]<b[0] *a<b

xnor u2(rs1,a[0],b[0]); //a[0]=b[0]

not u3(na1,a[1]);

and u4(rs2,na1,b[1]); //a[1]<b[1]

xnor u5(rs3,a[1],b[1]); //a[1]=b[1]

not u6(na2,a[2]);

and u7(rs4,na2,b[2]); //a[2]<b[2]

xnor u8(rs5,a[2],b[2]); //a[2]=b[2]

not u9(na3,a[3]);

and u10(rs6,na3,b[3]); //a[3]<b[3]

xnor u11(rs7,a[3],b[3]); //a[3]=b[3]

not u12(na4,a[4]);

and u13(rs8,na4,b[4]); //a[4]<b[4]

xnor u14(rs9,a[4],b[4]); //a[4]=b[4]

not u15(na5,a[5]);

and u16(rs10,na5,b[5]); //a[5]<b[5]

xnor u17(rs11,a[5],b[5]); //a[5]=b[5]

not u18(na6,a[6]);

and u19(rs12,na6,b[6]); //a[6]<b[6]

xnor u20(rs13,a[6],b[6]); //a[6]=b[6]

not u21(na7,a[7]);

and u22(rs14,na7,b[7]); //a[7]<b[7]

xnor u23(rs15,a[7],b[7]); //a[7]=b[7]

and u24(rs16,rs15,rs12);//a<b

and u25(rs17,rs15,rs13,rs10);//a<b

and u26(rs18,rs15,rs13,rs11,rs8);//a<b

and u27(rs19,rs15,rs13,rs11,rs9,rs6);//a<b

and u28(rs20,rs15,rs13,rs11,rs9,rs7,rs4);//a<b

and u29(rs21,rs15,rs13,rs11,rs9,rs7,rs5,rs2);//a<b

and u30(rs22,rs15,rs13,rs11,rs9,rs7,rs5,rs3,rs0);//a<b

and u31(rs23,rs15,rs13,rs11,rs9,rs7,rs5,rs3,rs1);//a=b

or u32(out,rs14,rs16,rs17,rs18,rs19,rs20,rs21,rs22,rs23);

endmodule

测试代码如下:

module compare8_3tb();

reg [7:0] a_t;

reg [7:0] b_t;

wire out_t;

compare8_3 myCompare8_3(

.out(out_t),

.a(a_t),

.b(b_t));

initial

begin

//a=b out=1

a_t=8'b00000000;

b_t=8'b00000000;

//a>b out=0

#20

a_t=8'b00100000;

b_t=8'b00010000;

//a<b out=1

#20

a_t=8'b00001000;

b_t=8'b00010000;

//a=b out=1

#20

a_t=8'b00010000;

b_t=8'b00010000;

end

endmodule

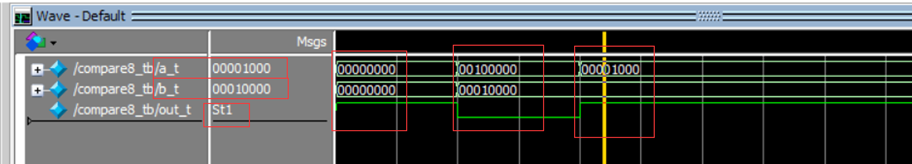

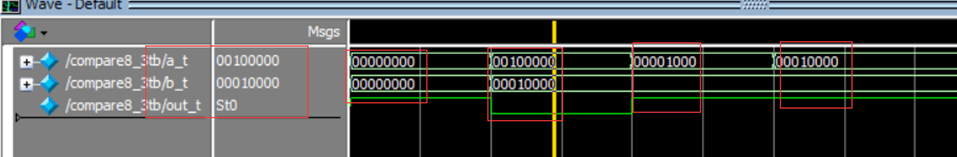

5.仿真波形

测试结果如下:

仿真波形:

总结

提示:

以上就是今天要分享的内容,本文仅仅简单介绍了Verilog使用always块、连续赋值assign和门级原语的方法完成8位比较器功能。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?