若对你有用,记得点赞、关注我哦!

若对你有用,记得点赞、关注我哦!

B站同名up猪,欢迎关注我的账号鸽子不二的个人空间-鸽子不二个人主页-哔哩哔哩视频哔哩哔哩鸽子不二的个人空间,提供鸽子不二分享的视频、音频、文章、动态、收藏等内容,关注鸽子不二账号,第一时间了解UP主动态。 https://space.bilibili.com/204913846博客总领目录请看这篇,不看后悔

https://space.bilibili.com/204913846博客总领目录请看这篇,不看后悔

软件工程专业大学四年学什么_大学近代史学分是多少-CSDN博客 https://blog.csdn.net/qq_41587612/article/details/104362661

https://blog.csdn.net/qq_41587612/article/details/104362661

1. 实验题目

八位比较器的设计与仿真

2. 实验目的

设计一个字节(8 位)的比较器,并进行仿真测试。

3. 实验要求

比较两个一字节数据 a[7:0],b[7:0]的大小,如a[7:0]大于b[7:0],则输出1,否则输出 0。

4.程序代码

Verilog代码:

module compare(a,b,out);

input [7:0] a,b;

output out;

assign out=(a[7:0]>b[7:0])?1:0;

endmodule

仿真代码:

`timescale 1ns/1ns

`include "./compare.v"

module comparetest;

reg[7:0] a,b;

wire equal;

initial

begin

a='b00000000;

b='b00000000;

#100 a='b00000000;b='b00000001;

#100 a='b00010001;b='b00000011;

#100 a='b00000001;b='b00000010;

#100 a=100;b=99;

#100 a=123;b=125;

#100 a=135;b=130;

#100 a=245;b=246;

#100 $stop;

end

compare compare(.out(out),.a(a),.b(b));

endmodule5. 实验结果

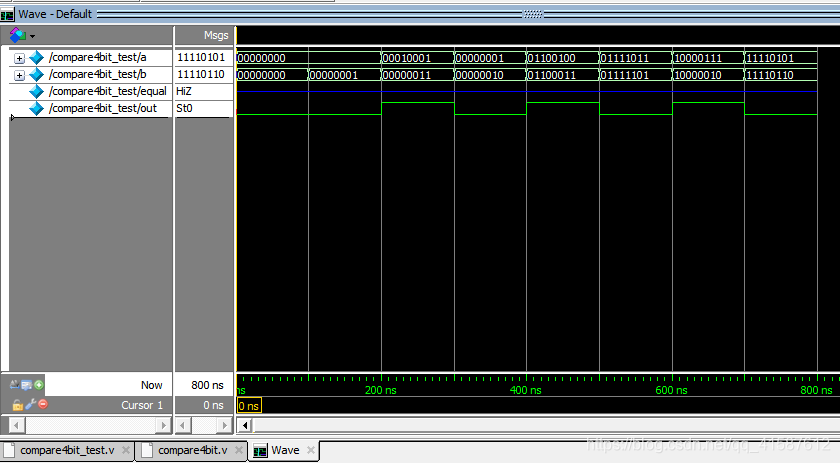

本实验比较两个一字节数据a[7:0],b[7:0]的大小,根据本题波形分析,每隔100个时间单位后a与b重新赋值进行比较,第一段波形中a=b=000000二者相等,输出的out值为1,100个时间单位后b的值变为1,此时b>a,a与b不等,输出out值为0,后面给定的多组测试数据以此类推。

5292

5292

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?