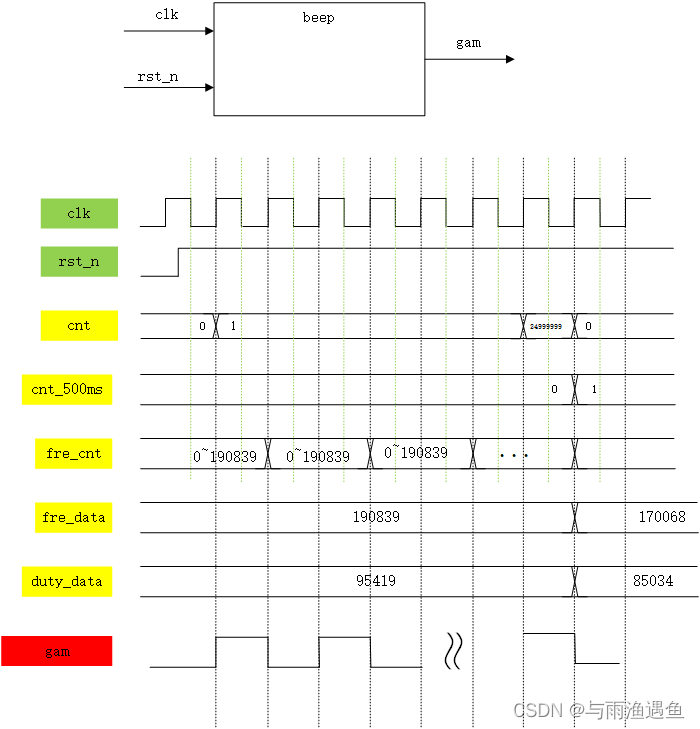

蜂鸣器

框图

代码

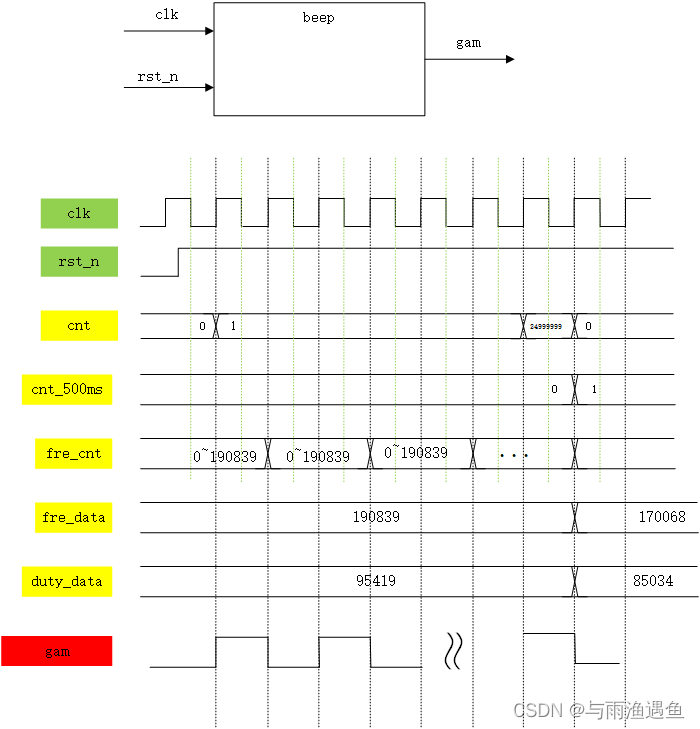

module beep

#(

parameter CNT_MAX = 32'd24999999,

parameter DO_MAX = 32'd190839,

parameter RI_MAX = 32'd170067,

parameter MI_MAX = 32'd151514,

parameter FA_MAX = 32'd143265,

parameter SO_MAX = 32'd127551,

parameter LA_MAX = 32'd113636,

parameter SI_MAX = 32'd101214,

parameter DO_DUTY = 32'd95419,

parameter RI_DUTY = 32'd85033,

parameter MI_DUTY = 32'd75756,

parameter FA_DUTY = 32'd71632,

parameter SO_DUTY = 32'd63774,

parameter LA_DUTY = 32'd56817,

parameter SI_DUTY = 32'd50606

)(

input wire clk,

input wire rst_n,

output reg gam

);

// parameter CNT_MAX = 32'd24999999;

// parameter DO_MAX = 32'd190839;

// parameter RI_MAX = 32'd170067;

// parameter MI_MAX = 32'd151514;

// parameter FA_MAX = 32'd143265;

// parameter SO_MAX = 32'd127551;

// parameter LA_MAX = 32'd113636;

// parameter SI_MAX = 32'd101214;

// parameter DO_DUTY = 32'd95419;

// parameter RI_DUTY = 32'd85033;

// parameter MI_DUTY = 32'd75756;

// parameter FA_DUTY = 32'd71632;

// parameter SO_DUTY = 32'd63774;

// parameter LA_DUTY = 32'd56817;

// parameter SI_DUTY = 32'd50606;

reg [31:0]cnt;

reg [2:0]cnt_500ms;

reg [31:0]fre_cnt;

reg [31:0]fre_data;

reg [31:0]duty_data;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt <= 32'd0;

end

else if (cnt == CNT_MAX) begin

cnt <= 32'd0;

end

else begin

cnt <= cnt + 32'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt_500ms <= 3'd0;

end

else if (cnt_500ms == 3'd6 && cnt == CNT_MAX) begin

cnt_500ms <= 3'd0;

end

else if (cnt == CNT_MAX) begin

cnt_500ms <= cnt_500ms + 3'd1;

end

else begin

cnt_500ms <= cnt_500ms;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

fre_cnt <= 32'd0;

end

else if (fre_cnt == fre_data || cnt == CNT_MAX) begin

fre_cnt <= 32'd0;

end

else begin

fre_cnt <= fre_cnt + 32'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

duty_data <= 32'd0;

end

else case (cnt_500ms)

0 : duty_data <= DO_DUTY;

1 : duty_data <= DO_DUTY;

2 : duty_data <= MI_DUTY;

3 : duty_data <= FA_DUTY;

4 : duty_data <= SO_DUTY;

5 : duty_data <= LA_DUTY;

6 : duty_data <= SI_DUTY;

default: duty_data <= DO_MAX;

endcase

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

fre_data <= 32'd0;

end

else case (cnt_500ms)

0 : fre_data <= DO_MAX;

1 : fre_data <= DO_MAX;

2 : fre_data <= MI_MAX;

3 : fre_data <= FA_MAX;

4 : fre_data <= SO_MAX;

5 : fre_data <= LA_MAX;

6 : fre_data <= SI_MAX;

default: fre_data <= DO_MAX;

endcase

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

gam <= 1'b0;

end

else if (cnt == CNT_MAX) begin

gam <= 1'b0;

end

else if (fre_cnt == fre_data || fre_cnt == duty_data) begin

gam <= ~gam;

end

else begin

gam <= gam;

end

end

endmodule

3631

3631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?