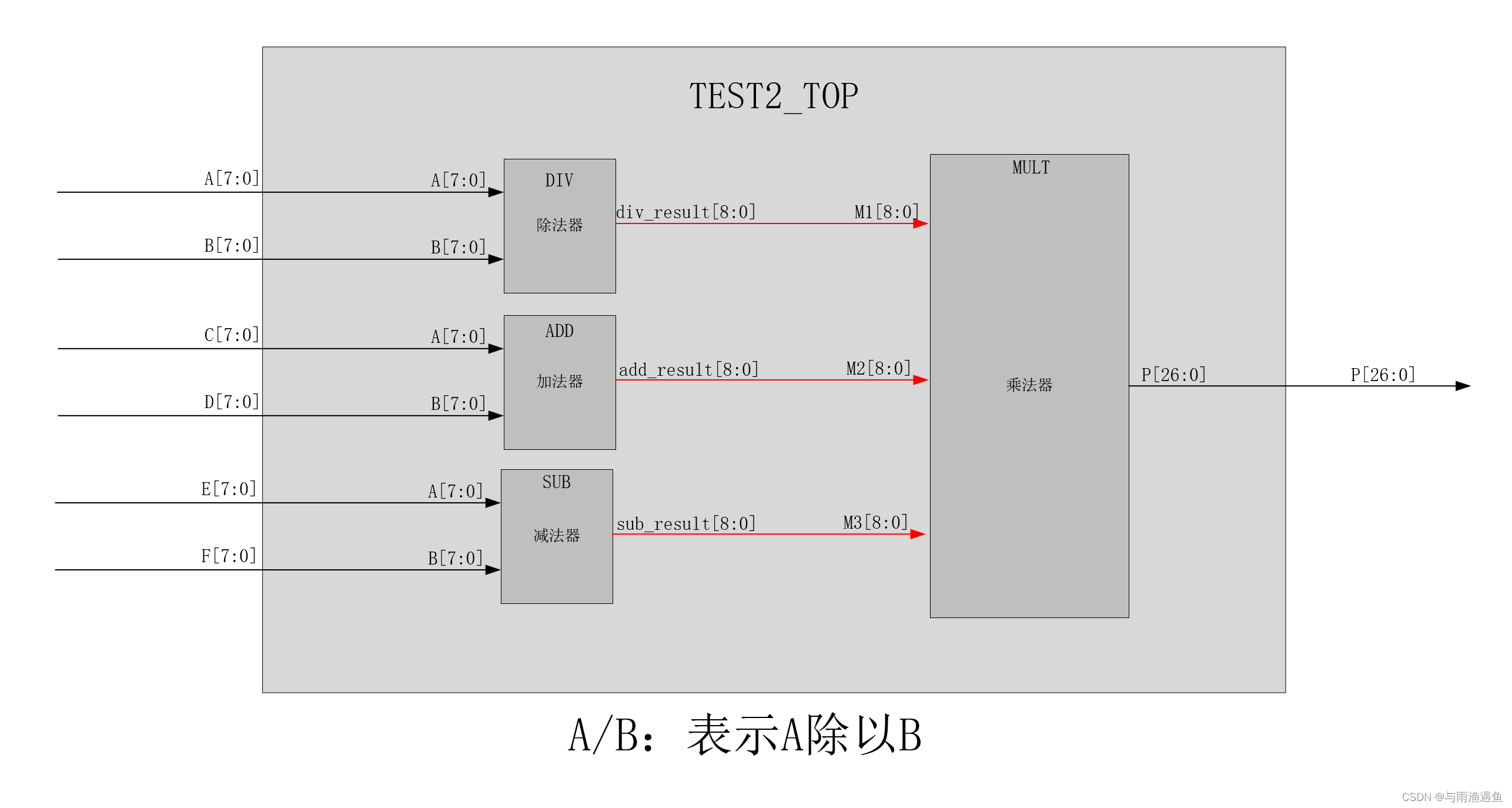

层次化设计(例2)

设计目标:实现P = (A/B)*(C+D)*(E-F)

框图

代码

顶层代码TEST2_TOP

module TEST2_TOP (

input wire [7:0]A,

input wire [7:0]B,

input wire [7:0]C,

input wire [7:0]D,

input wire [7:0]E,

input wire [7:0]F,

output wire [26:0]P

);

wire [8:0]div_result;

wire [8:0]add_result;

wire [8:0]sub_result;

ADD ADD_1(

.A(C),

.B(D),

.add_result(add_result)

);

SUB SUB_1(

.A(E),

.B(F),

.sub_result(sub_result)

);

DIV DIV_1(

.A(A),

.B(B),

.div_result(div_result)

);

MULT MULT_1(

.M1(div_result),

.M2(add_result),

.M3(sub_result),

.P(P)

);

endmodule

DIV模块

module DIV (

input wire [7:0]A,

input wire [7:0]B,

output wire [8:0] div_result

);

assign div_result = A / B;

endmodule

ADD模块

module ADD (

input wire [7:0]A,

input wire [7:0]B,

output wire [8:0] add_result

);

assign add_result = A + B;

endmodule

SUB模块

module SUB (

input wire [7:0]A,

input wire [7:0]B,

output wire [8:0] sub_result

);

assign sub_result = A - B;

endmodule

MULT模块

module MULT (

input wire [8:0]M1,

input wire [8:0]M2,

input wire [8:0]M3,

output wire [26:0] P

);

assign P = M1 * M2 * M3;

endmodule

tb文件

`timescale 1ns/1ps

module TEST2_TOP_tb ();

reg [7:0]A;

reg [7:0]B;

reg [7:0]C;

reg [7:0]D;

reg [7:0]E;

reg [7:0]F;

wire [26:0]P;

initial begin

A = 8'd1;

B = 8'd1;

C = 8'd1;

D = 8'd1;

E = 8'd1;

F = 8'd1;

end

always #10 A = {$random} % 256;

always #10 B = {$random} % 256;

always #10 C = {$random} % 256;

always #10 D = {$random} % 256;

always #10 E = {$random} % 256;

always #10 F = {$random} % 256;

TEST2_TOP TEST2_TOP_1(

.A(A),

.B(B),

.C(C),

.D(D),

.E(E),

.F(F),

.P(P)

);

endmodule

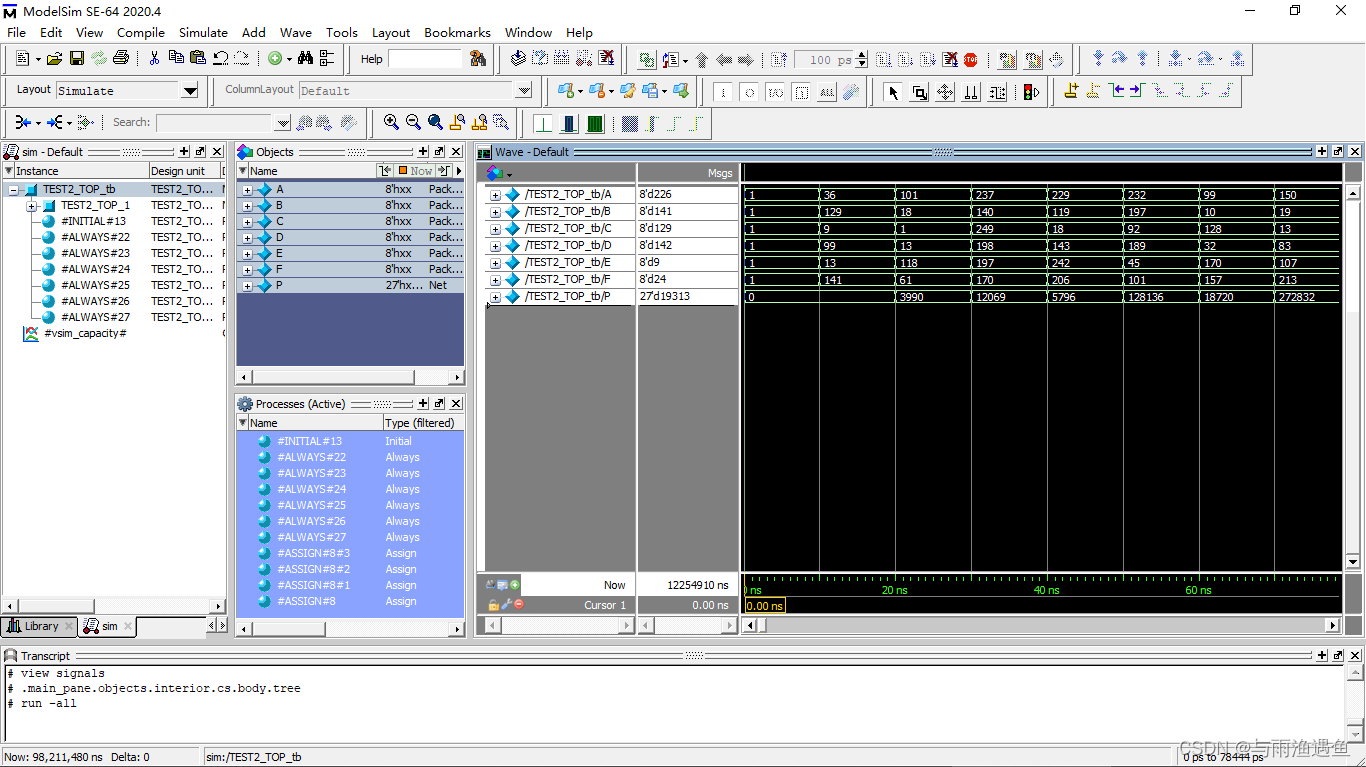

仿真结果

3439

3439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?