IP核——锁相环PLL

设计目标:

1:调用锁相环IP核,产生200Mhz的时钟,要求使用这个200Mhz的时钟,编写闪光灯模块(1个LED灯1秒亮灭循环),使用Signaltap II 抓取闪光灯模块的计数器和LED输出

2:调用锁相环IP核,产生125Mhz的时钟,要求使用这个125Mhz/200Mhz的时钟,编写流水灯模块(4个LED灯500ms流水显示),使用Signaltap II 抓取流水灯模块的计数器和LED输出

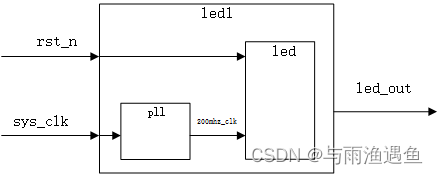

闪光灯

框图

代码

pll.v

module pll (

input wire sys_clk,

output wire clk_mul_4,

output wire locked

);

ip_pll ip_pll_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_4 ),

.locked ( locked )

);

endmodule

led.v

module led (

input wire clk,

input wire rst_n,

output reg led_out

);

reg [26:0]cnt;

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt <= 0;

end

else if (cnt == 199_999_999) begin

cnt <= 27'd0;

end

else begin

cnt <= cnt + 27'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

led_out <= 1'b0;

end

else if (cnt == 199_999_999) begin

led_out <= ~led_out;

end

else begin

led_out <= led_out;

end

end

endmodule

led1.v

module led1 (

input wire sys_clk,

input wire rst_n,

output wire led_out

);

wire locked;

wire clk_200mhz;

pll pll_1(

.sys_clk(sys_clk),

.clk_mul_4(clk_200mhz),

.locked(locked)

);

led led_1(

.clk(clk_200mhz),

.rst_n(locked),

.led_out(led_out)

);

endmodule

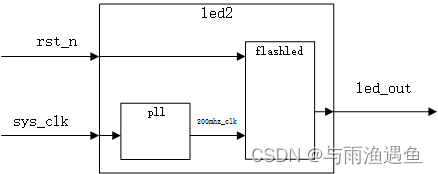

流水灯

框图

代码

flashled.v

module flashled (

input wire clk,

input wire rst_n,

output reg [3:0]led_out

);

//parameter CNT_500MS_MAX = 32'd99_999_999;//200mhz

parameter CNT_500MS_MAX = 32'd62_499_999;//125mhz

reg [31:0]CNT_500MS;

reg [3:0]cnt;

//计数器1

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

CNT_500MS <= 32'd0;

end

else if (CNT_500MS ==CNT_500MS_MAX) begin

CNT_500MS <= 32'd0;

end

else begin

CNT_500MS <= CNT_500MS + 32'd1;

end

end

//计数器2

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

cnt <= 4'd0;

end

else if (cnt == 4'd5 && CNT_500MS == CNT_500MS_MAX) begin

cnt <= 4'd0;

end

else if (CNT_500MS == CNT_500MS_MAX)begin

cnt <= cnt + 4'd1;

end

else begin

cnt <= cnt;

end

end

always @(posedge clk or negedge rst_n) begin

if (~rst_n) begin

led_out <= 4'b1111;

end

else case (cnt)

4'd0: led_out <=4'b0111;

4'd1: led_out <=4'b1011;

4'd2: led_out <=4'b1101;

4'd3: led_out <=4'b1110;

4'd4: led_out <=4'b1101;

4'd5: led_out <=4'b1011;

default: led_out <=led_out;

endcase

end

endmodule

pll.v

module pll (

input wire sys_clk,

output wire clk_mul_4,

output wire clk_125mhz,

output wire locked

);

ip_pll ip_pll_inst (

.inclk0 ( sys_clk ),

.c0 ( clk_mul_4 ),

.c1 ( clk_125mhz ),

.locked ( locked )

);

endmodule

led2.v

module led2 (

input wire sys_clk,

input wire rst_n,

output wire [3:0]led_out

);

wire locked;

wire clk_200mhz;

wire clk_125mhz;

pll pll_1(

.sys_clk(sys_clk),

.clk_mul_4(clk_200mhz),

.clk_125mhz(clk_125mhz),

.locked(locked)

);

flashled flashled_1(

.clk(clk_125mhz),

.rst_n(locked),

.led_out(led_out)

);

endmodule

Signaltap II波形

1940

1940

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?