电路图链接

链接:https://pan.baidu.com/s/1D3Vx_rMmmESP5rIswSl2Ag?pwd=2333

提取码:2333

以下是较为清晰的电路图的连接图。

然后直接说重点,存入和读取的步骤。

以下的设置为1即为将按钮拨为朝上,打开什么按钮就是置为零。

首先是设置电路的初始状态,MR置为一,CE置为一,SW-BUS置为一。

一、存入(以存入11H为例)

1.调节SW7~SW0为存入的地址00000001,LDAR和WE都置为一,打开SW-BUS,点击P2,(观察中间一排灯泡仅最后一个亮即操作无误)

2.关闭SW-BUS,调节SW7~SW0为存入的数据00010001,打开SW-BUS,然后打开CE,点击P1,(观察上面一排灯泡为00010001,1为亮0为暗,即操作无误),关闭CE,关闭SW-BUS。

3.重复上述过程直至全部存入。

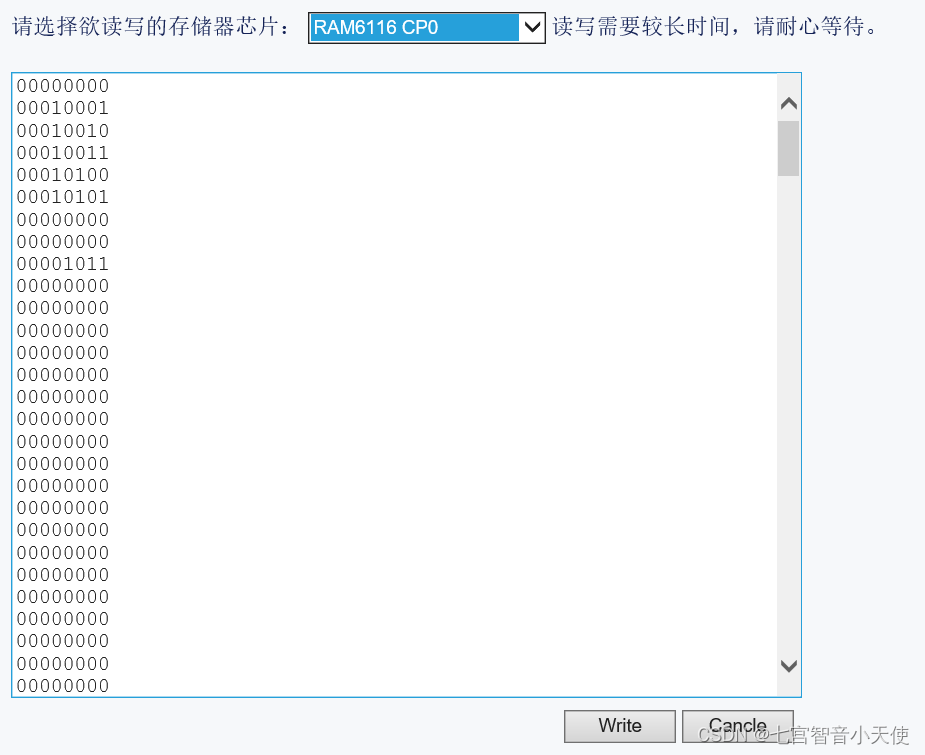

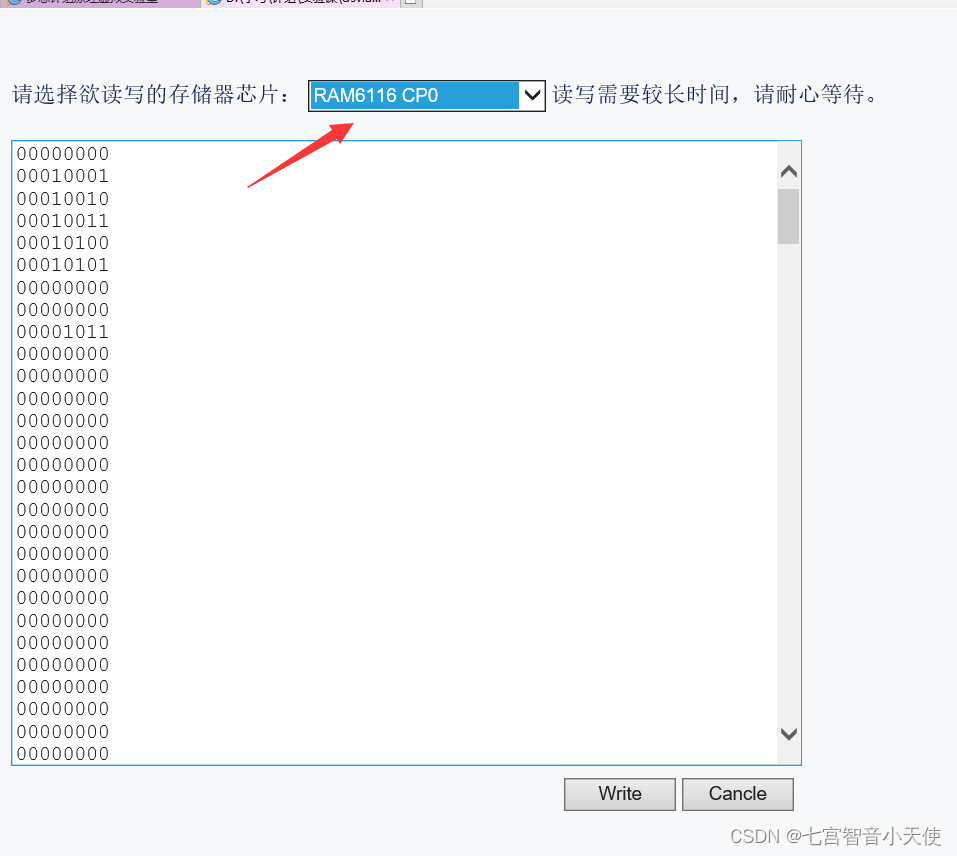

全部存入后的存储器内部的数据图像如下图。

(补充)报告中的思考部分

思考与分析

- 静态半导体存储器与动态半导体存储器的主要区别是什么?

静态RAM(SRAM)速度非常快,只要电源存在内容就不会自动消失。集成度相对较低,功耗也较大。一般高速缓冲存储器用它组成。

动态RAM(DRAM)的内容在10-3或10-6秒之后自动消失,因此必须周期性的在内容消失之前进行刷新。由于它的基本存储电路由一个晶体管及一个电容组成,因此它的集成度高,成本较低,另外耗电也少,但它需要一个额外的刷新电路。DRAM运行速度较慢,SRAM比DRAM要快2~5倍,一般,PC机的标准存储器都采用DRAM组成。 - 由两片 6116( 2K×8) 怎样扩展成( 2K×16) 或( 4K×8) 的存储器? 怎样连线?

两片进行位(竖着排两个)拓展扩展成2K×16,将两片存储器的地址、片选CS、读写控制端R/W相应并联,数据端分别引出。两位进行字扩展(横着排两个)扩展成4K×8,数据线与两片的数据端相连,地址总线的低位地址与两片的11位地址端相连,而高位地址经过译码器和片选端相连。

二、读取

接着上文说到的最后存入完成,此时SW-BUS处于关闭状态,依旧以读取11H为例

1.调整SW7~SW0为00000001,然后打开SW-BUS,然后点击P2,然后打开CE和WE,(观察上面一排灯泡为00010001,1为亮0为暗,即操作无误),关闭CE,关闭SW-BUS。

2.重复上述过程,直至完成所有数据的读取。

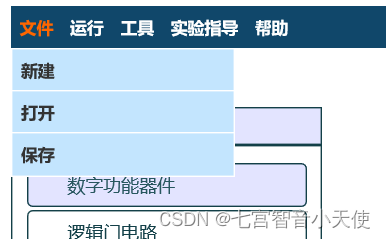

三、如何导入我的电路图

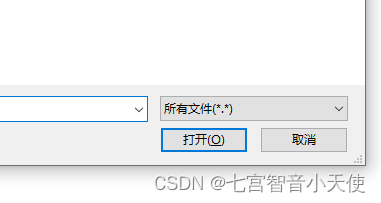

点击打开,在路径中找到我的文件如图

点击打开

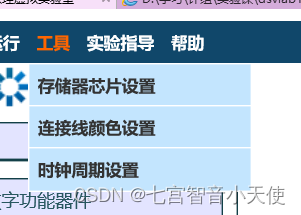

四、如何查看存储器数据以及更改线条颜色

第一个存储器芯片设置为查看存储器,点击后在箭头所指处打开自己的存储器即可。

工具里的第二项更改线条颜色,点击后选择自己想要的颜色然后点击Enter即可。

2847

2847

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?