使用板子信号:GD32F470VKT6(开发板)。

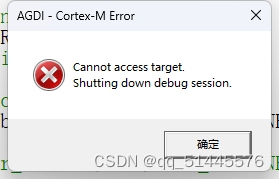

问题:在连接自带的GD-Link后,在正常可以download的情况下,debug会出现“Cannot access target. Shutting down debug session.”情况,如下图所示:

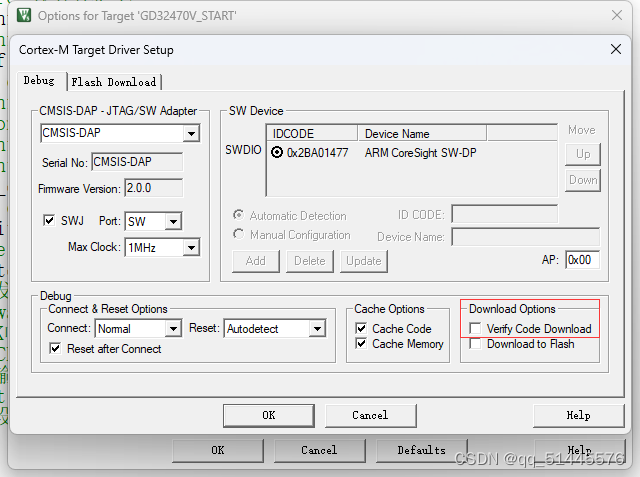

网上查了很多方法,基本都是STM32的,也没有解决,于是无意间发现,在Options for Target(魔法棒)中的debug的settings中,将“Verify Code Download

”取消勾选(之前是默认勾选的),问题解决,很玄学,但是至少可以debug了。

本文讲述了作者在使用GD32F470VKT6开发板时遇到的调试问题,通过取消STM32的VerifyCodeDownload选项解决了Cannotaccesstarget错误,虽然看似玄学,但提供了实用的解决方案。

本文讲述了作者在使用GD32F470VKT6开发板时遇到的调试问题,通过取消STM32的VerifyCodeDownload选项解决了Cannotaccesstarget错误,虽然看似玄学,但提供了实用的解决方案。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?