WLCSP晶圆级芯片封装技术

晶圆级晶粒尺寸封装

所谓{晶圆级封装(Wafer level package)}是指先将整片矽晶圆封装好以后,在进行切割的动作。由于封装以后面积比封装前增加少于120%,因此又称为[晶圆级晶粒尺寸封装(WLCSP:Wafer Level Chip Scale Package)。晶圆级封装必须满足下列两个条件:

- 先封装再切割:必须再晶粒切割前先完成相关的封装与测试制程。

- 类似半导体制程:不使用传统机械方式加压加热接合,而使用类似半导体制程进行封装。

晶圆级晶粒尺寸封装的步骤

晶圆级封装式先将整片晶圆封装好以后,再进行切割的动作,因此使用类似半导体制程进行封装,我们可以想象它的制程就是前面介绍过的半导体制程,详细步骤如下:

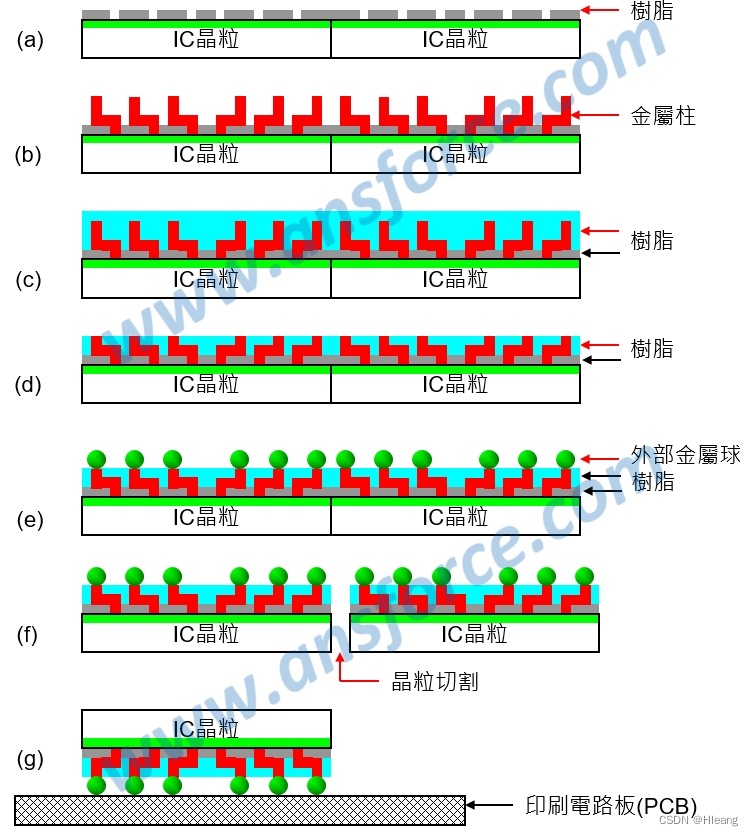

- 树脂涂布:在晶圆制作完成以后(尚未以钻石刀切开之前),使用[旋转涂布]在整片晶圆表面涂布一层环氧树脂,将覆盖在晶圆上访黏着垫(Bond Pad)的环氧树脂以[蚀刻技术]去除,如<图一(a)>所示。

- 金属蒸镀:使用[薄膜成长技术]成为金属薄膜,再使用[蚀刻技术]将不需要的金属薄膜去除,形成金属柱(Plug),如<图一(b)>所示。

- 树脂涂布:使用[旋转涂布]在整片晶圆表面再涂布一层环氧树脂,覆盖在晶圆上方的金属柱,把金属柱完全覆盖起来,如<图一©>所示。

- 表面研磨:使用[化学机械研磨]将整片晶圆表面的环氧树脂与金属柱磨平,使晶圆上方黏着垫区域的金属柱露出,必须同时研磨硬的金属与软的树脂因此并不容易,如<图一(d)>所示。

- 上金属球:以机械钢嘴将金属球加压加热[全部一次]打在晶圆上方露出的金属柱上,相当于使传统集成电路封装的外部金属球,如<图一(e)>所示。

- 晶粒切割:使用钻石刀将晶圆沿切割线切开,就可以得到一颗一颗[已经封装好的]集成电路(IC),如<图一(f)>所示。

封装好的集成电路(IC)可以连接到印刷电路板上,如图所示,如同使用传统的封装技术所得到的集成电路(IC)一样,但是封装后的体积和晶片本身差不多,是目前封装体积最小的封装方式。

晶圆级封装的优缺点:

- 优点:适合小型集成电路,不需要打线成本较低,封装后尺寸很小,适合应用在手机、穿戴式设备等对体积要求很严格的集成电路产品中。

- 缺点:技术因难度较高,与传统的封装方式不同,由于晶片尺寸很小,在有限的面积上无法制作太多的引脚,因此不适合引脚数太多的集成电路。

传统封装技术

早期的封装主要是由封装厂来制作,但随着近些年的演变,我们要求的集成电路体积越来越小,越来越小之后科学家就必须用化学的方法进行一些晶圆的制程来做封装。一旦这些封装技术变成晶圆级,用晶圆的方式进行的时候他就比较适合晶圆厂来做。简单来说,为了缩小封装的体积,但是技术难度太高,传统的封装厂一时间没办法跟上所以晶圆厂变成自己做封装。

集成电路制造和封装技术的未来趋势

目前使用的极紫外光(EUV)微影技术制程节点的极限大约使3纳米(nm),如果要再把集成电路缩小,就只有从对封装技术下手,因此今年来晶圆厂都开始[兼差]发展先进封装技术,包括:2.5D和3D立体封装技术,朝向[小晶片(Chiplet)]方向发展则是必然的趋势。

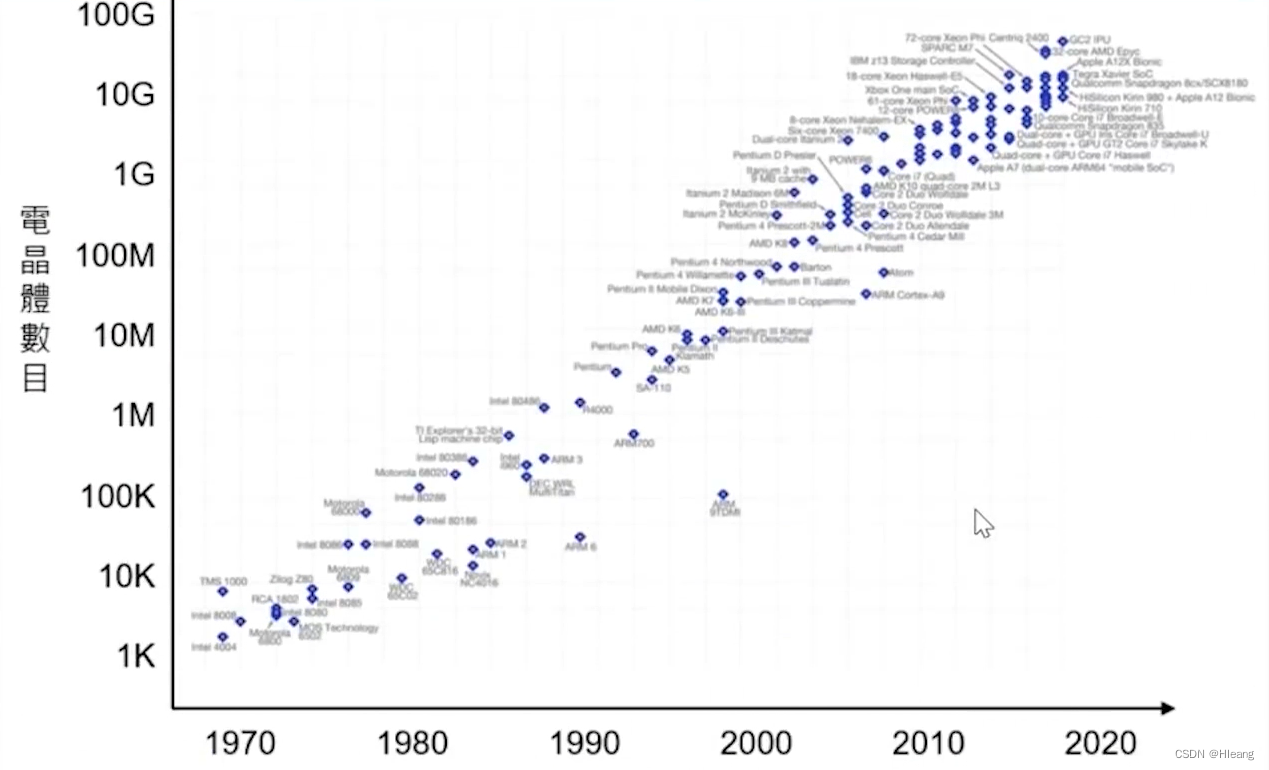

摩尔定律由intel创办人的Gordon Moore首先提出。他观察由1970年代开始的intel 4004处理器,到1980年代的intel 80286处理器,1990年代的intel 80486处理器,2000年的Pentium系列处理器,发现集成电路(IC)的芯片(Chip)上可以容纳的晶体管数目大约每隔两年就会增加一倍,这就是所谓的摩尔定律,如<图二>所示。

后来,英特尔执行长David House则加码提出每18个月芯片的运算。芯片的运算效能就可以提高一倍的看法。曲博不喜欢引用摩尔定律,因为这个所谓的定律其实并不符合科学上定律的条件,充其量只能说是半导体制程资料分析后的规则。不过,这样的规则这些年却愈来愈不准了。

小芯片(Chiplet)的发展

前面我们讨论过制程节点(极限长度),2018年已经量产的制程是7纳米(nm),2019年要量产的制程是5纳米(nm),目前使用的极紫外光(EUV)微影技术一般,相信制程节点的极限大约是3纳米(nm),小于3纳米(nm)基本上使用现在的极紫外光(EUV)已经很难达成,必须改用其他的微影技术,例如X射线(X-ray),电子束(Electron beam)等,而且光罩、材料、制程、化学反应等都必须进行大变动,到底使用哪一种技术,目前还不确定。

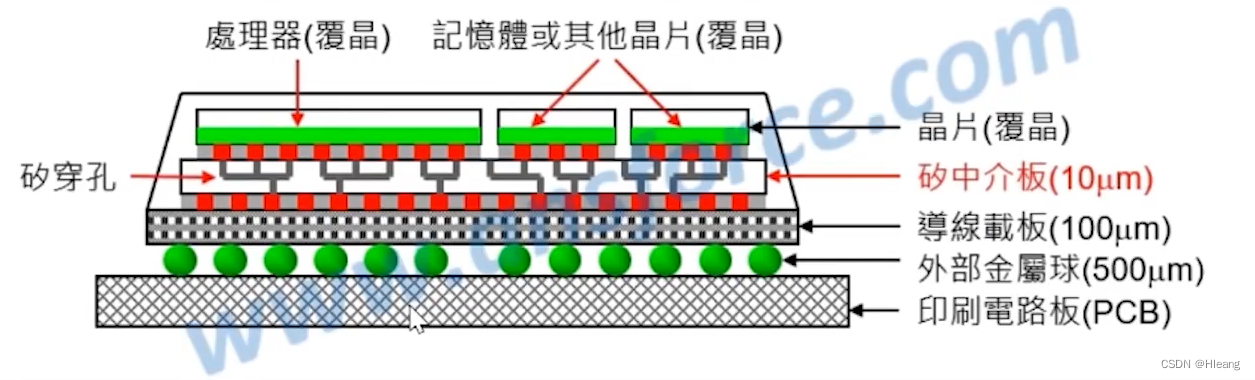

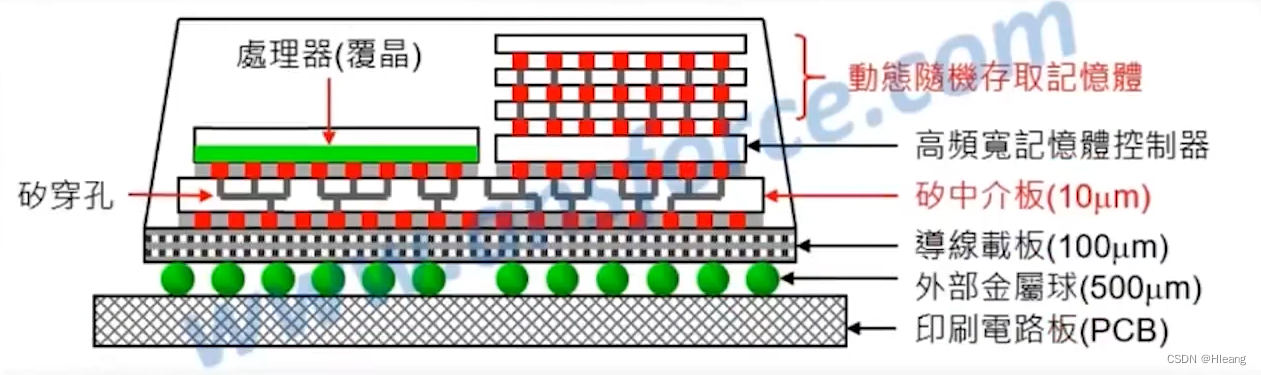

由于芯片内的晶体管制程节点已经缩小到极限,如果要再把集成电路缩小,就只有从封装技术下手。因此,近年来晶体厂都开始[兼差]发展先进封装技术,包括2.5D与3D立体封装技术。朝向小芯片(Chiplet)方向发展则是必然的趋势.

小芯片(Chiplet)的定义

最早期的电子产品是将主动元件晶体管与被动元件电阻、电容、电感等独立的电子元件分别焊接在印刷电路板(PCB)上的,后来发明了[集成电路(IC:Integrated Circuit)]将所有的晶体管整合缩小制作在一个矽晶片(Chip)上,再封装成一个集成电路,整合越多晶体管功能越完整,虽然使得芯片与集成电路的面积变大,但是印刷电路板(PCB上)的电子元件大幅减少,使得电子产品的体积大幅缩小。这是过去50年来集成电路产业的发展方向。

后来愈演愈烈,整合的晶体管越来越多,开始发展[系统单晶片(SoC:System on a Chip)],例如将多核心中央处理器(CPU)图形处理器(GPU)射频(RF)等都整合到单一芯片,使得芯片的面积变大,而且芯片内部的通信连线也很复杂,更重要的是良率降低,因此最近又开始朝向小芯片(Chiplet)的方向发展,将多核心中央处理器(CPU)做成一个小芯片,图形处理器(GPU)做成一个小芯片,射频(RF)做成一个小芯片。

2.5D和3D的封装技术

2.5D封装

3D封装

754

754

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?