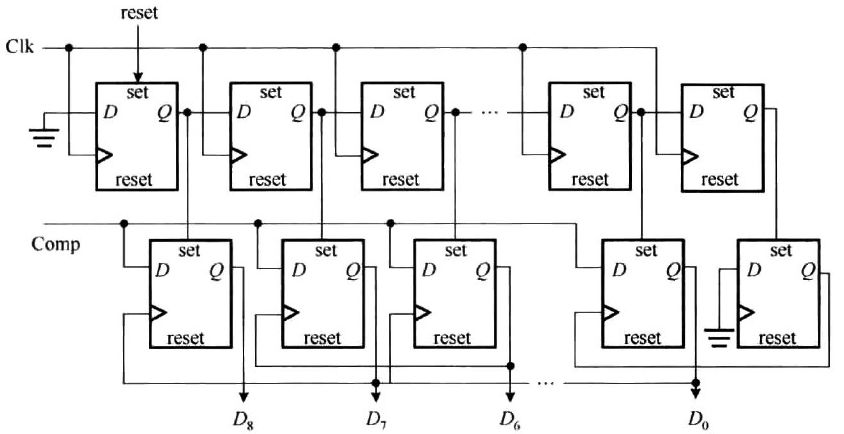

本篇以最基础的SAR寄存器出发,思考如何将逐次逼近的思想做入电路中

注:下文所提第n位都是从左往右数,也就是逐次比较的方向

确定第n位,是在参比之后,不论如何该位之后一位都必须置1。即在第n次比较后,处理第n位时,n+1位都要置1。所以上方一排移位寄存器用于在每个CLK到来时给n+1位置1。

而第n位的去留,在第n次比较之后,而对第n位不做要求,因为结果已定。

因n+1位在第n位比较之后必定置1,而其在初始状态一定为0,故可作为去留的第n位的时钟信号,是去是留由比较结果决定,Vadc>Vx就去(Comp = 0),Vadc<Vx就留(用比较结果作为置数的值,但仅有时钟信号到来的寄存器受到影响,而同一时间仅有一个寄存器有时钟信号,所以下面一排大家公用一条Comp作为D的输入)。所以下面一排寄存器的Q接到上一个的CLK,从左往右看。

4595

4595

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?