目录

参考《Verilog 编程艺术》魏家明著

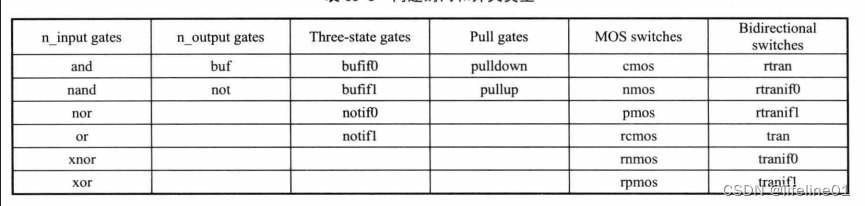

Verilog共有14中逻辑门和12种开关,用于提供门级和开关级模型。

门和开关的声明

1.门和开关的类型由关键字命名。

2.可选驱动强度(Drive strength)

3.可选传输延迟(Propagation delay)

4.门和开关的实例名(Instance name)是可选的

5.实例化时可以使用实例数组(Instance array)

6.同一类型的多个实例在声明时可以使用逗号分隔,所有这样的实例具有同样的驱动强度和延迟要求。

门和开关类型

支持驱动强度的门

and,or,xor,nand,nor,xnor,buf,bufif0,bufif1,not,notif0,notif1,pulldown, pullup它们可以使用的驱动强度分为两类strength0和strength1,分别对应驱动0和1的强度:

strength0: supply0,strong0,pull0,weak0

strength1: supply1,strong1,pull1,weak1例子:

nor (highz1, strong0) n1(out1, in1, in2);延迟

and #(10) a1 (out, in1, in2); // only one delay

and #(10, 12) a2 (out, in1, in2); // rise and fall delays

bufif0 #(10, 12, 11) (out, in, ctrl); // rise fall and turn-off delays实例数组

可以通过实例数组一次实例化多个门或开关的实例。

例子:

module driver (

input en,

input [3:0] in,

output [3:0] out

);

bufif0 ar[3:0] (out, in, en); // array of three-state buffers

endmodule

module busdriver (

input [15:0] busin,

output [7:0] bushigh, buslow,

input enh, enl

);

driver busar3 (busin[15:12], bushigh[7:4], enh);

driver busar2 (busin[11:8], bushigh[3:0], enh);

driver busar1 (busin[7:4], bushigh[7:4], enl);

driver busar3 (busin[3:0], bushigh[3:0], enl);

endmoduleand,nand,nor,or,xor,xnor

1.它们都只能有一个输出端口,可以有多个输入端口,其中输出端口是第一个端口。

2.从逻辑上 nand = ~and,nor = ~or,xnor = ~xor;

例子:

and a1 (out, in1, in2, in3);buf,not

1.它们都只能有一个输入端口,可以有多个输出端口,其中输入端口是最后的端口。

2.从逻辑上 nut = ~buf;

例子:

buf b1 (out1, out2, out3, in);bufif1,bufif0,notif1,notif0

1.它们都只能有一个数据输出端口,一个数据输入端口和一个控制输入端口,第一个端口是数据输出端口,第二个端口是数据输入端口,第三个端口是控制输入端口。

2.对于bufif1和notif1,当控制等于1时,数据通过;当控制等于0时,输出为z

3.对于bufif0和notif0,当控制等于0时,数据通过;当控制等于1时,输出为z

例子:

bufif1 bf1 (outw, inw, controlw);MOS switches

MOS开关有cmos,nmos,pmos,rcmos,mmos,rpmos

例子:

pmos p1 (out, data, control);

cmos (w, datain, ncontrol, pcontrol);

// is equivalent to

nmos (w, datain, ncontrol);

pmos (w, datain, pcontrol);Bidirectional pass switches

双向开关有tran,tranif1,tranif0,rtran,rtranif1,rtranif0

1.对于tran和rtran,它们有两个端口,都是双向数据端口。

2.对于tranif1,tranif0,rtranif1,rtranif0,它们都有三个端口,前两个端口是双向数据端口,第三个端口是控制输入端口。

3.对于tranif1和rtranif1,当控制端口等于1时,数据通过;当控制端口等于0时,输出为z;

4.对于tranif0和rtranif0,当控制端口等于0时,数据通过;当控制端口等于1时,输出为z;

例子:

tranif1 t1 (inout1, inout2, control1);pullup,pulldown

pullup (strong1) p1 (meta), p2(netb);

5578

5578

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?