参考书籍:《Verilog HDL 数字设计与综合》第二版,本文档为第11章的学习笔记。由于本章也讲述的建模方式,开关级建模作为电路设计的最低抽象层,随着复杂度升高,出现了门级、数据流、行为级建模,以本章作为建模方式的起步,有助于认识数字电路设计的基础。

由于先进建模技术的发展开关级建模并不适应复杂的电路。Verilog HDL目前仅提供逻辑值0,1,x,z和他们相关驱动强度进行数字设计的能力,没有模拟设计的能力。更加详细请看Verilog原文档。

学习目标

- 描述基本的MOS开关:NMOS、PMOS、CMOS

- 理解双向传输开关、电源和地的建模方法

- 识别阻抗MOS开关

- 基本MOS开关和双向传输开关上说明延迟方法。

- 建立基本开关级电路

基础理论

关于MOS和CMOS请参考另一篇博客:

11.1 开关级建模元件

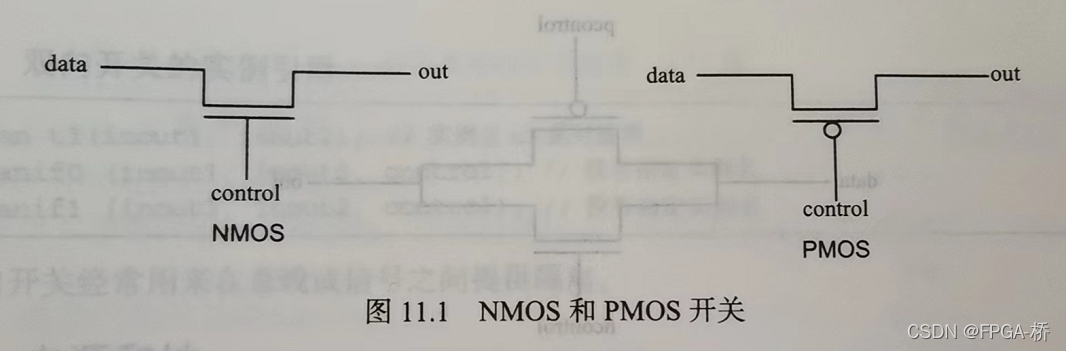

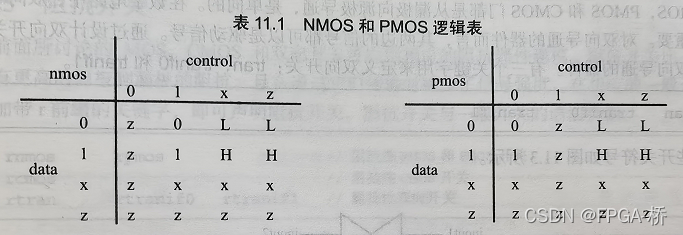

11.1.1 MOS开关

MOS管主要有两类:NMOS和PMOS管(都是增强型)

逻辑表中符号L代表0或者z,H代表1或z。

注意这里不区分源极与漏极

Verilog中的表示及实例化:

使用关键字:nmos pmos

//实例化引用

nmos n1(out, data, control);

pmos p1(out, data, control);

//由于开关时Verilog原定义的,引用时可以不用给出实例名称,但不建议使用

nmos (out, data, control);

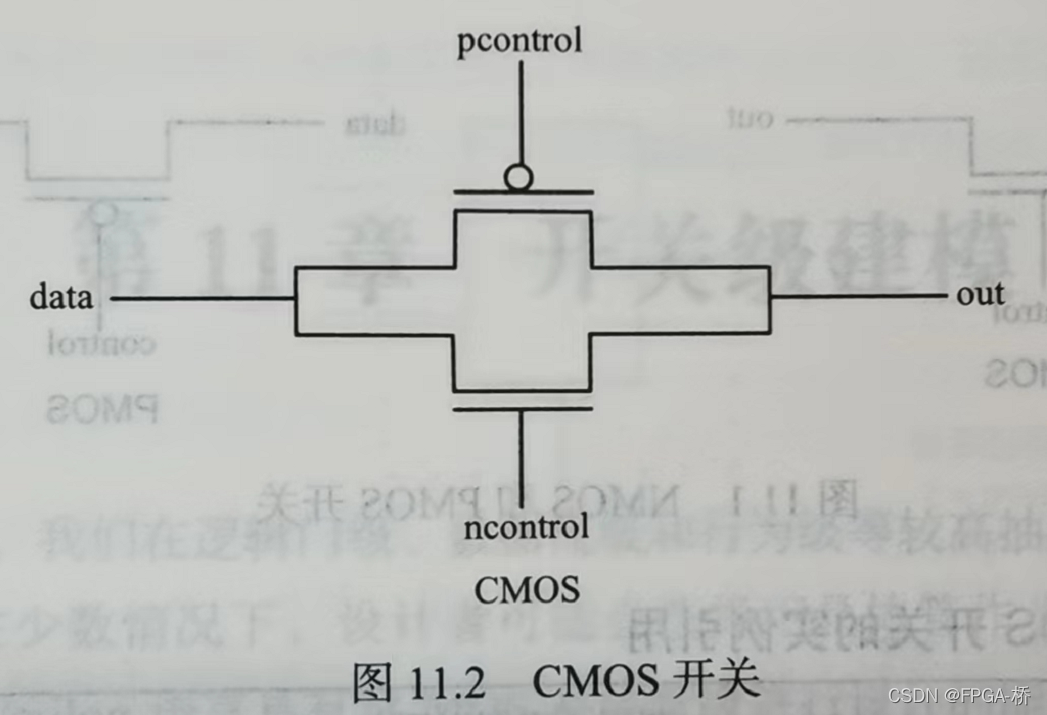

pmos (out, data, control);11.1.1 CMOS开关

| 输入端 | 控制端 | 输出端 | |

| data | pcontrol | ncontrol | out |

| 0、1、x、z | 0 | 1 | data |

| 1 | 0 | z | |

Verilog中的表示及实例化:

使用关键字:cmos

//实例化引用

cmos c1(out, data, ncontrol, pcontrol);

//没有指定实例名

cmos (out, data, ncontrol, pcontrol);11.1.3 双向开关

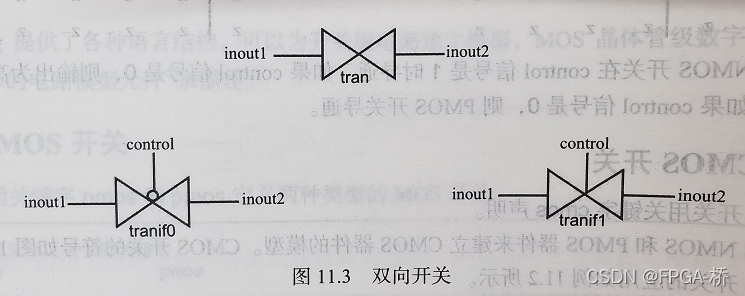

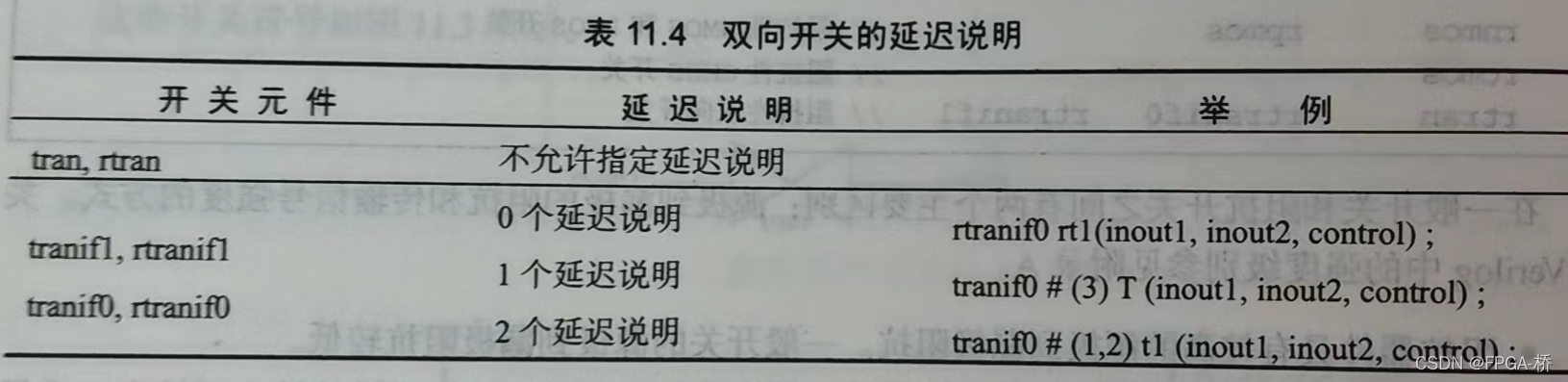

其关键字:tran、tranif0、tranif1

tran:作为信号inout1和inout2之间的缓存,inout1和inout2都可以是驱动信号。

tranif0:当control为0时,inout1和inout2进行连接

tranif1:当control为1时,inout1和inout2进行连接

//实例化

tran t1(inout1, inout2);

tranif0 (inout1, inout2, control);

tranif1 (inout1, inout2, control);11.1.4 电源和地

晶体管中的源极(Vdd,1)和地级(Vss,0)分别用关键字supply1和supply0来定义。

整个模拟过程supply1和supply0始终代表网表提供逻辑值1和逻辑值0。

//实例化

supply1 vdd;

supply0 vss;

//变量的连接

assign a = vdd;

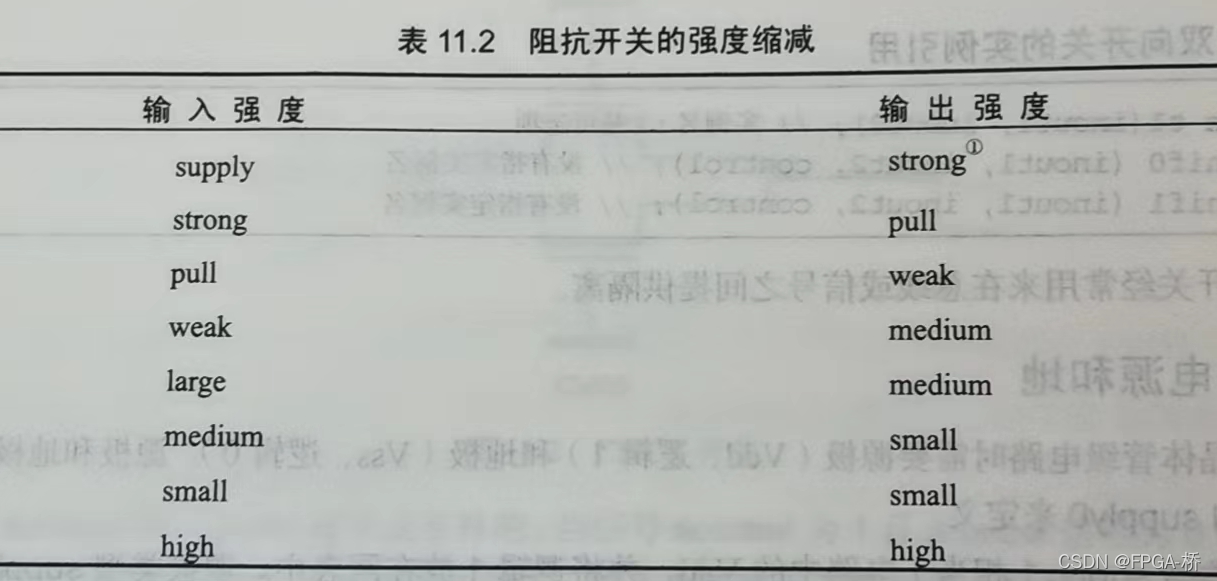

assign b = vss;11.1.5 阻抗开关

在之前的mos管的关键字前加入字母r,表示成阻抗开关,比一般的开关具有更高的源极到漏极的阻抗,且在通过它们传输时减少了信号强度。

//阻抗开关相应的关键字

rnmos rpmos

rcmos

rtran rtranif0 rtranif1- 阻抗器件具有较高的源极到漏极阻抗。一般开关阻抗较低

- 阻抗开关在传递时减少了信号强度

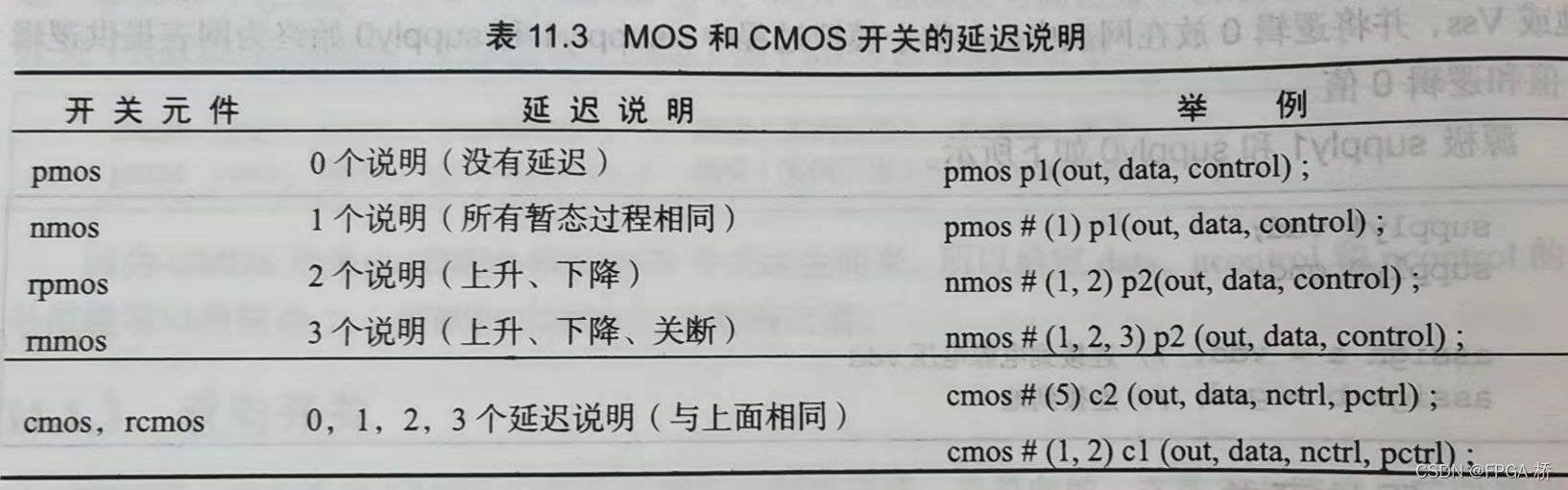

11.1.6 开关中的延迟说明

MOS和CMOS开关

可以通过这些开关级元件的信号指定延迟。延迟是可选项,它能紧跟在开关的关键字之后。可以为开关指定0、1、2或3个时延。

双向传输开关

这种开关在传输信号时没有时延,但是当开关值切换时由开关时延。

specify

使用开关设计的模块指定路径延迟(引脚到引脚的延迟)以及时序检查。用specify快可以描述路径延迟。

11.2 由CMOS组成的电路

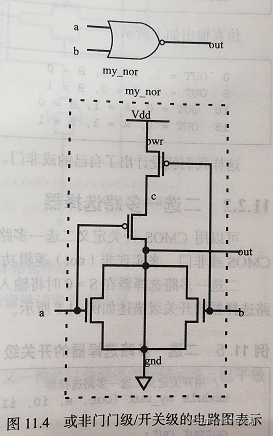

11.2.1 CMOS或非门(nor)

虽然Verilog有nor门原语,这里使用CMOS开关设计或非门。

或非门功能是只有a、b都为0是才输出。

//设计块

module CMOS_nor(out, a, b);

input a, b;

output out;

//定义电源

supply1 Vdd;

supply0 Gnd;

//实例化PMOS开关

pmos (c, Vdd, b);

pmos (out, c, a);

nmos (out, Gnd, a);

nmos (out, Gnd, b);

endmodule

//激励块

module tb_CMOS_nor();

reg A, B;

wire OUT;

CMOS_nor nor1(.out(OUT), .a(A), .b(B));

initial begin

A = 1'b0;

B = 1'b0;

#10 A = 1'b0; B = 1'b1;

#10 A = 1'b1; B = 1'b0;

#10 A = 1'b1; B = 1'b1;

end

initial

$monitor($time ,"OUT = %b, A = %b, B = %b", OUT, A, B);

endmodule

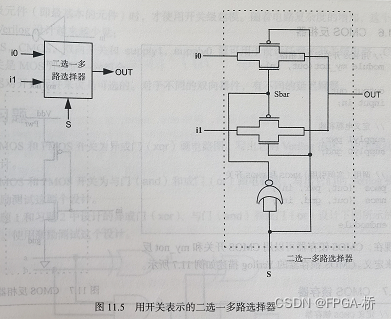

11.2.2 二选以多路选择器

这里为CMOS开关级建模,还有其他建模方式,如行为级建模:

//设计块

module mux2_1(out, s, in0, in1);

output out;

input s, in0, in1;

wire sbar; //s的取反

not (sbar, s);

cmos(out, in0, sbar, s);

cmos(out, in1, s, sbar);

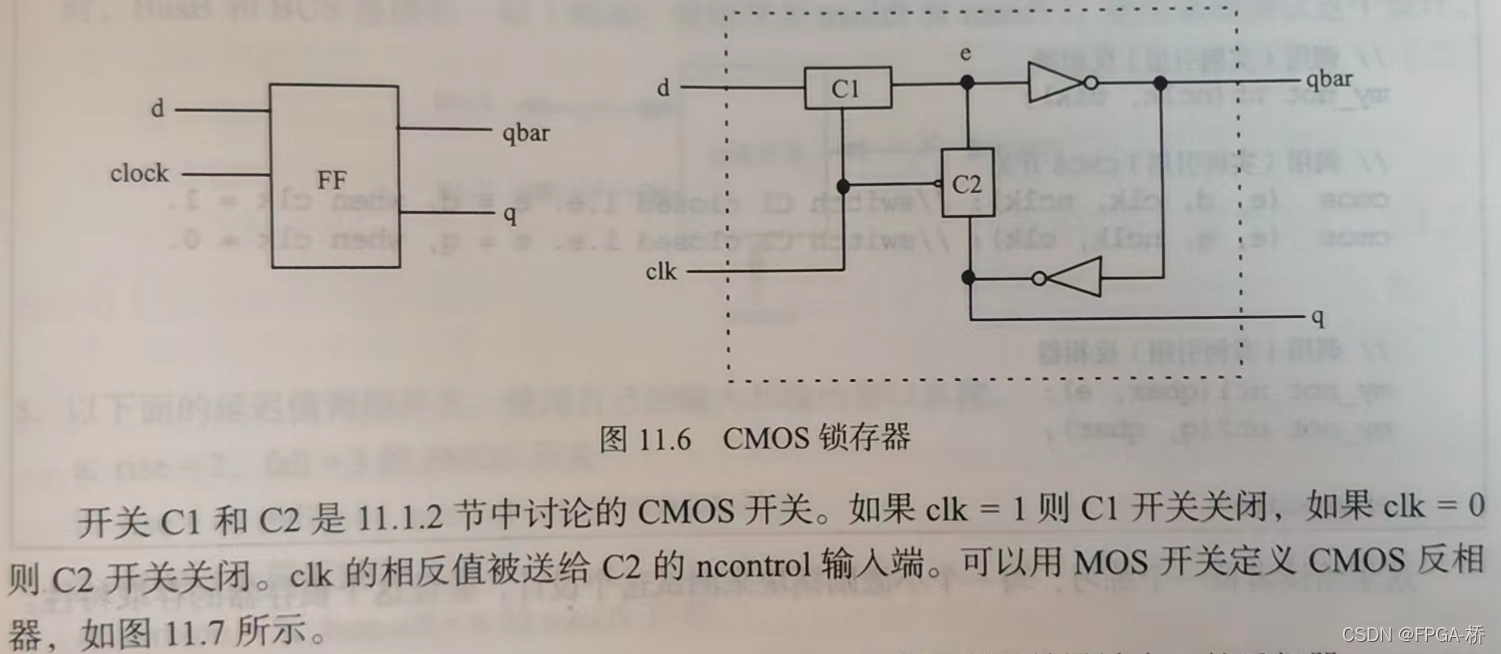

endmodule11.2.3 简单的CMOS锁存器

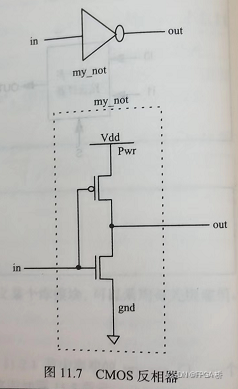

关于锁存器的其他建模方式,如SR锁存器的行为级建模:三、4【Verilog HDL】基础知识之模块和端口_FPGA-桥的博客-CSDN博客清楚模块中的组成部分模块的端口列表声明模块实例化及其端口信号连接标识符层次 https://blog.csdn.net/ARM_qiao/article/details/124208735下图反相器也可以使用CMOS设计反相器

https://blog.csdn.net/ARM_qiao/article/details/124208735下图反相器也可以使用CMOS设计反相器

//程序块

//定义CMOS反相器

module CMOS_not(out, in);

output out;

input in;

supply1 Vdd;

suppiy0 Gnd;

pmos(out, Vdd, in);

nmos(out, Gnd, in);

endmodule

//定义CMOS锁存器

module cff(q, qbar, d, clk);

output q, qbar;

input d, clk;

wire e;

wire nclk;

CMOS_not nt1(nclk, clk);

cmos(e, d, clk, nclk);

cmos(e, q, nclk, clk);

endmodule

本文档介绍了Verilog HDL中开关级建模的基本元素,包括NMOS、PMOS、CMOS开关,双向传输开关,电源和地的建模方法。学习目标包括理解MOS开关的延迟描述,建立基本的CMOS电路,如CMOS或非门和二选一多路选择器。此外,还涉及了简单的CMOS锁存器设计。

本文档介绍了Verilog HDL中开关级建模的基本元素,包括NMOS、PMOS、CMOS开关,双向传输开关,电源和地的建模方法。学习目标包括理解MOS开关的延迟描述,建立基本的CMOS电路,如CMOS或非门和二选一多路选择器。此外,还涉及了简单的CMOS锁存器设计。

2172

2172

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?