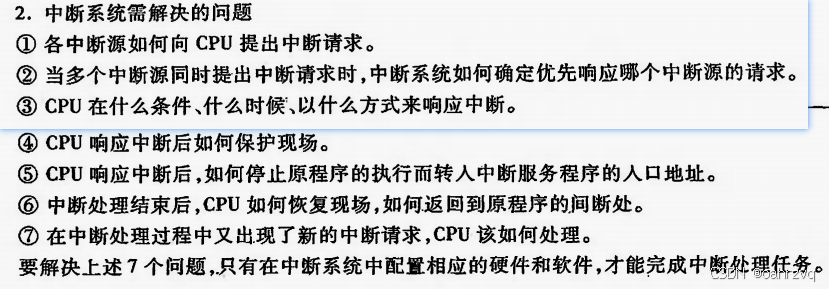

结合RISC-V CPU架构对中断系统七个关键问题的详细解析,按照由浅入深的结构进行说明:

一、中断请求机制(问题①)

硬件基础:

RISC-V通过CLINT(Core Local Interrupter)和PLIC(Platform-Level Interrupt Controller)实现中断请求传递。

• 内部中断(定时器/软件中断)由CLINT直接向CPU发送请求

• 外部中断(如GPIO、外设)通过PLIC统一收集,PLIC的每个中断源有独立ID(如UART=10,SPI=14)

软件协作:

mip(Machine Interrupt Pending)寄存器各bit位对应不同中断类型,CPU通过轮询mip.MEIP(外部中断挂起)等标志位感知请求。

二、中断优先级判定(问题②)

硬件仲裁规则:

-

RISC-V特权架构强制优先级:

• 异常 > 外部中断 > 定时器中断 > 软件中断• 紧急程度:Non-maskable中断(NMI) > 可屏蔽中断

-

PLIC动态优先级:

• 每个中断源可配置0-7级优先级(实际芯片可扩展)• 仲裁逻辑:优先级数值高者优先,同级则ID小者优先

软件策略:

通过PLIC_priority寄存器动态调整优先级,例如网络中断优先级可设为7,键盘中断设为3。

三、中断响应条件(问题③)

响应三要素:

if ((mstatus.MIE == 1) && // 全局中断使能

(mip & mie) != 0 && // 中断使能掩码匹配

(current_privilege <= interrupt_privilege)) // 特权级检查

{

trap_handler(); // 触发中断响应

}

响应过程:

- 冻结流水线,保存

pc到mepc - 保存

mstatus状态到MPP和MPIE字段 - 跳转到

mtvec寄存器指定的中断向量表基地址

四、现场保护机制(问题④)

硬件自动保存:

• mepc:被中断指令地址

• mcause:中断原因代码(如0x8000000B表示外部中断)

• mtval:附加信息(如非法指令的具体编码)

软件手动保存:

// 典型上下文保存代码

csrrw sp, mscratch, sp // 切换专用栈指针

addi sp, sp, -32*4

sw x1, 0(sp) // 保存通用寄存器

sw x2, 4(sp)

...

sw x31, 124(sp)

五、中断服务程序跳转(问题⑤)

向量化处理模式(mtvec.MODE=1):

void __attribute__((interrupt)) handle_irq() {

uint32_t cause = mcause & 0xFFF;

void (*handler)(void) = vector_table[cause]; // 向量表跳转

handler();

}

统一处理模式(mtvec.MODE=0):

csrr a0, mcause // 读取中断原因

andi a0, a0, 0x3FF // 提取中断ID

slli a0, a0, 2 // 计算偏移量

la t0, irq_handler_table

add t0, t0, a0

jalr t0 // 跳转到具体处理程序

六、现场恢复与返回(问题⑥)

恢复阶段:

-

寄存器恢复:

lw x31, 124(sp) // 反向恢复寄存器 ... lw x1, 0(sp) addi sp, sp, 32*4 csrrw sp, mscratch, sp -

特权返回指令:

mret指令同时完成:

• 恢复mstatus.MIE• 跳转回

mepc地址

原子性保障:

恢复过程需关闭中断(csrci mstatus, 8),防止恢复过程中断。

七、嵌套中断处理(问题⑦)

硬件支持:

• mstatus.MPIE保存进入中断前的MIE状态

• mstack专用中断栈指针寄存器(部分扩展实现)

软件实现步骤:

void nested_irq_handler() {

csrwi mstatus, 0x88 // 开启嵌套中断(MIE=1, MPIE=1)

push_registers(); // 使用独立中断栈

// 处理新中断...

pop_registers();

csrwi mstatus, 0x08 // 关闭当前层中断

}

深度控制:

通过mstack指针偏移量检测嵌套深度,防止栈溢出。

硬件/软件协同全景

(图示:绿色部分为硬件自动处理,蓝色为软件处理流程)

关键配置寄存器:

| 寄存器 | 功能描述 |

|---|---|

mstatus | 全局中断使能(MIE)、特权模式 |

mie | 中断类型使能掩码 |

mip | 中断挂起状态 |

mtvec | 中断向量表基址 |

mscratch | 专用栈指针暂存 |

通过以上软硬协同机制,RISC-V实现了符合POSIX标准的可抢占式中断系统,典型中断延迟可控制在10-30个时钟周期。实际应用中需结合具体芯片实现(如SiFive E系列与U系列中断控制器差异)进行优化配置。

334

334

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?