目录

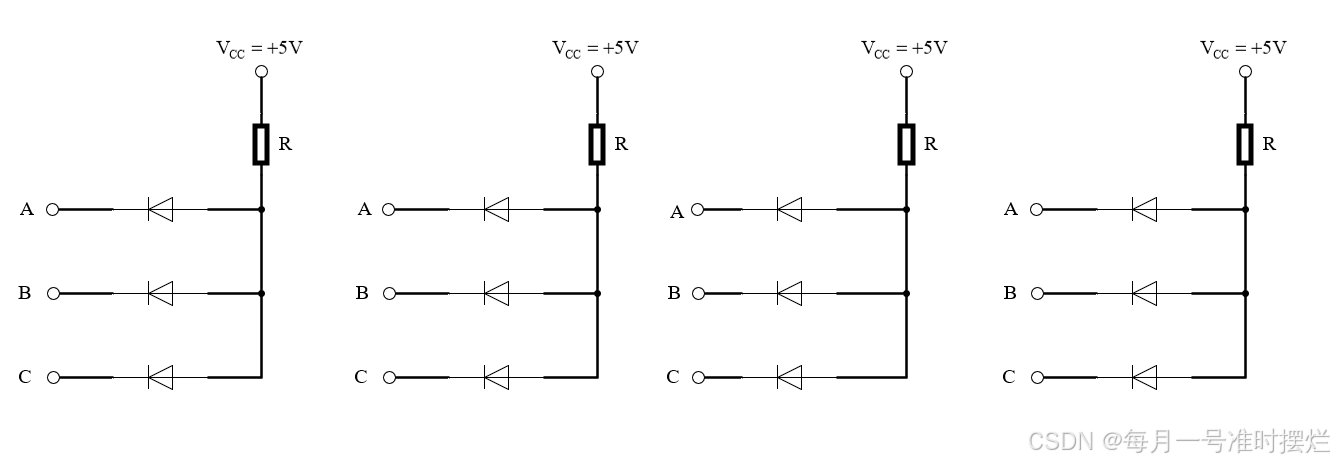

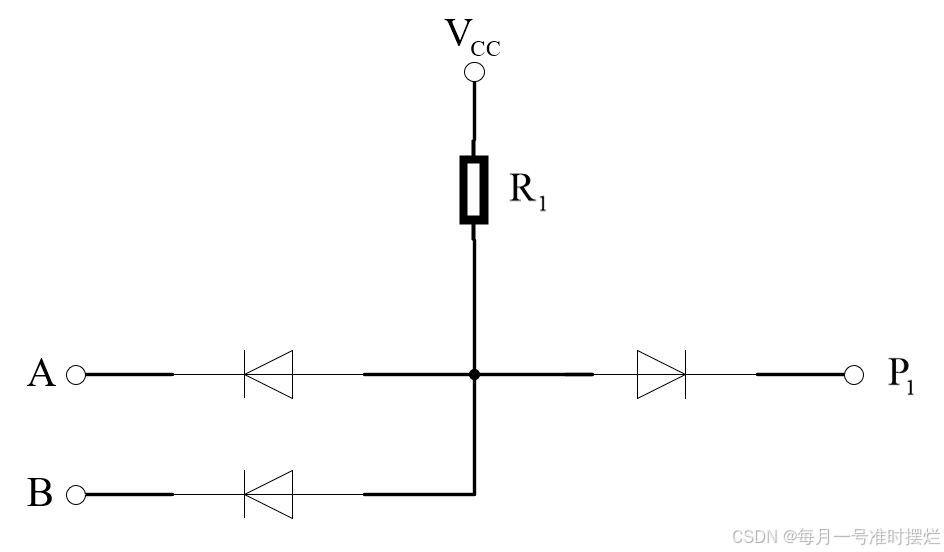

在由二极管构成的简单门电路中,二极管的工作特性往往不是理想的。如下图示:

在上面这张图中,由四个相同的与门电路组成,当与门输出为低电平时,二极管正向导通,由于正向导通的存在,与门相对于0V输入点位,会产生0.7V的点位平移。当多个与门级联的时候,二极管的正向导通压降最后一级输出为2.8V,产生严重的点位偏移,影响最后的结果。

TTL门电路相对于CMOS门电路来说,TTL门电路速度更快,尤其是在低电阻的情况下,其传播速度比CMOS电路更慢。同时,TTL电路对电源噪声和地线噪声的容忍度较高,能够在噪声较大的环境中稳定工作,逻辑点评的范围更大更稳定。除此之外,CMOS门电路相对于TTL门电路来说带负载的能力较差。

1 TTL门电路

与二极管门电路相比,这种双极型二极管构造了门电路结构虽然复杂,但是开关的速度开、带负载能力强,这种是TTL门电路。

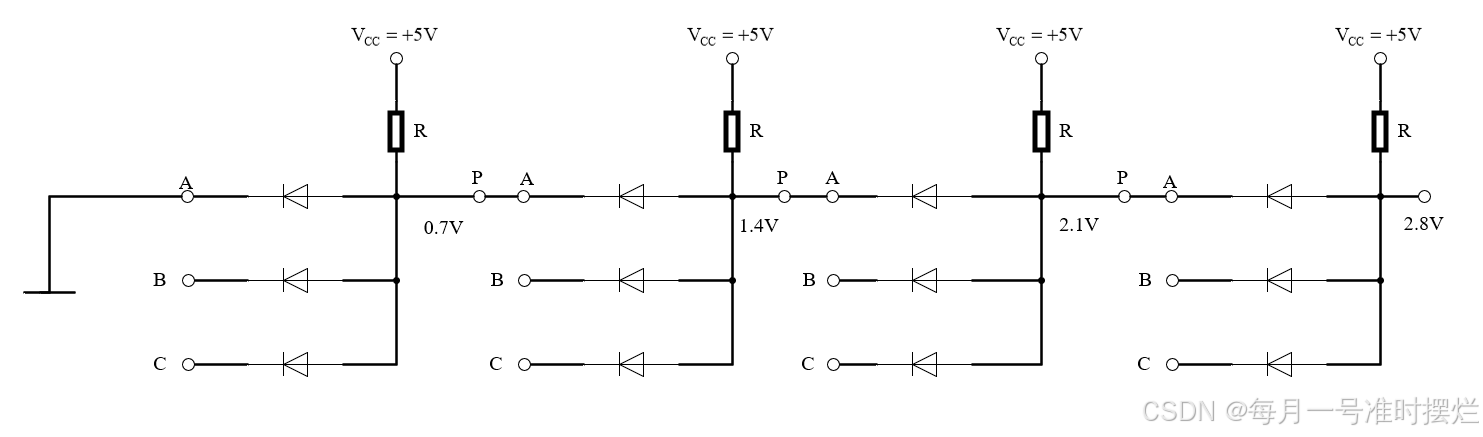

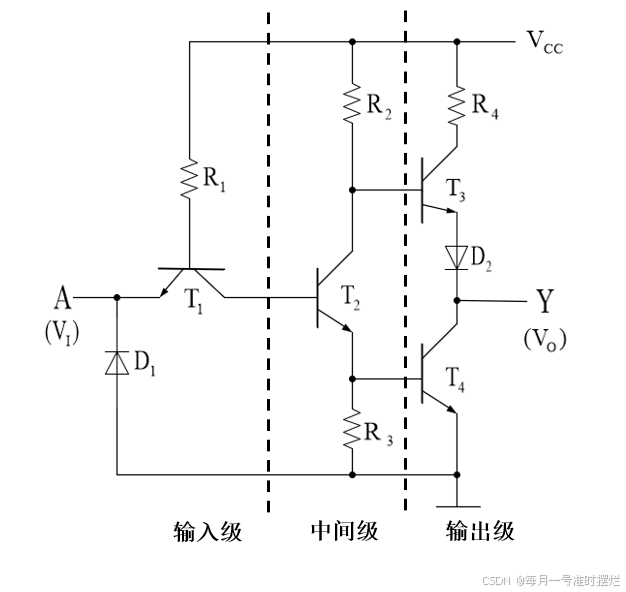

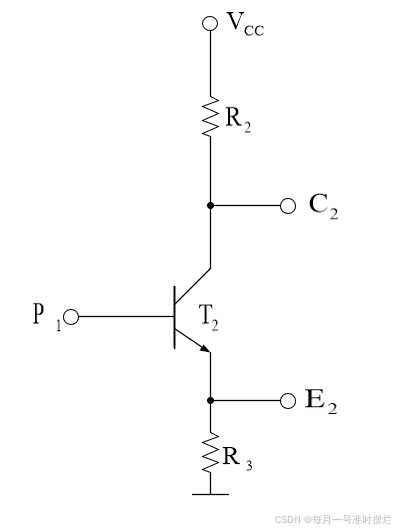

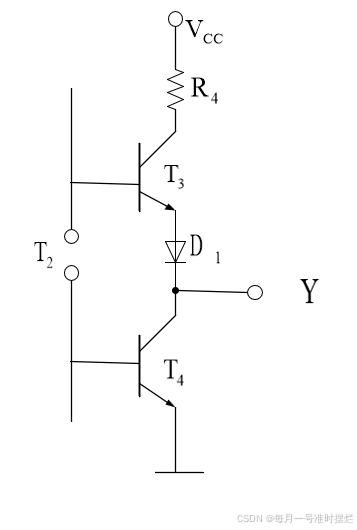

如下图所示为TTL门电路的经典电路:

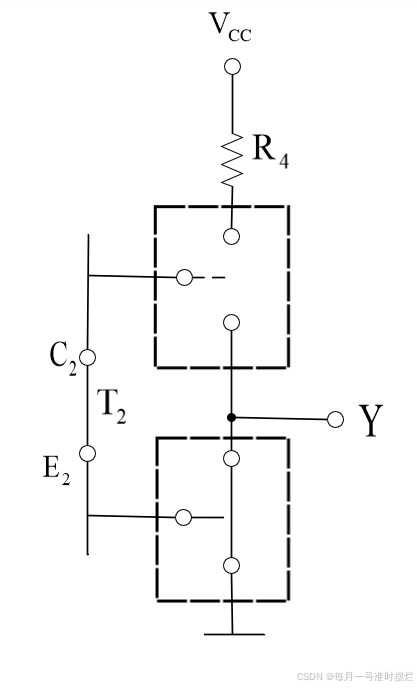

对于TTL门电路来说,也可以使用双电源的方式,如下所示:

但是在现实中基本不会使用这种双电源的电路结构,主要原因是双电源的电路结构如果在没有优化的情况下会增加静态消耗,同时也会增加额外的动态功耗,并且双电路可能导致更高的电路噪声,影响电路的稳定性。

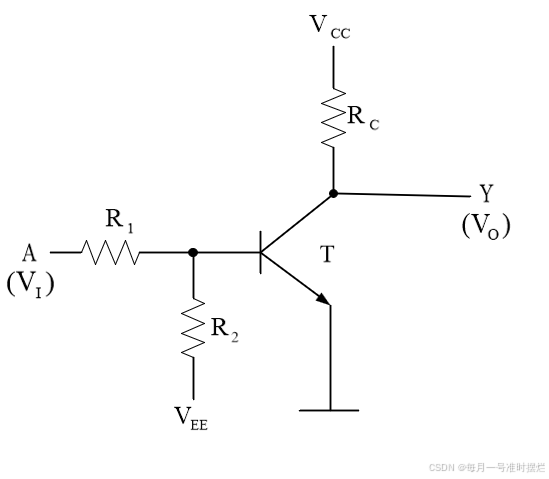

如下图所示为一种经典的TTL门电路:

在上面的电路中,分为输入级、中间级和输出级,如下图所示:

在上图中,所对应的逻辑关系为逻辑非,关系式为Y=A'。逻辑图如下所示:

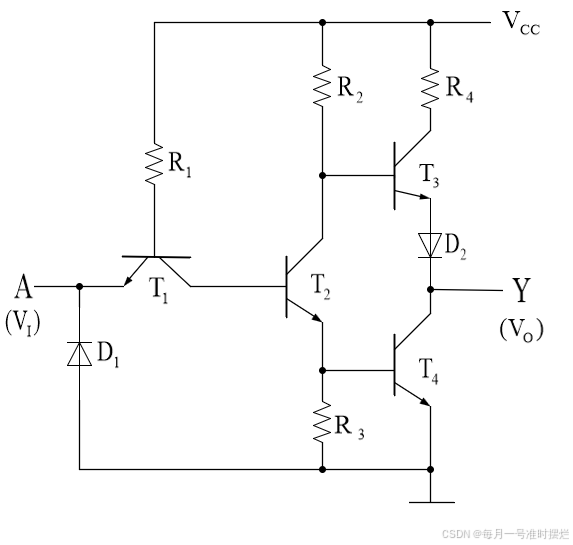

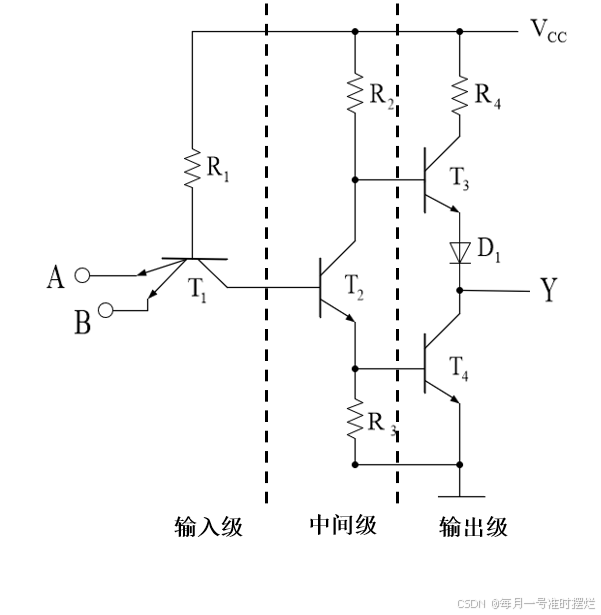

除此之外,还有两个输入变量的经典TTL门电路如下所示:

在上图中,所对应的逻辑关系为逻辑与非,逻辑式为:Y=(A.B)'。逻辑图如下所示:

下面分别对TTL电路中输入级、中间级和输出级进行介绍。

1.1 输入级

在输入级、中间级和输出级中以上面逻辑与非的电路图为例。

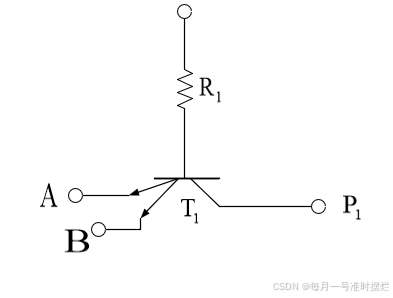

输入级是由单个或者多个发射结的晶体以及上拉电阻组成的。输入级电路图如下图所示:

对于逻辑与非的TTL门电路输入级来说,将的发射结以及集电接由二极管来表示的话,示意图如下所示:

输入端的两个二极管和上拉电阻构成了与门结构的集电极,它的集电极等效负载电阻是由电阻

以及

的集电结反向电阻构成的,它的集电极负载电阻的阻值非常大,因此在稳态的时候

的集电结一般处于正偏。因此

点是处于正偏,

相当于A和B的与关系,即

。

1.2 中间级

TTL门电路的中间级又被称为倒相级,由上拉电阻、下拉电阻

以及晶体管

构成的。TTL门电路的中间级电路如下所示:

如果不考虑集电极和发射级向下一级分流的话,那么电阻和

流过同一个电流,可以得到

的集电结和发射结的线性方程:

,

。当

上升时,由

可推断,

增加,

不变,此时

减少;同时当

上升,

也随着上升。

当中间级收到输入信号的控制处于饱和导通状态的时候,它的集电极和发射极

之间的电位差非常小,此时输出的饱和压降为0.3V,此时

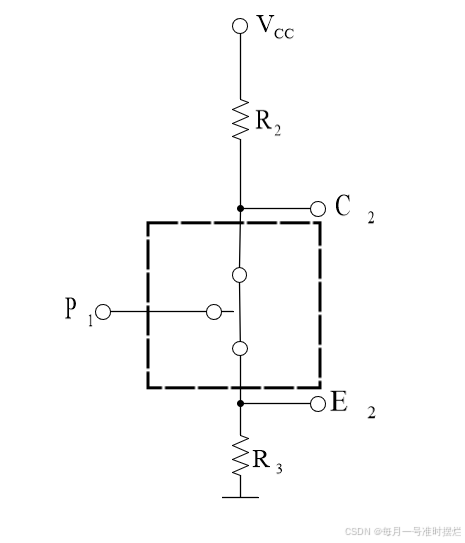

相当于断开状态。如下图所示为开关模拟示意图:

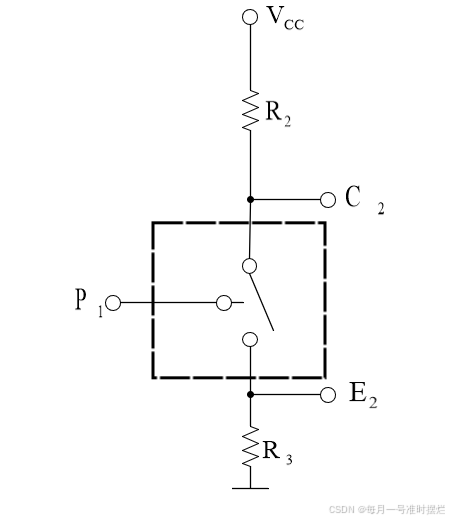

当晶体管受到输入信号的控制处于截止状态的时候,它的集电极电流约为0,此时集电极点位约等于

,而自身的发射级的点位约等于0,此时

相当于断开状态。如下图所示为开关模拟示意图:

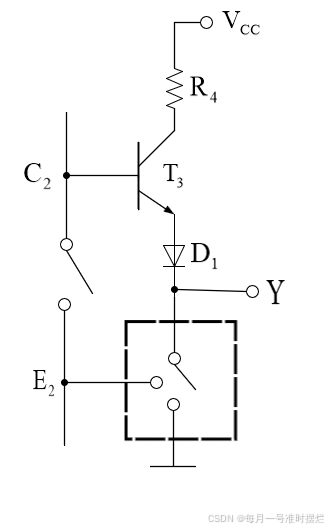

1.3 输出级

TTL门电路的输出级是由两个双极行晶体管和

、一个二极管

和上拉电阻

组成。如下图所示为TTL门电路输出级的电路结构:

当中间级的晶体管处于饱和导通的时候,的发射结和二极管

处于零偏的工作状态,而

的发射结可以得到一个正向的偏置电压,所以

的输出电流全部流向了

的基级,所以

的偏置电流全部流向了

的基极,使得

饱和导通。示意图如下所示:

当晶体管处于截止状态的时候,它的集电极

可以使

和

导通,而发射级点位

对应的地点为可以使得

的发射结得不到合适的偏置电压,使得

处于截止的状态。两个晶体管

和

在中间级

的控制之下,始终是一个导通一个截止的状态,因此有效降低输出级的静态功耗,因此被称为推挽式输出级。如下图所示为晶体管

处于截止状态:

当和

处于导通的时候,工作于射级跟随的状态,此时电路的阻抗非常小,输出稳定的高电平,带负载的能力加强。当输出为低电平的时候,也就是

饱和导通的时候,它的输出阻抗也非常小,因此这种具有推挽式输出级的电路结构驱动负载能力很强。

(本节参考了哈尔滨工业大学《数字电子技术基础》内容)

924

924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?