3.4 TTL门电路

3.4.1 双极型三极管的开关特性

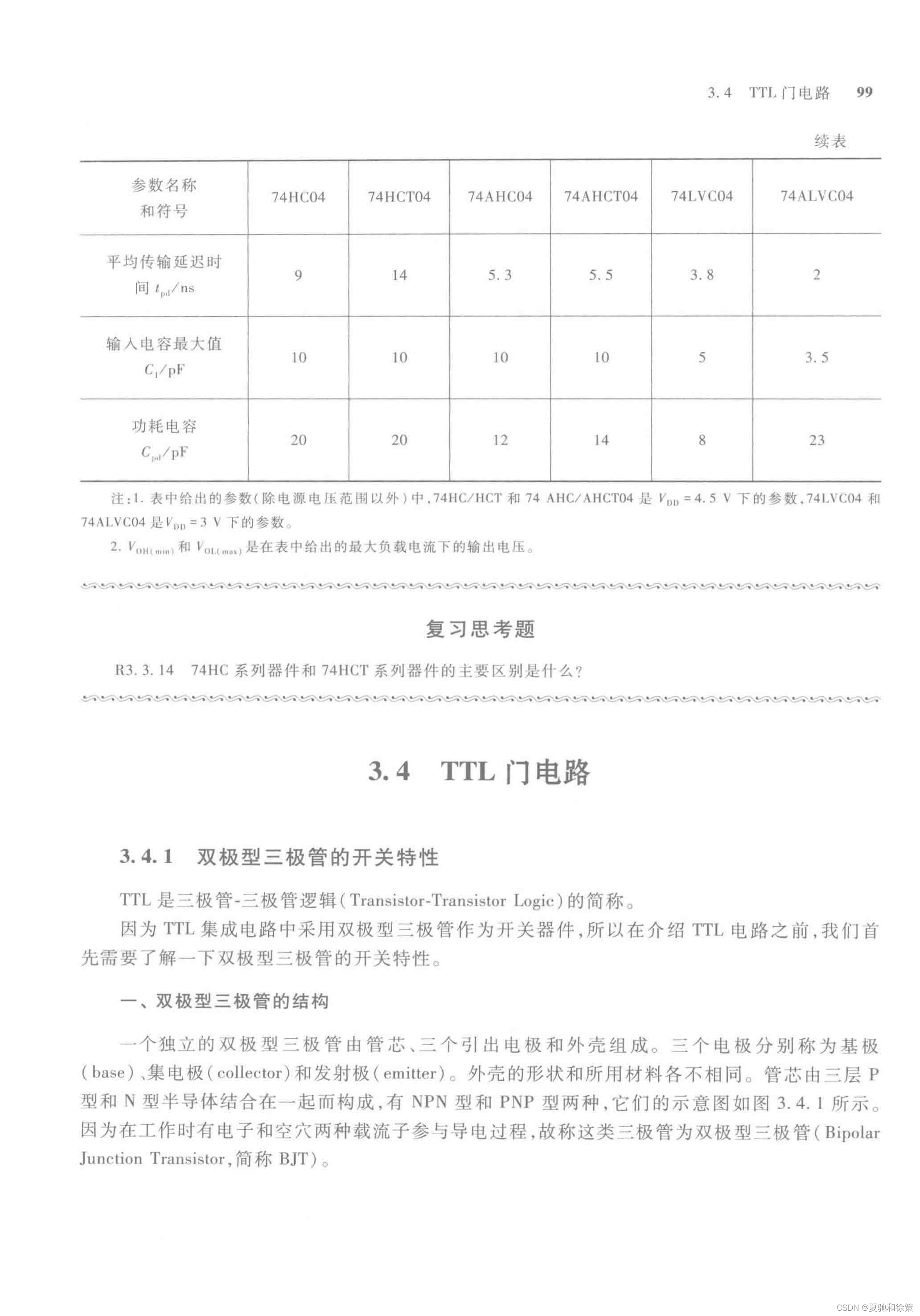

TTL是三极管-三极管逻辑(Transistor-Transistor Logic)的简称。因为TTL集成电路中采用双极型三极管作为开关器件,所以在介绍TTL电路之前,我们首先需要了解一下双极型三极管的开关特性。

一、双极型三极管的结构

一个独立的双极型三极管由管芯、三个引出电极和外壳组成。三个电极分别称为基极(base)、集电极(collector)和发射极(emitter)。外壳的形状和所用材料各不相同。管芯由三层P型和N型半导体结合在一起而构成,有NPN型和PNP型两种,它们的示意图如图3.4.1所示。因为在工作时有电子和空穴两种载流子参与导电过程,故称这类三极管为双极型三极管(Bipolar Junction Transistor,简称BJT)。

图3.4.1 双极型三极管的两种类型

(a) NPN型 (b) PNP型

二、双极型三极管的输入特性和输出特性

若以基极b和发射极e之间的发射结作为输入回路,则可以测出表示输入电压 𝑣𝐵𝐸vBE 和输入电流 𝑖𝐵iB 之间关系的特性曲线,如图3.4.2(a)所示。这个曲线称为输入特性曲线。由图可见,这个曲线近似于指数曲线。为了简化分析计算,经常采用图中虚线所示的折线来近似。图中的 𝑉𝐵𝐸(𝑜𝑛)VBE(on) 称为开启电压。硅三极管的 𝑉𝐵𝐸(𝑜𝑛)VBE(on) 为0.5~0.7 V,锗三极管的 𝑉𝐵𝐸(𝑜𝑛)VBE(on) 为0.2-0.3 V。

图3.4.2 双极型三极管的特性曲线

(a) 输入特性曲线 (b) 输出特性曲线

若以集电极c和发射极e之间的回路作为输出回路,则可测出在不同 𝑖𝐵iB 值下表示集电极电流 𝑖𝐶iC 和集电极电压 𝑣𝐶𝐸vCE 之间关系的曲线,如图3.4.2(b)所示。这一族曲线称为输出特性曲线。由图可知,集电极电流 𝑖𝐶iC 不仅受 𝑣𝐶𝐸vCE 的影响,还受输入的基极电流 𝑖𝐵iB 的控制。输出特性曲线明显地分成三个区域。

- 放大区:曲线右边水平的部分称为放大区(或者叫线性区)。放大区的特点是 𝑖𝐶iC 随 𝑖𝐵iB 成正比地变化,而几乎不受 𝑣𝐶𝐸vCE 变化的影响。 𝛽=Δ𝑖𝐶Δ𝑖𝐵β=ΔiBΔiC 称为电流放大系数,普通三极管的 𝛽β 值多在几十到几百的范围内。

- 饱和区:曲线靠近纵坐标轴的部分称为饱和区。饱和区的特点是 𝑖𝐶iC 不再随 𝑖𝐵iB 以 𝛽β 倍的比例增加而趋向于饱和。硅三极管开始进入饱和区的 𝑉𝐶𝐸VCE 值约为0.6~0.7V。在深度饱和状态下,集电极和发射极间的饱和压降 𝑉𝐶𝐸(𝑠𝑎𝑡)VCE(sat) 在0.2V以下。

- 截止区:图3.4.2(b)中 𝑖𝐵=0iB=0 的一条输出特性曲线以下的区域称为截止区。截止区的特点是 𝑖𝐶iC 几乎等于零。这时仅有极微小的反向穿透电流 𝐼𝐶𝐵𝑂ICBO 流过。硅三极管的 𝐼𝐶𝐵𝑂ICBO 通常都在1μA以下。

三、双极型三极管的基本开关电路——三极管反相器

用NPN型三极管取代图3.1.1(a)中的开关S,就得到了图3.4.3所示的三极管开关电路。只要电路的参数配合得当,必能做到输入电压 𝑣𝑖𝑛vin 为低电平时三极管工作在截止状态,输出为高电平;而 𝑣𝑖𝑛vin 为高电平时三极管工作在饱和状态,输出为低电平。因此,这就是一个反相器电路。

图3.4.3 三极管反相器的基本开关电路

- 当输入电压 𝑣𝑖𝑛=0vin=0 时,三极管的 𝑖𝐵=0iB=0。由图3.4.2(a) 所示的输入特性曲线可知,这时 𝑖𝐵=0iB=0,三极管处于截止状态。如果采用图3.4.2(a)中折线化的近似输入特性,则近似地认为在 𝑣𝑖𝑛<𝑉𝐵𝐸(𝑜𝑛)vin<VBE(on) 时三极管已处于截止状态, 𝑖𝐵=0iB=0。由输出特性曲线可以看到, 𝑖𝐶=0iC=0 时, 𝑣𝐶𝐸=𝑉𝐶𝐶vCE=VCC,电阻 𝑅𝐶RC 上没有压降。因此,三极管开关电路的输出为高电平 𝑉𝑜𝑢𝑡Vout,且 𝑉𝑜𝑢𝑡=𝑉𝐶𝐶Vout=VCC。

- 当 𝑣𝑖𝑛>𝑉𝐵𝐸(𝑜𝑛)vin>VBE(on) 时,有 𝑖𝐵iB 产生,同时有相应的集电极电流 𝑖𝐶iC 流过 𝑅𝐶RC 和三极管的输出回路,三极管开始进入放大区。根据折线化的输入特性可近似地求出基极电流为 𝑖𝐵=𝑣𝑖𝑛−𝑉𝐵𝐸(𝑜𝑛)𝑅𝐵iB=RBvin−VBE(on)。

- 若三极管的电流放大系数为 𝛽β,则得到 𝑖𝐶=𝛽𝑖𝐵iC=βiB。此时集电极电压为 𝑣𝐶𝐸=𝑉𝐶𝐶−𝑖𝐶𝑅𝐶vCE=VCC−iCRC。

在给出输出特性曲线的条件下,也可以用非线性电路的图解法,求出给定电路参数下 𝑣𝐶𝐸vCE 的具体数值。图解法的原理如图3.4.4所示。

图3.4.4 用图解法分析图3.4.3电路

- 当 𝑣𝑖𝑛vin 继续升高时 𝑖𝐵iB 增加, 𝑅𝐶RC 上的压降也随之增大。当 𝑅𝐶RC 上的压降接近电源电压 𝑉𝐶𝐶VCC 时,三极管上的压降将接近于零,三极管的 𝑣𝐶𝐸vCE 之间最后只有一个很小的饱和导通压降和很小的饱和导通内阻,三极管处于深度饱和状态,开关电路处于导通状态,输出端为低电平, 𝑣𝑜𝑢𝑡=𝑉𝐶𝐸(𝑠𝑎𝑡)≈0vout=VCE(sat)≈0。

若以 𝑉𝐶𝐸(𝑠𝑎𝑡)VCE(sat) 表示三极管深度饱和时的压降,以 𝑅𝐶𝐸(𝑠𝑎𝑡)RCE(sat) 表示深度饱和时的导通内阻,则由图3.4.4(a) 可求出深度饱和时三极管所需要的基极电流为 𝑖𝐵(𝑠𝑎𝑡)=𝑉𝐶𝐶−𝑉𝐶𝐸(𝑠𝑎𝑡)𝑅𝐵iB(sat)=RBVCC−VCE(sat)。

综上所述,只要合理地选择电路参数,保证当 𝑣𝑖𝑛vin 为低电平时 𝑖𝐵<𝐼𝐵(𝑠𝑎𝑡)iB<IB(sat),三极管工作在截止状态;而 𝑣𝑖𝑛vin 为高电平时 𝑖𝐵≥𝐼𝐵(𝑠𝑎𝑡)iB≥IB(sat),三极管工作在深度饱和状态,则三极管的 𝑣𝐶𝐸vCE 间就相当于一个受 𝑣𝑖𝑛vin 控制的开关。

四、三极管反相器的开关等效电路

根据以上的分析,我们可以将三极管开关状态下的等效电路画成如图3.4.5所示的形式。由于截止状态下的 𝑖𝐶iC 和 𝑣𝐶𝐸vCE 等于零,所以等效电路画成图(a)的形式。图(b)为饱和导通下的等效电路,图中的 𝑉𝐵𝐸(𝑜𝑛)VBE(on) 是发射结b-e的开启电压, 𝑉𝐶𝐸(𝑠𝑎𝑡)VCE(sat) 和 𝑅𝐶𝐸(𝑠𝑎𝑡)RCE(sat) 是c-e间的饱和导通压降和饱和导通内阻。在电源电压远大于 𝑉𝐵𝐸(𝑜𝑛)VBE(on) 且外接负载电阻远大于 𝑅𝐶𝐸(𝑠𝑎𝑡)RCE(sat) 的情况下,可以将饱和导通状态的等效电路简化为图(c)的形式。

图3.4.5 双极型三极管的开关等效电路

(a) 截止状态 (b) 饱和导通状态 (c) 简化等效电路

用双极型三极管的等效电路代替图3.4.3中的三极管,就得到了图3.4.6中的三极管反相器的等效电路。

图3.4.6 双极型三极管反相器的等效电路

(a) 反相器电路 (b) 输入低电平时的等效电路 (c) 输入高电平时的等效电路

由图可见,输入高电平时电源电压全部加在电阻 𝑅𝐶RC 上,电路的功耗很大;而输入低电平时三极管截止,电路的输出电阻很大(等于 𝑅𝐶RC)。因此,这个电路不宜作为集成电路的基本单元。在下一节里我们将会看到,在双极型的TTL集成电路中,反相器的输出端也采用了类似于CMOS反相器的结构,即使用另一只三极管代替 𝑅𝐶RC,并且保证无论输出为高电平还是低电平时,输出级两个串联的三极管当中,总是一个导通而另一个截止。

五、双极型三极管反相器的动态开关特性

在动态情况下,亦即三极管在截止与饱和导通两种状态间迅速转换时,三极管内部电荷的建立和消散都需要一定的时间,因而集电极电流 𝑖𝐶iC 的变化将滞后于输入电压 𝑣𝑖𝑛vin 的变化。在接成三极管开关电路以后,开关电路的输出电压 𝑣𝑜𝑢𝑡vout 的变化也必然滞后于输入电压 𝑣𝑖𝑛vin 的变化,如图3.4.7所示。这种滞后现象也可以用三极管的b-e间、c-e间都存在结电容效应来理解。

图3.4.7 双极型三极管的动态开关特性

例3.4.1

在图3.4.8所示的反相器电路中,已知 𝑉𝐶𝐶=5𝑉VCC=5V, 𝑅𝐵=4𝑘ΩRB=4kΩ, 𝑅𝐶=1.6𝑘ΩRC=1.6kΩ,二极管 𝐷1D1、𝐷2D2、𝐷3D3 的正向导通压降为0.7V,三极管发射结(b-e结)的开启电压 𝑉𝐵𝐸(𝑜𝑛)=0.7𝑉VBE(on)=0.7V。三极管的饱和导通压降和饱和导通内阻可以忽略不计。若输入信号的高、低电平分别为3.4V和0.2V,试计算:

- 三极管的电流放大系数 𝛽β 值应取为多少,才能保证输入高电平信号时三极管饱和导通?

- 输出的高、低电平值。

图3.4.8 例3.4.1 电路

解答:

- 根据式(3.4.4)可知,如果图3.4.8电路中的三极管工作在饱和状态,则可得:

𝛽=(𝑉𝐶𝐶−𝑉𝐵𝐸(𝑜𝑛))𝑅𝐵(𝑉𝐶𝐶−𝑉𝐷1−𝑉𝐷2−𝑉𝐵𝐸(𝑜𝑛))𝑅𝐶β=(VCC−VD1−VD2−VBE(on))RC(VCC−VBE(on))RB

由于输入高电平信号时二极管 𝐷1D1 截止,于是得到:

𝛽=(𝑉𝐶𝐶−𝑉𝐵𝐸(𝑜𝑛))𝑅𝐵(𝑉𝐶𝐶−𝑉𝐷2−𝑉𝐷3−𝑉𝐵𝐸(𝑜𝑛))𝑅𝐶=(5𝑉−0.7𝑉)×4𝑘Ω(5𝑉−0.7𝑉−0.7𝑉−0.7𝑉)×1.6𝑘Ω≈3.7β=(VCC−VD2−VD3−VBE(on))RC(VCC−VBE(on))RB=(5V−0.7V−0.7V−0.7V)×1.6kΩ(5V−0.7V)×4kΩ≈3.7

因此,三极管的电流放大系数必须大于3.7。

- 输入为低电平0.2V时,𝐷1D1 导通,P点为0.9V,三极管处于截止状态,故输出的高电平为 𝑉𝑜𝑢𝑡=𝑉𝐶𝐶=5𝑉Vout=VCC=5V。

输入为高电平3.4V时,三极管导通

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1387

1387

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?