目录

1 减法器

在数字电路中,除了有加法器还有减法器。减法器是一种执行减法运算的数字电路和逻辑器件,主要是用于计算两个二进制数之间的差。与加法器类似,减法器也可以分为半减器和全减器。

1.1 半减器

半减器是处理两个1位二进制的差,并且处理借位。半减器不能处理来自低位的借位,因此仅适用于最低位的减法。

考虑使用电路来实现一位减法,输入的两个二进制数A和B,其中A为被减数,B为减数。输出两个二进制数S和C,其中S表示A减去B的结果,C表示是否向高位借位。

- 当A=0,B=0时,S=0,C=0。

- 当A=0,B=1时,S=1,需要向高位借位,C=1。

- 当A=1,B=0时,S=1,C=0。

- 当A=1,B=1时,S=0,C=0。

根据上述内容可以列出真值表得:

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

根据真值表可以推出逻辑式为:

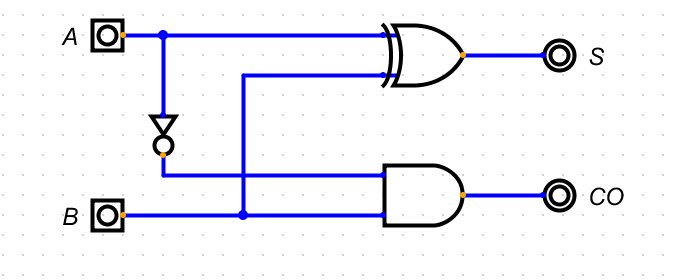

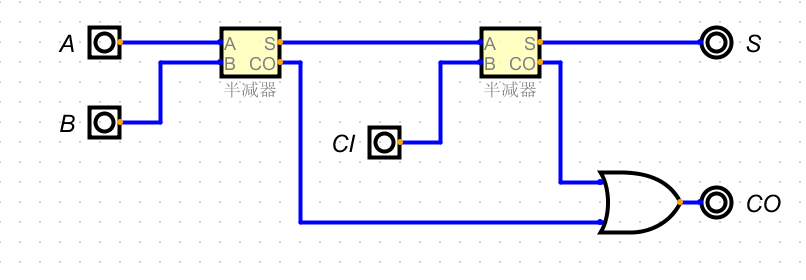

电路图如下所示:

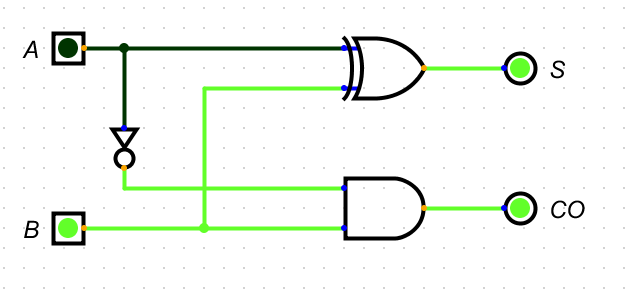

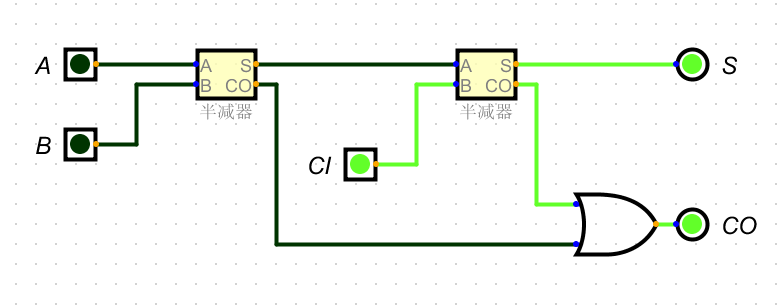

运行该电路,当A=0,B=1时,电路如下所示:

通过电路可以看到S为1,CO为1,符合半减器的真值表。

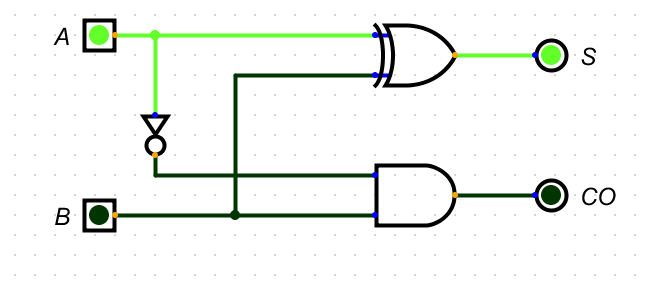

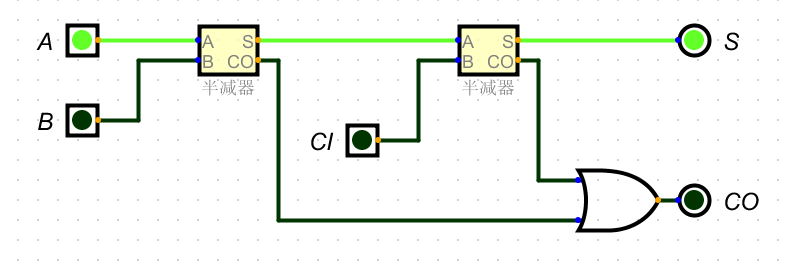

当A=1,B=0时,电路如下所示:

通过电路可以看到S为1,CO为0,符合半减器的真值表。

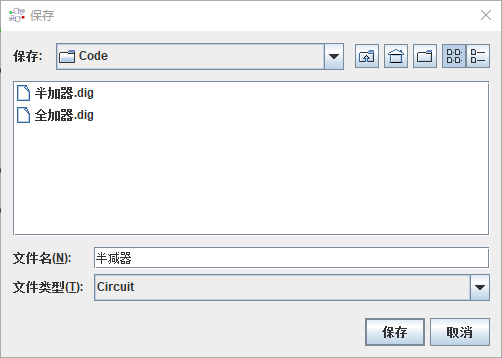

将其保存为半减器文件,可以作为全减器的子电路。如下所示:

1.2 全减器

全减器是计算两个二进制之间的差,并且考虑低位的借位。全减器输出减法的结果并且处理借位。

考虑如何使用电路来时实现一位全减器,输入了三个变量A、B、CI,其中A为被减数,B为减数,CI为来自低位的借位,输出三个变量,其中S为相减后结果,CO为是否要向高位借位。真值表如下所示:

| A | B | CI | S | CO |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

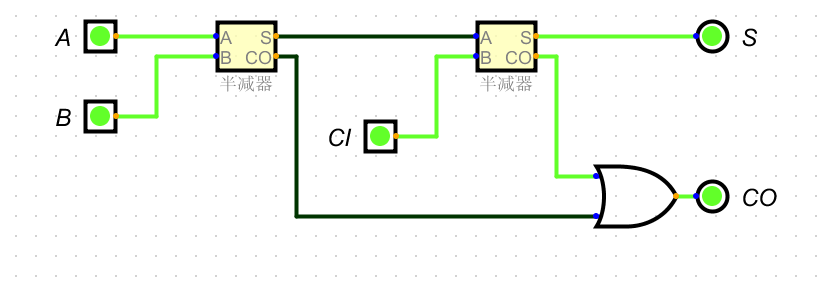

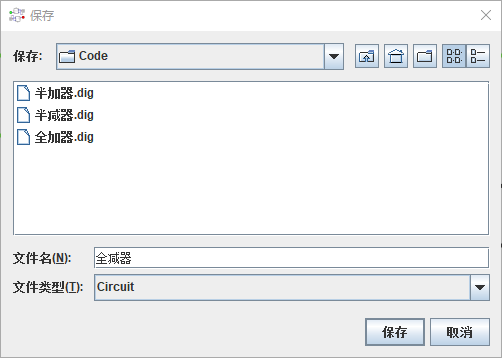

利用子电路半减器来实现全减器的电路图如下所示:

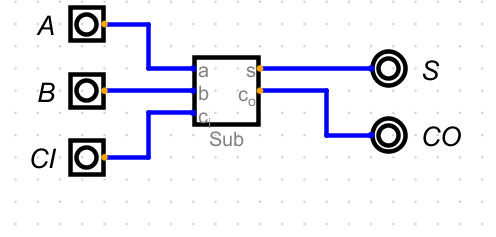

运行该电路,当A=0,B=0,有低位的借位,即CI=1,此时电路如下所示:

输出结果为S=1,CO=1,符合全减器运算结果。

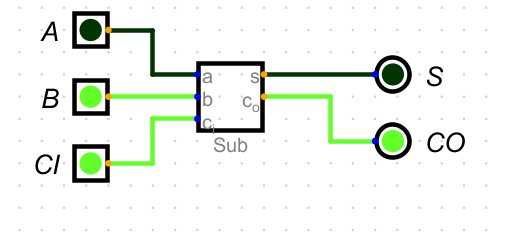

当A=1,B=0,无低位的借位,即CI=0,此时电路如下所示:

输出结果为S=1,CO=0,符合全减器运算结果。

当A=1,B=1,有低位的进位,即CI=1,此时电路如下所示:

输出结果为S=1,CO=1,符合全减器的运算结果。

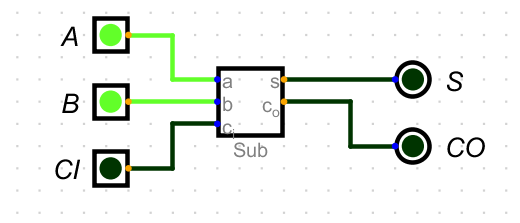

将其保存为全减器文件,可以作为多位减法器的子电路。如下所示:

另一种构建全减器的方式是直接使用Digital软件中的组件,点击组件选项栏中的运算器,之后点击运算器中减法器,然后将引脚A、B和CI分别连接输入,引脚S和CO连接输出。如下所示:

当A=0,B=1,有低位的借位,即CI=1,如下所示:

输出S为0,CO为1,符合减法器运算结果。

当A=1,B=1,无低位的借位,即CI=0,如下所示:

输出S为0,CO为0,符合减法器运算结果。

1.3 多位减法器

多位减法器是一种能够对多位二进制数进行减法运算的数字电路。

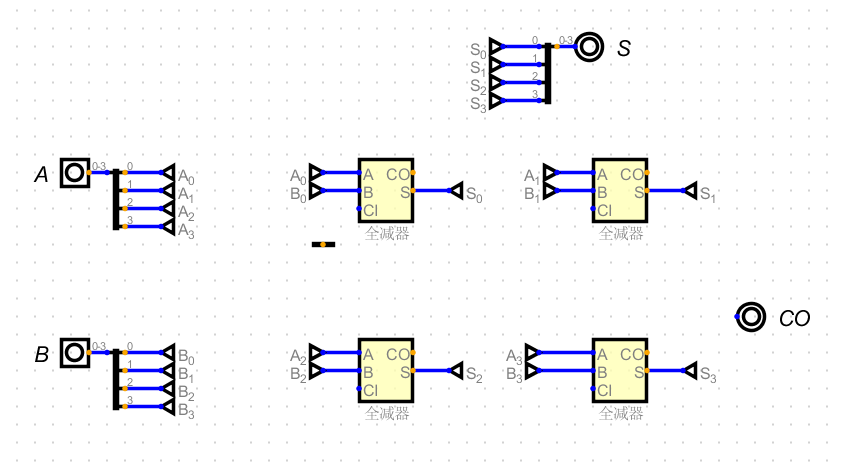

与多位加法器类似,可以使用Digital软件来实现多位减法器,选择全减器作为子选择器,输入变量A和B连接分裂器,分裂器连接四个隧道,输出变量S连接合并器,合并器连接隧道,如下所示为各个元器件示意图:

首个的全减器的引脚CI接地,将引脚CO接下一个全减器的引脚CI,依次连接,然后最后一个全减器的引脚CO接输出CO。

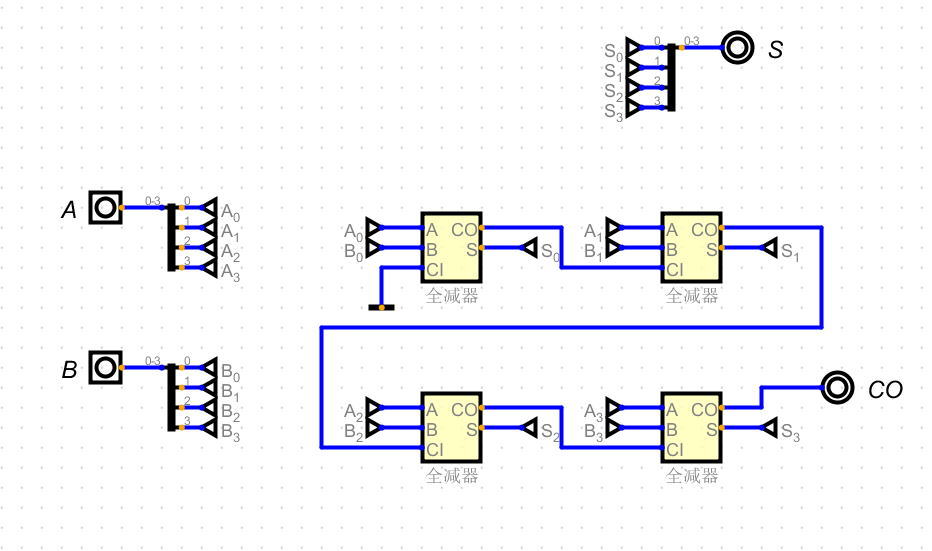

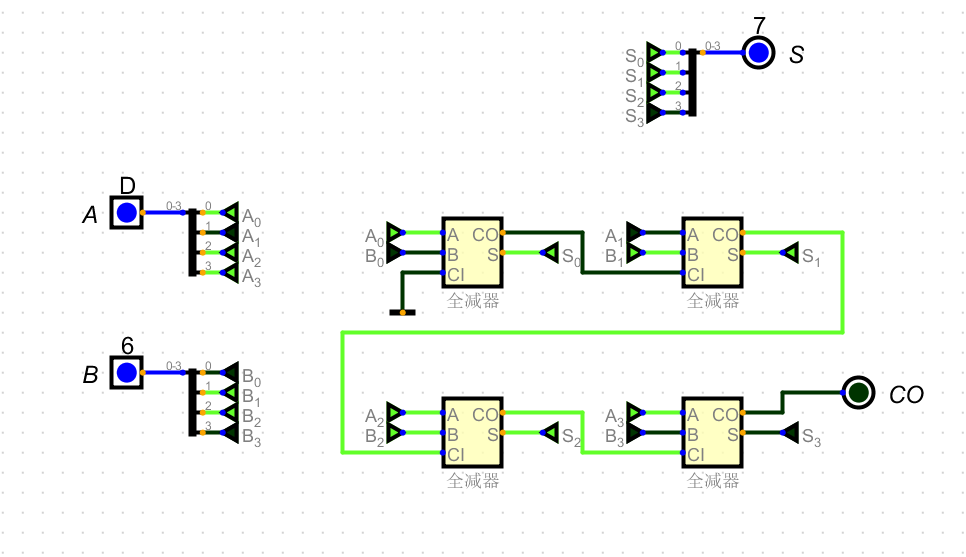

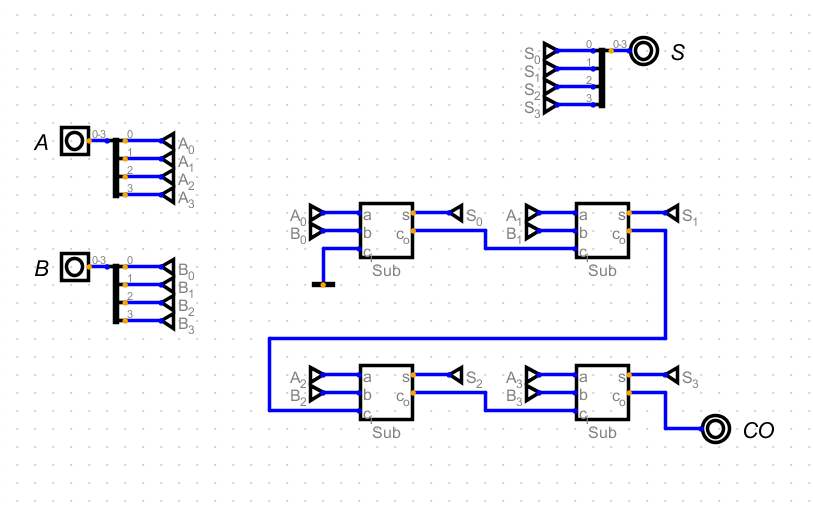

连接电路如下所示:

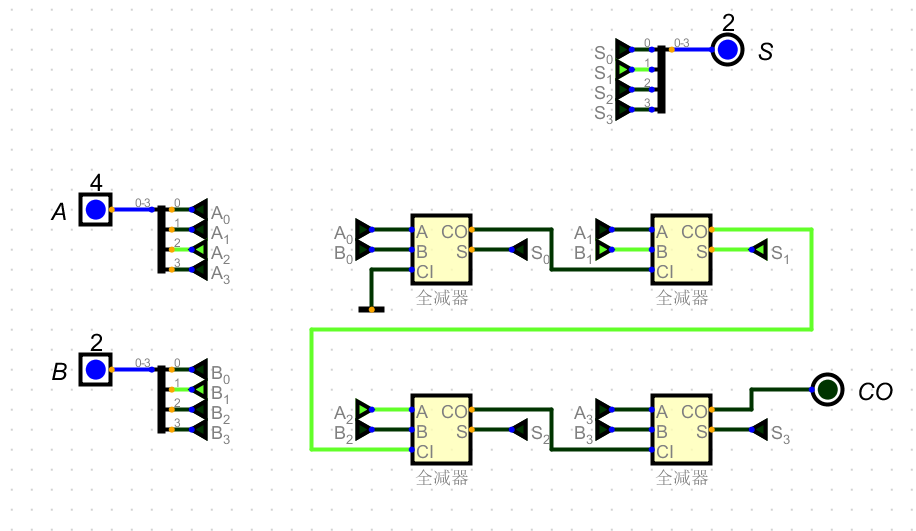

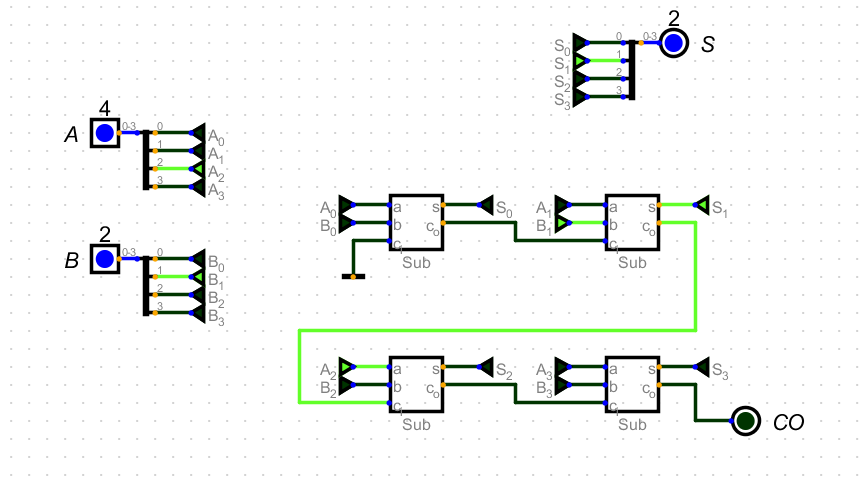

当A输入为4,B输入为2,电路如下所示:

可以看到S=2、CO=0,符合减法运算。

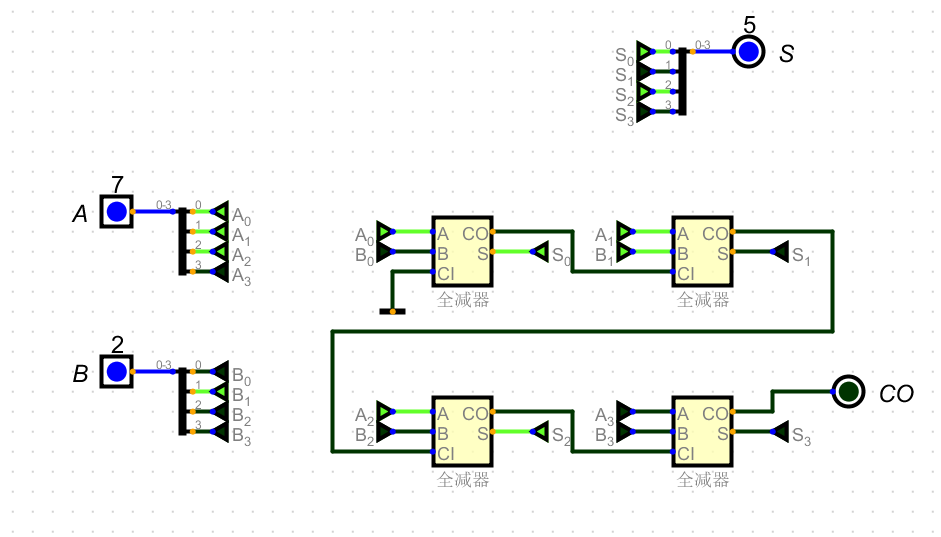

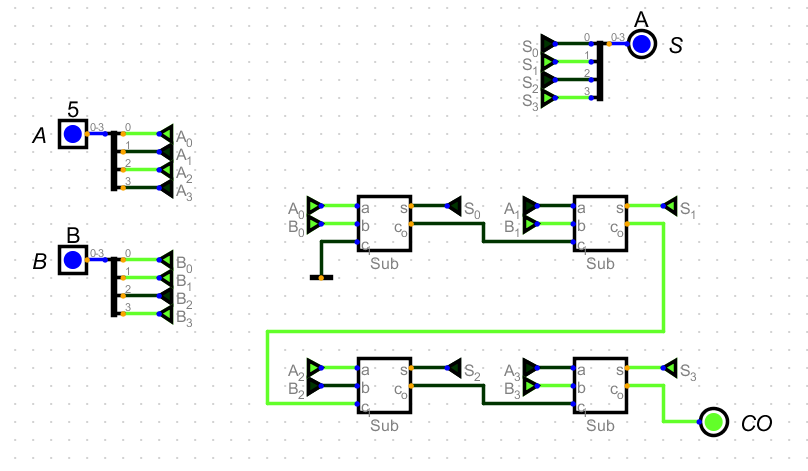

当A=7、B=2时,电路如下所示:

可以看到S=5,CO=0,符合减法运算。

当A=13(十六进制的D)、B=6时,电路如下所示:

可以看到S=7,CO=0,符合减法运算。

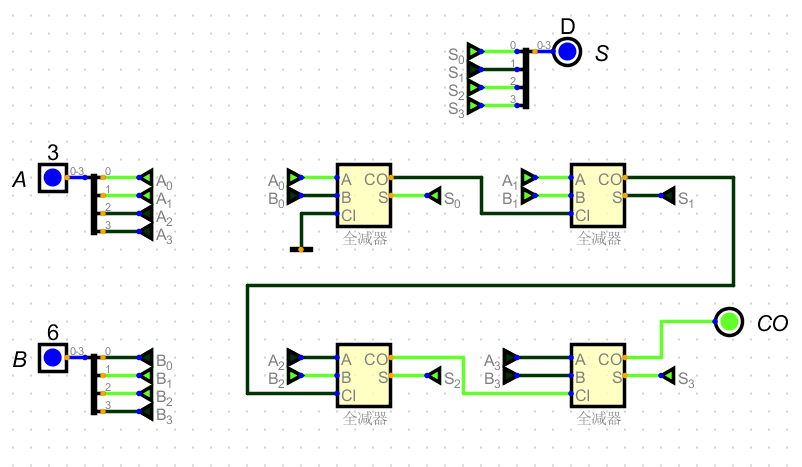

当A=3,B=6时,电路如下所示:

可以看到S=13(十六进制的D),CO=1,产生了向高位借位,符合减法运算。

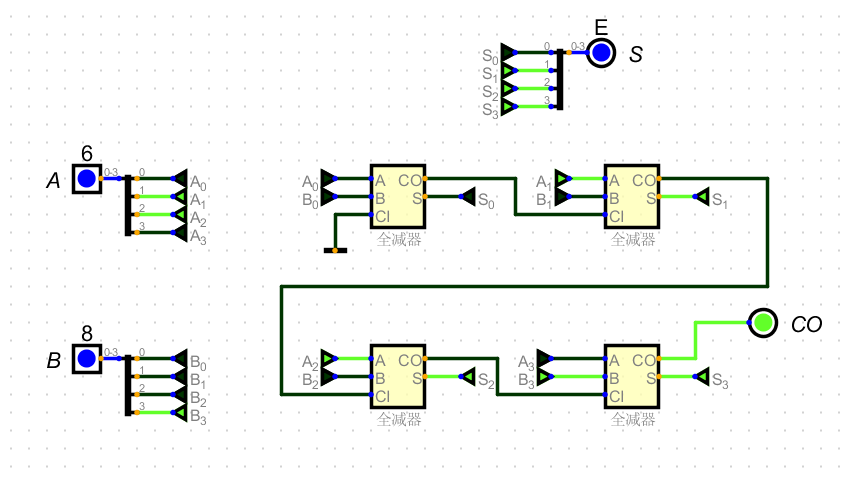

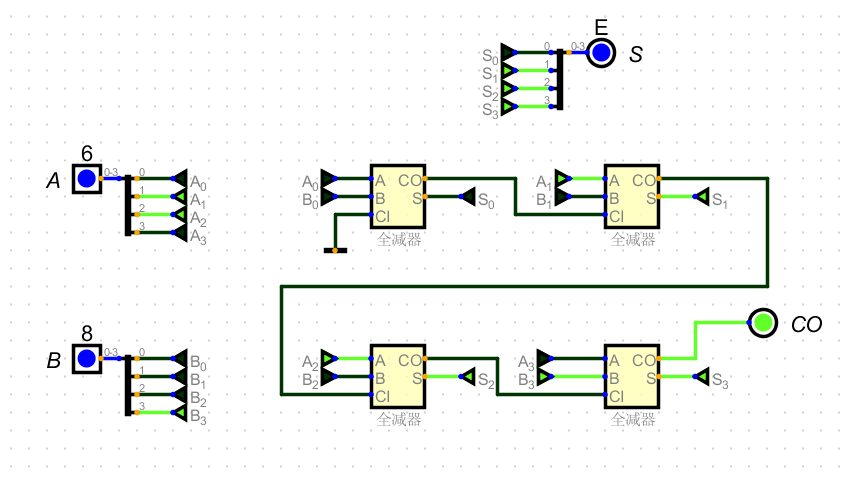

当A=6、B=8,电路如下所示:

可以看到S=14(十六进制的E),CO=1,产生了高位借位,符合减法运算。

当 A=10(十六进制的A)、B=14(十六进制的E)时,电路如下所示:

可以看到S=12(十六进制的C),CO=1,产生了高位借位,符合减法运算。

或者可以使用Digital软件中组件中的全减器来实现多位减法器。打开Digital软件,点击组件选项栏中的运算器,然后点击运算器选项栏中的减法器,最终电路如下所示:

运行该电路,当A=4,B=2时,电路的输出情况如下所示:

可以看到S=2,CO=0,符合减法运算结果。

当A=5、B=11(十六进制的B),电路如下所示:

可以看到S=10(十六进制的A),CO=1,产生了高位借位,符合减法结果。

1169

1169

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?