一、实验目的

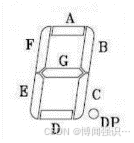

二、实验原理1、数码管简介:数码管是很常见的一种显示设备,一般分为七段数码管和八段数码管,两者区别就在于八段数码管比七段数码管多了一个“点”。我们采用的数码管为 6 位一体的八段数码管,数码管的段结构图 1 所示 本实验我们使用的是共阳极数码管,当某一字段对应的引脚为低电平时,相应字段就点亮,当某一字段对应的引脚为高电平时,相应字段就不亮。六位一体数码管是属于动态显示,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。 2、引脚设置:六位一体数码管的相同的段都接在了一起,一共是 8 个引脚,然后加上 6 个控制信号引脚,一共是 14 个引脚,其中 DIG[0..7]是对应数码管的 A,B,C,D,E,F,G,H(即点DP);当某一字段对应的引脚为低电平时,相应字段发亮,当某一字段为高电平时,相应字段不亮。SEL[0..5]是6个数码管的六个控制引脚,也是低电平有效,当控制引脚为低电平时,对应的数码管有了供电电压,这样数码管才能点亮,否则无论数码管的段如何变化,也不能点亮对应的数码管。输出信号的7位分别接共阴数码管的七个段,高位在左,低位在右。例如:当7位输出为“1000000”时,数码管G段为高电平,所以G段不亮,其余均亮,所以显示数字“0”。SEL[0..5]是六个数码管的六个控制引脚,也是低电平有效,当控制引脚为低电平时,对应的数码管有了供电电压,这样数码管才能点亮,否则无论数码管的段如何变化,也不能点亮对应的数码管。

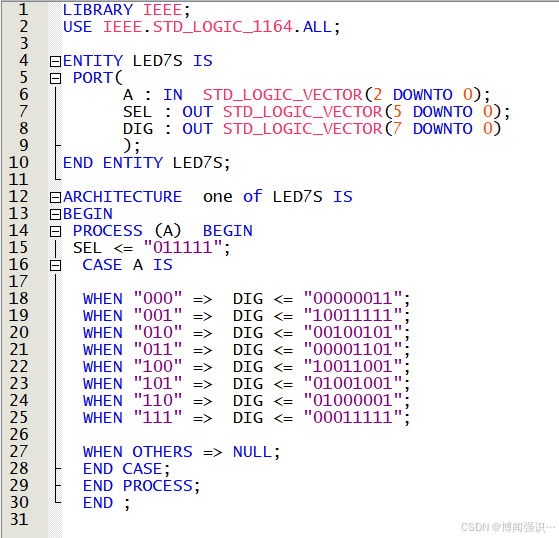

图1 要显示数字0-7,需要7位输出,但由于需要接控制引脚,而不需要接数码管的H(即点DP)位,所以输出需要8位。输出信号的前七位从左至右为7段数码管的7个段,输出信号从左至右最后一位为控制引脚。开发板板载了 4 个独立按键,3 个用户按键(KEY1~KEY3),1 个功能按键(RESET)。按键都为低电平按下为低电平(0),松开为高电平(1)。4位输入信号接开发板的4个控制按键。功能按键(RESET)控制是否显示数字,3 个用户按键(KEY1~KEY3)控制输出显示的数字大小。 2、程序设计如下图所示。

图2 数码管程序设计 3、输入码、输出码对应的数据

三、实验器材1.计算机:配置为P4 CPU128M内存 2.实验软件:Quartus II(Quartus Prime 13.1) Lite Edition 3.开发板: ALINX AX301,芯片为Cyclone IV,型号为EP4CE6F17C8以及配套的AX301用户手册 4.电源线、烧录线等 四、实验内容和步骤

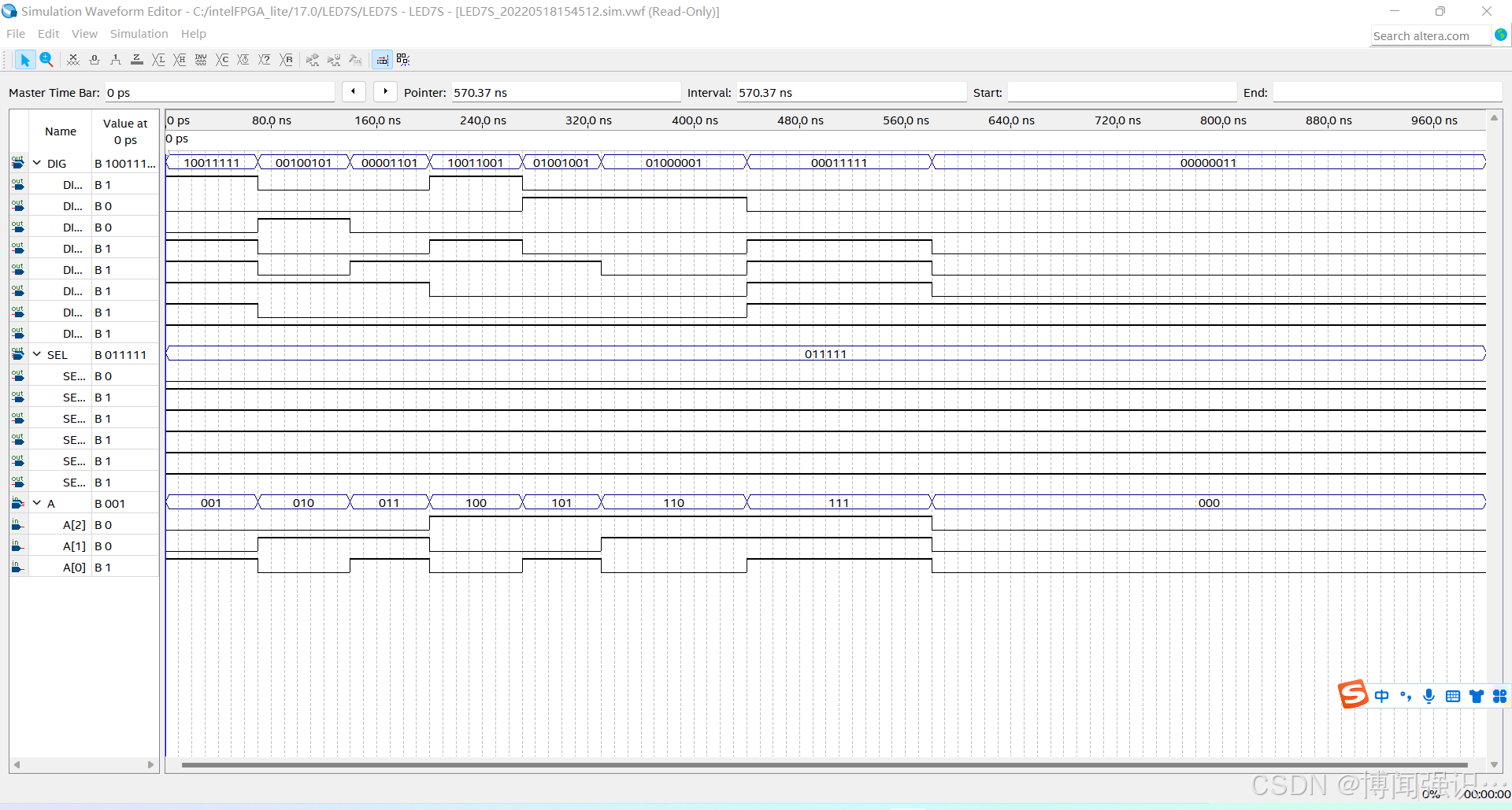

3.进行编译。若编译成功,则可以对其进行功能和时序性质进行仿真测试;若编译不成功,则需要检查和纠正错误,修改程序,再次进行编译,直至成功。 4.仿真测试。打开波形编辑器→设置仿真时间区域→波形文件存盘→将工程的所有端口信号节点选入波形编译器→仿真器参数设置→启动仿真器→观察仿真结果。 5.引脚锁定。输入端A信号分别接开发板的三个控制按键key引脚M15、M16和E16,输出信号接入数码管引脚SEL和DIG。 6.编译文件下载和硬件测试。操作开发板,查看结果与预期是否相符,若符合则通过;若不符合则检查代码与管脚,重复上述步骤,直至结果与预期相符合。 五、实验数据与处理1、波形仿真图

2、硬件测试结果图 本次结果共显示0-7八个数字,因篇幅限制,我们将3个结果1,3,7分别展示如下:

六、问题讨论1、代码编译时,常见的报错原因主要包括结构体名称与工程名称不符、使用if语句时未在条件语句结束处键入end if、数组位数不匹配等。根据编译的报错结果,双击错误即可跳转至代码出错处,根据提示修改即可。 波形仿真时常见错误原因是在多次进行波形仿真时未删除或覆盖上一次的波形仿真文件。因此我们要删除之前的波形仿真文件,或者将其覆盖。 |

电子设计自动化实验报告一:数码管显示电路的设计

于 2024-11-18 15:35:03 首次发布

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?