<think>嗯,用户想设计存储器扩展模块,把两块16x4的存储器扩展成16x8,然后再用两块16x8扩展到32x8,最后连接到CPU。这涉及到位扩展和字扩展,对吧?首先,我得回忆一下存储器扩展的基本方法。

位扩展应该是增加数据位宽。比如16x4的存储,两块组合起来,每块的地址相同,但数据位拼在一起,变成8位。这样,每个地址可以存储8位数据,而容量还是16个字。这时候需要把两块存储器的地址线连在一起,数据线合并,高位和低位分别接不同的存储块。比如,第一块处理低4位,第二块处理高4位,这样组合起来就是8位了。同时,CPU的访问信号要同时使能这两个存储块,所以片选信号应该连在一起,或者通过控制逻辑让它们同时有效。

然后是字扩展,也就是增加地址范围。从16x8扩展到32x8,地址线需要增加一位。比如原来的地址是4位(16=2^4),现在需要5位地址。这时候可以将最高位地址作为片选信号。当最高位是0时,选中的是第一个16x8的块;当是1时,选中第二个。这样,地址空间就从0x0000到0x001F变成了32个字。这时候,CPU的地址线需要连接到两个存储模块,并根据最高位选择哪一个模块被激活。数据线则可能需要三态门或者多路选择器来处理,确保同一时间只有一个模块输出数据。

接下来要考虑如何用Verilog实现这些扩展。对于位扩展,两块16x4的存储器实例,地址输入相同,数据输出拼接。比如,存储器的输出是4位,合并成8位。写操作时,CPU的数据总线分成高低4位,分别写入两个存储器。读的时候,两个存储器的数据合并输出。

字扩展的话,两块16x8的存储器,地址线使用低4位,最高位作为片选。当CPU的地址最高位是0,选中第一个模块;是1则选中第二个。可能需要一个地址解码器,根据地址的高位生成片选信号。同时,数据总线需要处理两个模块的输出,可能用三态缓冲器,当片选有效时输出数据,否则高阻态,避免冲突。

然后要考虑与CPU的连接。CPU的地址总线、数据总线和控制信号(如读写使能)需要连接到存储模块。对于位扩展后的16x8模块,地址线是4位,数据线8位。字扩展后的32x8模块,地址线5位,数据线8位。控制信号需要正确连接到存储器的读写端口,并且片选信号由地址解码产生。

在Verilog代码方面,位扩展部分需要实例化两个16x4的RAM模块,地址输入相同,数据输出合并。写使能可能需要同时有效,或者根据字节使能分开,但用户的问题可能只需要简单的扩展,所以同时使能即可。字扩展部分则需要两个16x8的模块,地址的低4位共用,最高位决定片选。读数据时,根据片选信号选择哪个模块的数据输出。

可能还需要考虑时序问题,比如存储器的访问时间是否满足CPU的要求。但用户可能暂时不需要考虑这么深入,先实现基本功能。

然后,用户需要具体的代码实现。对于16x4到16x8的位扩展,代码里会有两个RAM实例,地址相同,数据输出合并。例如:

module RAM16x8 (

input [3:0] addr,

input [7:0] din,

input we, clk,

output [7:0] dout

);

wire [3:0] dout_low, dout_high;

RAM16x4 ram_low (

.addr(addr),

.din(din[3:0]),

.we(we),

.clk(clk),

.dout(dout_low)

);

RAM16x4 ram_high (

.addr(addr),

.din(din[7:4]),

.we(we),

.clk(clk),

.dout(dout_high)

);

assign dout = {dout_high, dout_low};

endmodule

这里,din的低4位和高4位分别写入两个RAM,输出时合并。可能需要将we同时连接到两个RAM,或者根据字节使能分开,但用户的问题可能只需要整体写入,所以同时使能。

对于字扩展,从16x8到32x8,需要两个16x8的RAM,地址的高位作为片选:

module RAM32x8 (

input [4:0] addr,

input [7:0] din,

input we, clk,

output [7:0] dout

);

wire sel = addr[4];

wire [3:0] lower_addr = addr[3:0];

wire [7:0] dout0, dout1;

RAM16x8 ram0 (

.addr(lower_addr),

.din(din),

.we(we & ~sel),

.clk(clk),

.dout(dout0)

);

RAM16x8 ram1 (

.addr(lower_addr),

.din(din),

.we(we & sel),

.clk(clk),

.dout(dout1)

);

assign dout = sel ? dout1 : dout0;

endmodule

这里,地址的最高位sel决定使用哪个RAM模块。写使能需要根据sel来分别控制,读的时候根据sel选择输出哪个模块的数据。

然后,连接到CPU的话,需要将CPU的地址线、数据线、控制信号连接到这些存储器模块。比如,CPU的地址总线在访问16x8时用4位,访问32x8时用5位。可能需要多路选择器或地址解码逻辑,但用户的问题可能希望直接扩展,所以按上述模块连接即可。

需要注意的是,存储器的读写时序是否与CPU的时钟同步,比如是否在时钟上升沿触发读写操作。这需要根据CPU的设计来调整存储器的接口。

用户提供的引用中,提到了符号扩展模块EXT16T32,可能类似地,存储器的扩展也需要类似的模块,但这里主要是存储器的位和字扩展。另外,引用中的MUX2X32可能用于选择不同的扩展方式,这里在字扩展时也需要多路选择器来选择不同存储块的数据输出。

总结一下,步骤应该是:

1. 位扩展:两块16x4合并为16x8,地址并联,数据合并。

2. 字扩展:两块16x8合并为32x8,地址最高位作为片选,地址低4位共用。

3. Verilog代码实现这两个扩展模块。

4. 连接CPU时,地址线、数据线、控制信号正确连接,确保读写操作正确选择存储模块。

可能用户还希望看到模块的连接方式,比如CPU如何生成地址、数据,以及控制信号如何连接到存储器的we和sel等信号。例如,CPU的地址总线在字扩展时是5位,低4位连接到存储器的地址输入,最高位用于生成片选信号。数据总线8位直接连接存储器的din和dout,we由CPU的写使能信号控制。

最后,需要测试这些模块是否正确工作,比如写入不同的地址,读取是否正确,特别是在字扩展时,地址切换是否选通正确的存储块。</think>### 存储器扩展设计实现

#### 一、存储器扩展原理

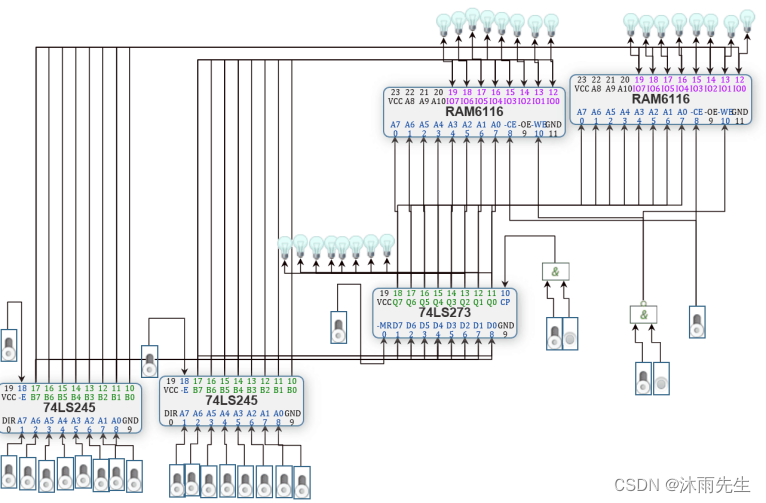

1. **位扩展(16×4 → 16×8)**

将两块16×4存储器并联,通过合并数据位宽实现存储容量翻倍。每个地址存储8位数据(低4位和高4位分别由两块存储器提供)[^1]。

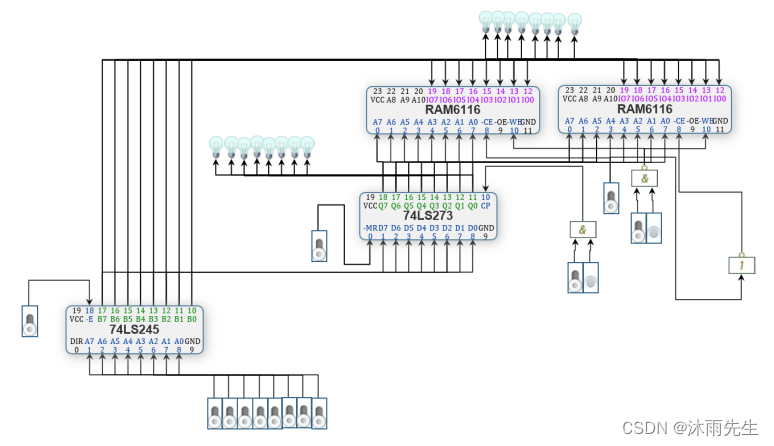

2. **字扩展(16×8 → 32×8)**

通过增加地址范围实现存储容量扩展,使用地址最高位控制片选信号(`sel`)选择不同的存储模块[^2]。

#### 二、Verilog代码实现

##### 1. 位扩展模块(16×4 → 16×8)

```verilog

module RAM16x8 (

input [3:0] addr, // 4位地址线

input [7:0] din, // 8位输入数据

input we, clk, // 写使能、时钟

output [7:0] dout // 8位输出数据

);

wire [3:0] dout_low, dout_high;

// 低4位存储单元

RAM16x4 ram_low (

.addr(addr),

.din(din[3:0]),

.we(we),

.clk(clk),

.dout(dout_low)

);

// 高4位存储单元

RAM16x4 ram_high (

.addr(addr),

.din(din[7:4]),

.we(we),

.clk(clk),

.dout(dout_high)

);

assign dout = {dout_high, dout_low}; // 合并输出

endmodule

```

##### 2. 字扩展模块(16×8 → 32×8)

```verilog

module RAM32x8 (

input [4:0] addr, // 5位地址线

input [7:0] din,

input we, clk,

output [7:0] dout

);

wire sel = addr[4]; // 最高位作为片选信号

wire [3:0] lower_addr = addr[3:0]; // 低4位地址

wire [7:0] dout0, dout1;

// 第一块16×8存储器(地址0x00~0x0F)

RAM16x8 ram0 (

.addr(lower_addr),

.din(din),

.we(we & ~sel), // 片选为0时使能

.clk(clk),

.dout(dout0)

);

// 第二块16×8存储器(地址0x10~0x1F)

RAM16x8 ram1 (

.addr(lower_addr),

.din(din),

.we(we & sel), // 片选为1时使能

.clk(clk),

.dout(dout1)

);

assign dout = sel ? dout1 : dout0; // 数据输出选择

endmodule

```

#### 三、CPU连接设计

1. **信号连接**

- **地址线**:字扩展后地址线扩展为5位(`addr[4:0]`)

- **数据线**:8位双向数据总线(`din/dout`)

- **控制信号**:写使能(`we`)直接连接CPU控制单元[^3]

2. **时序同步**

存储器操作需与CPU时钟同步,在时钟上升沿执行读写操作:

```verilog

module CPU (

input clk,

output [4:0] addr,

inout [7:0] data,

output we

);

// 数据总线三态控制

assign data = (we) ? 8'bz : internal_data;

// 存储控制器实例化

RAM32x8 memory (

.addr(addr),

.din(data),

.we(we),

.clk(clk),

.dout(data)

);

endmodule

```

#### 四、关键设计要点

1. **位扩展**:通过数据总线合并实现位宽翻倍,需保证两片存储器**同时读写**。

2. **字扩展**:利用地址最高位实现片选逻辑,需注意地址译码的**时序一致性**。

3. **总线冲突**:使用三态门控制数据总线方向,避免读写冲突[^4]。

---

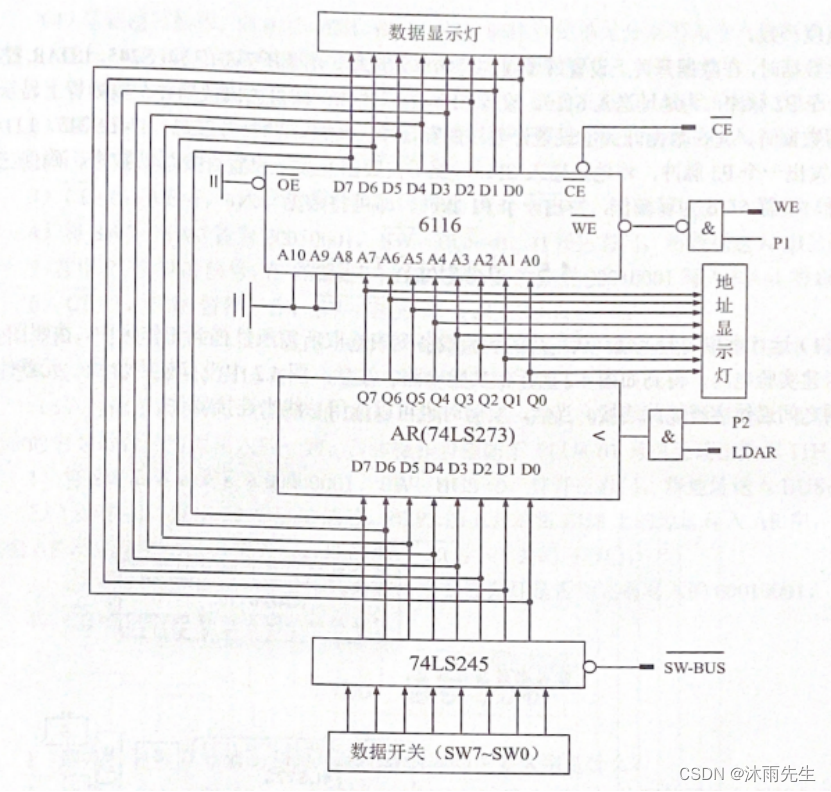

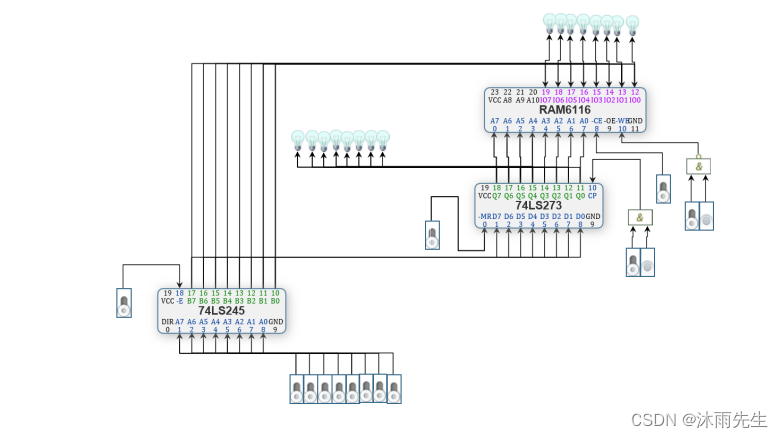

本文详细介绍了半导体静态存储器RAM的工作原理、实验要求,包括如何设置地址和数据、进行写入和读取操作。同时,文章涵盖了实验步骤,如预设置电路、写入和读取数据,以及思考与分析部分中对存储器扩展的探讨。

本文详细介绍了半导体静态存储器RAM的工作原理、实验要求,包括如何设置地址和数据、进行写入和读取操作。同时,文章涵盖了实验步骤,如预设置电路、写入和读取数据,以及思考与分析部分中对存储器扩展的探讨。

4730

4730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?