VHDL设计要求:

在文本编辑器中使用 VHDL 语言设计一个 T 触发器,具有反 向输出端。命名为***dff.vhd,仿真验证。然后在一个新的实体 中将上述 T 触发器定义成一个元件,通过元件例化语句将其级联 成一个 64 分频的同步分频器,命名为***fp.vhd,仿真验证。

题目分析:

题目要求需要先设计一个T触发器,在设计并验证T触发器的功能正确之后,需要使用元件例化语句来构成一个64分频的分频器

元件例化语句介绍:

一部分是元件声明部分,通常放在结构体声明部分;另一 部 分是元件例化部分,放在结构体描述部分。

a.元件声明 component 元件名 is port(例化元件端口名表); end component 元件名;

b.元件例化 例化名:元件名 port map(元件端口=>当前实体端口,...,元件端口=>当前 实体 端口); 上述端口映射方式称为名称关联,即根据名称将相应的端口 对应起来。 当顶层元件的端口、信号或参数排列顺序完全一致时,可以 这样写: port map(当前实体端口 1,...,当前实体端口 n);

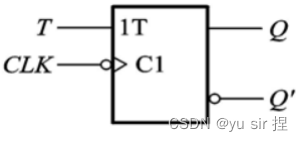

T触发器介绍:

T 触发器是在数字电路中,凡在 CP 时钟脉冲控制下,根据输 入信号 T 取值的不同,具有保持和翻转功能的触发器,即当 T=0 时 能保持状态不变,当 T=1 时一定翻转的电路。

下面介绍代码:

T触发器vhdl代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY Tdeco IS

port (

T,CLK: in std_logic;------------------T触发器的输入端口

Q,QB:buffer std_logic-----------------输出端与反向输出端

);

end entity;

architecture beh of Tdeco is

begin

process (CLK) IS

begin

if (CLK'event and CLK='1' )then----------运行条件

if(T='1') then

QB<=Q;

Q<=NOT(Q);

else

Q<=Q;

QB<=NOT(Q);

end if;

end if;

end process;

end beh;T触发器构成的64分频器代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY byldff IS

port (

TI,CLKI: in std_logic;------------------64分频器的输入

OUTA:buffer std_logic-----------------输出端

);

end entity;

architecture beh of byldff is

------------------------------------------t触发器

component Tdeco

port (

T,CLK: in std_logic;------------------T触发器的输入端口

Q,QB:buffer std_logic-----------------输出端与反向输出端

);

end component;

-------------------------------------------程序中中间信号的声明

SIGNAL Q1,Q2,Q3,Q4,Q5 : STD_logic;

begin

-------------------------------------------元件调用

T1:Tdeco port map(T=>TI,CLK=>CLKI,Q=>Q1);

T2:Tdeco port map(T=>TI,CLK=>Q1,Q=>Q2);

T3:Tdeco port map(T=>TI,CLK=>Q2,Q=>Q3);

T4:Tdeco port map(T=>TI,CLK=>Q3,Q=>Q4);

T5:Tdeco port map(T=>TI,CLK=>Q4,Q=>Q5);

T6:Tdeco port map(T=>TI,CLK=>Q5,Q=>OUTA);

end beh;PDF格式的图文步骤详解以及源文件在我主页下载

1084

1084

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?