简单介绍DDS :

这里具体可参考AMD_FPGA官方文档:References • Vitis High-Level Synthesis User Guide (UG1399) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

DDS Compiler LogiCORE IP Product Guide(PG141)

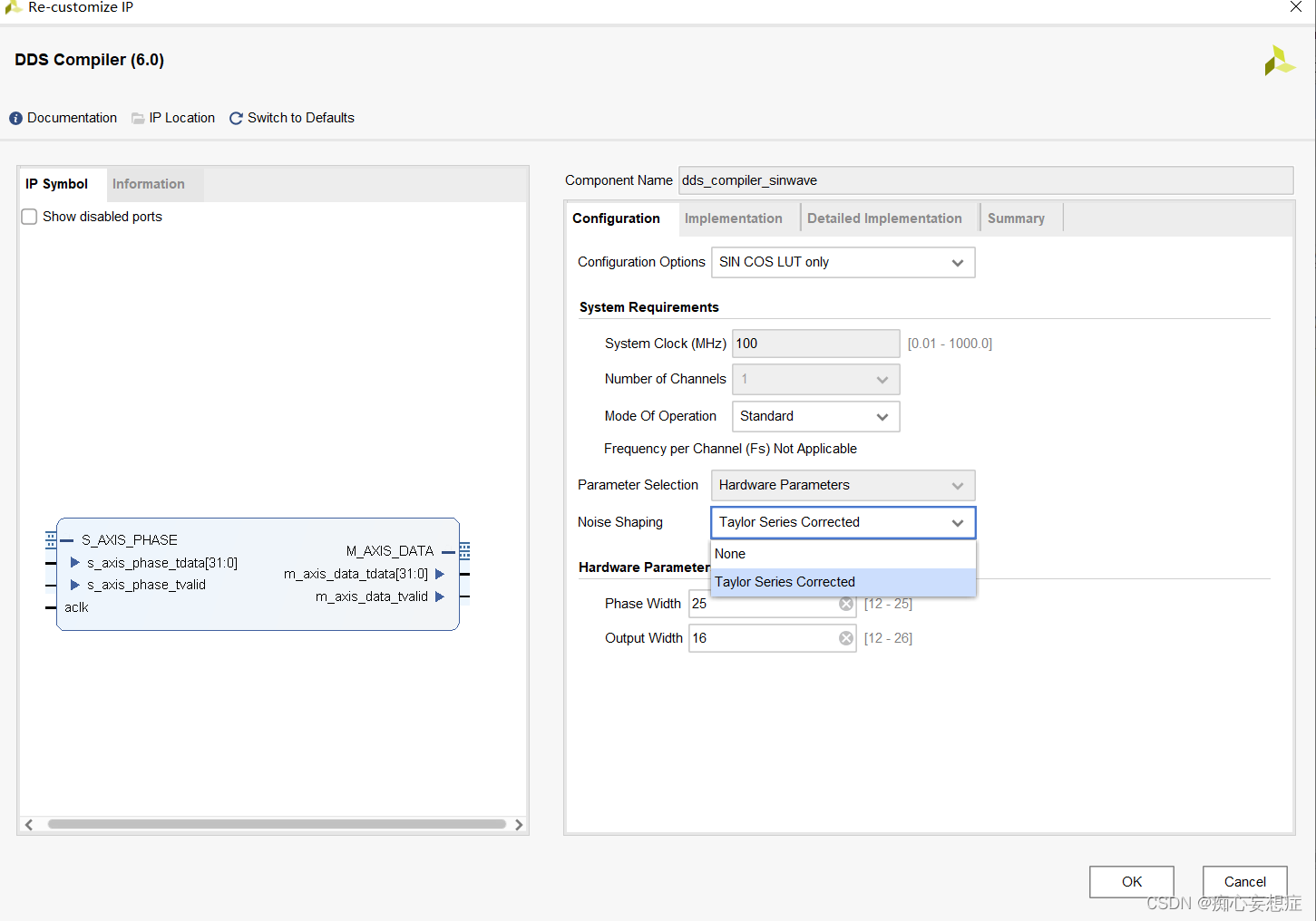

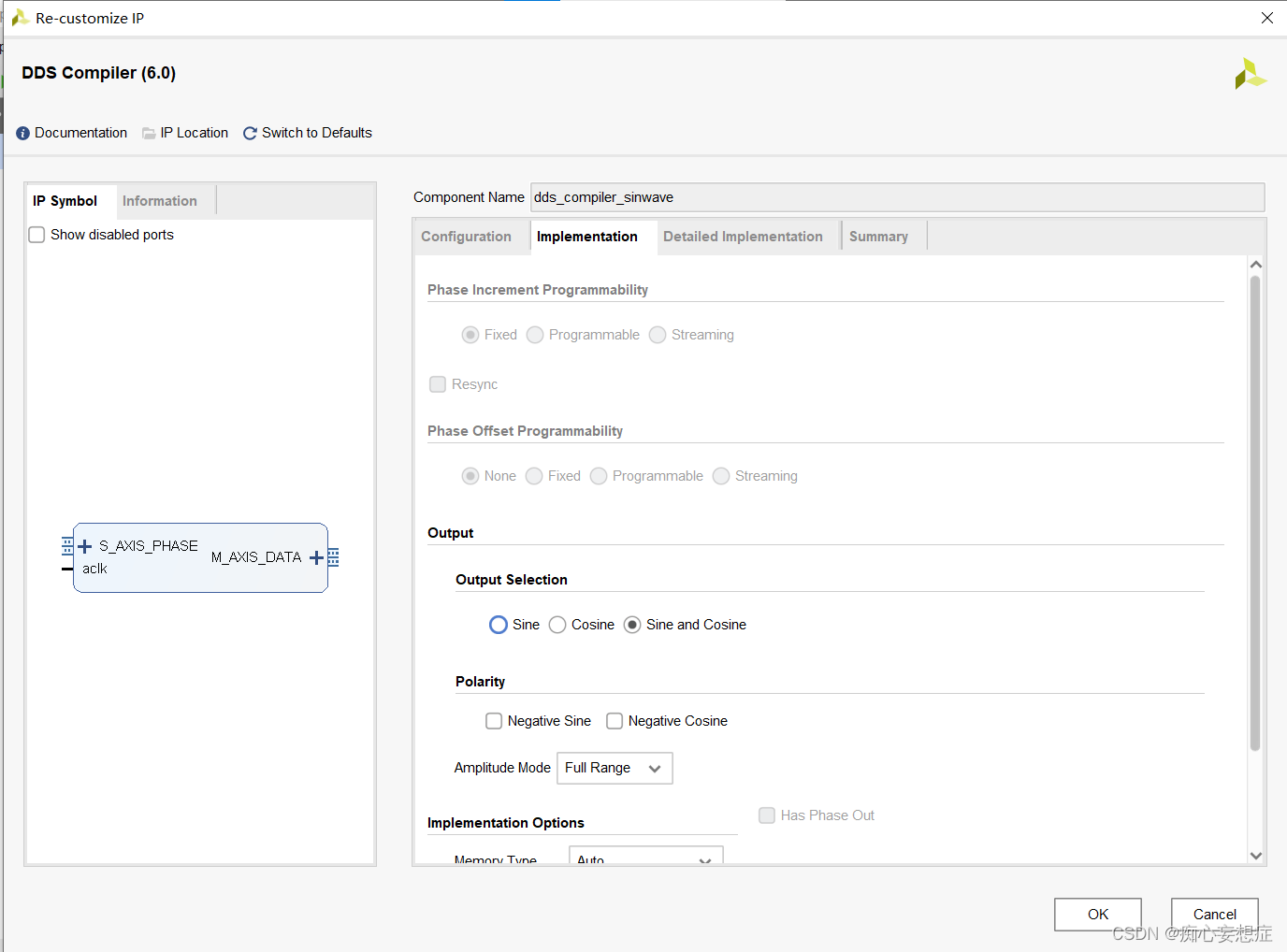

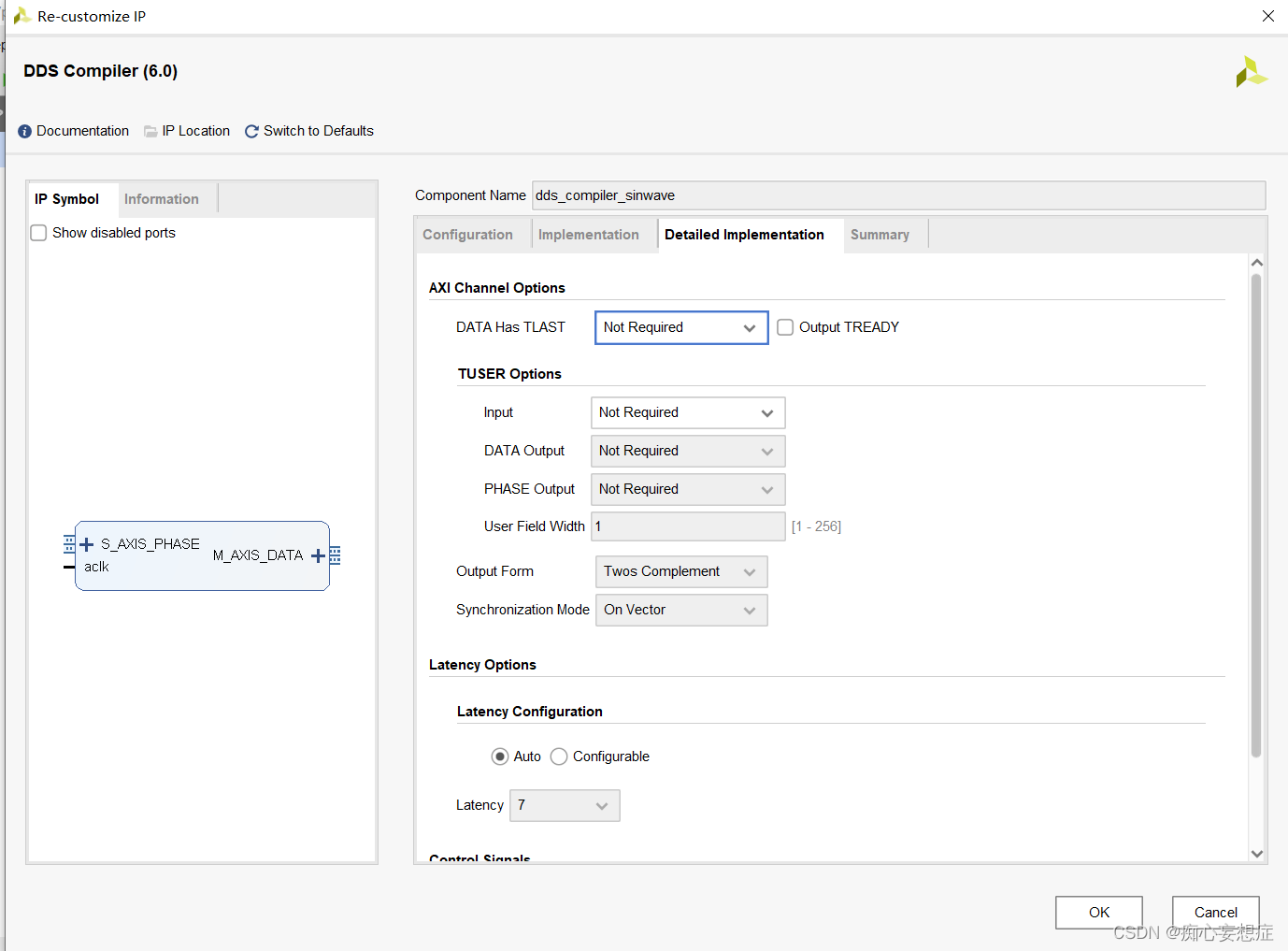

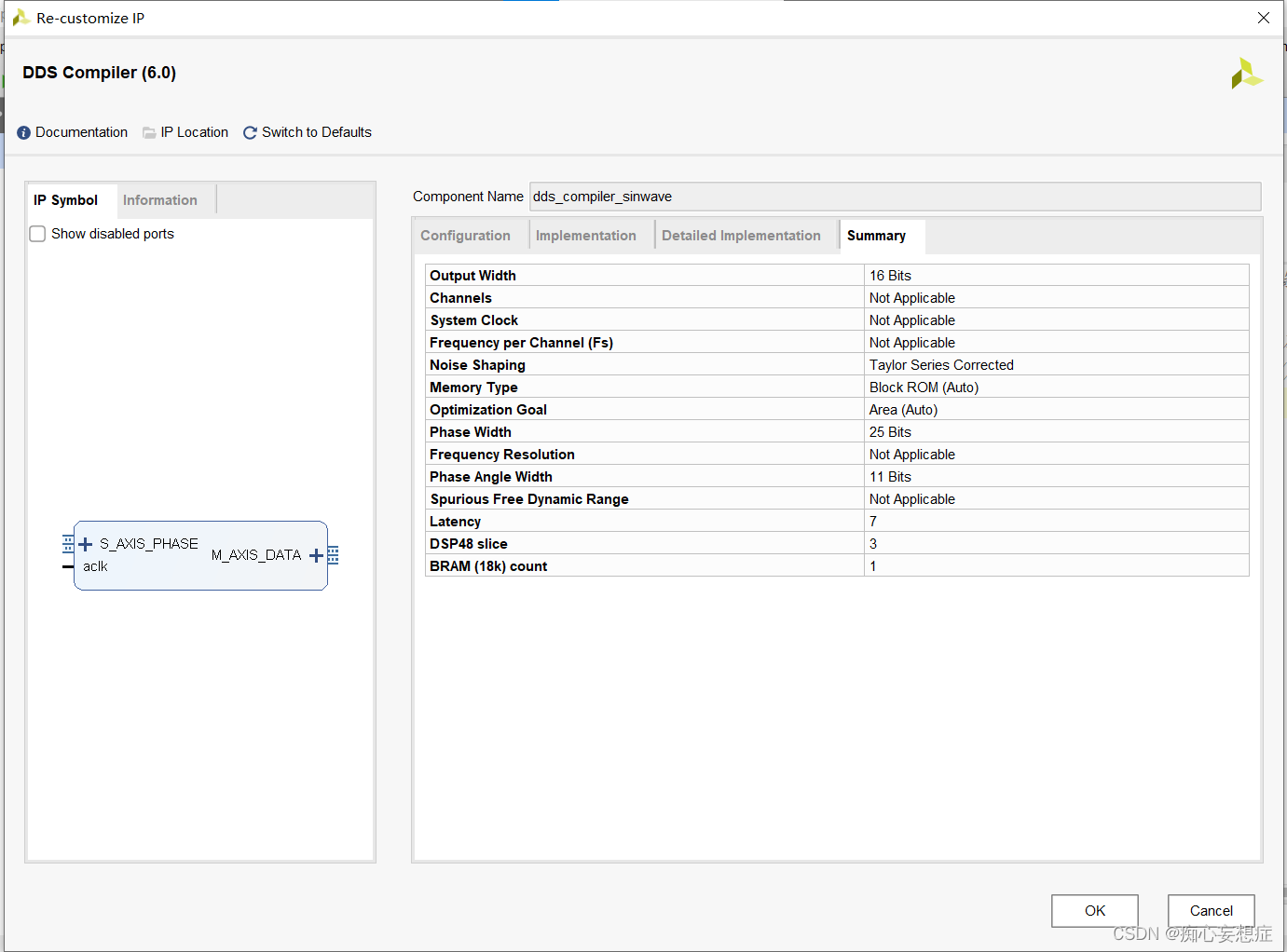

IP核参数设置如下:

代码如下:

功能模块代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/08/16 22:21:23

// Design Name:

// Module Name: SinWave_dds

// Project Name:

// Target Devices:

// Tool Versions:

// Description: 利用DDS产生任意频率的正余弦波

// Dependencies:

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

// fout=(f_word*fclk)/2^N,fout为输出频率,fclk为系统时钟频率,N为相位累加器地址位宽

// f_word = f_out*2^N/f_clk

// POFF = 4*2^32/100 = 171798692;其中4为所需产生频率,32为相位累加器地址的位宽,100为时钟频率

//

module SinWave_dds # (

parameter POFF = 32'd171798692

)(

input aclk,

input rst_n,

output data_valid,

output [31:0] data

);

// reg define

reg [31:0] phase_add ;

// wire define

wire [15:0] sin_data;

wire [15:0] cos_data;

always @(posedge aclk) begin

if(!rst_n) begin

phase_add <=32'd0;

end

else begin

phase_add<=phase_add + POFF;

end

end

assign sin_data = data[31:16];

assign cos_data = data[15:0 ];

dds_compiler_sinwave u_dds_inst(

.aclk(aclk), // input wire aclk

.s_axis_phase_tvalid(1'b1), // input wire s_axis_phase_tvalid

.s_axis_phase_tdata({7'd0,phase_add[31:7]}), // input wire [31 : 0] s_axis_phase_tdata

.m_axis_data_tvalid(data_valid), // output wire m_axis_data_tvalid

.m_axis_data_tdata(data) // output wire [31 : 0] m_axis_data_tdata

);

endmodule

测试模块代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/08/17 20:34:35

// Design Name:

// Module Name: SinWave_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module SinWave_tb( );

// reg define

reg rst_n;

reg aclk;

// reg define

wire data_valid;

wire [31:0] data;

parameter CLK_PERIOD = 'd5; //100MHz时钟

initial begin

aclk <= 1'b0 ;

rst_n <= 1'b0 ;

#(10 * CLK_PERIOD)

rst_n <= 1'b1 ;

end

always #CLK_PERIOD aclk = ~aclk;

SinWave_dds # (

.POFF ('d171798692)

) u_SinWave_dds(

.aclk (aclk ) ,

.rst_n (rst_n ) ,

.data_valid (data_valid ) ,

.data (data )

);

endmodule

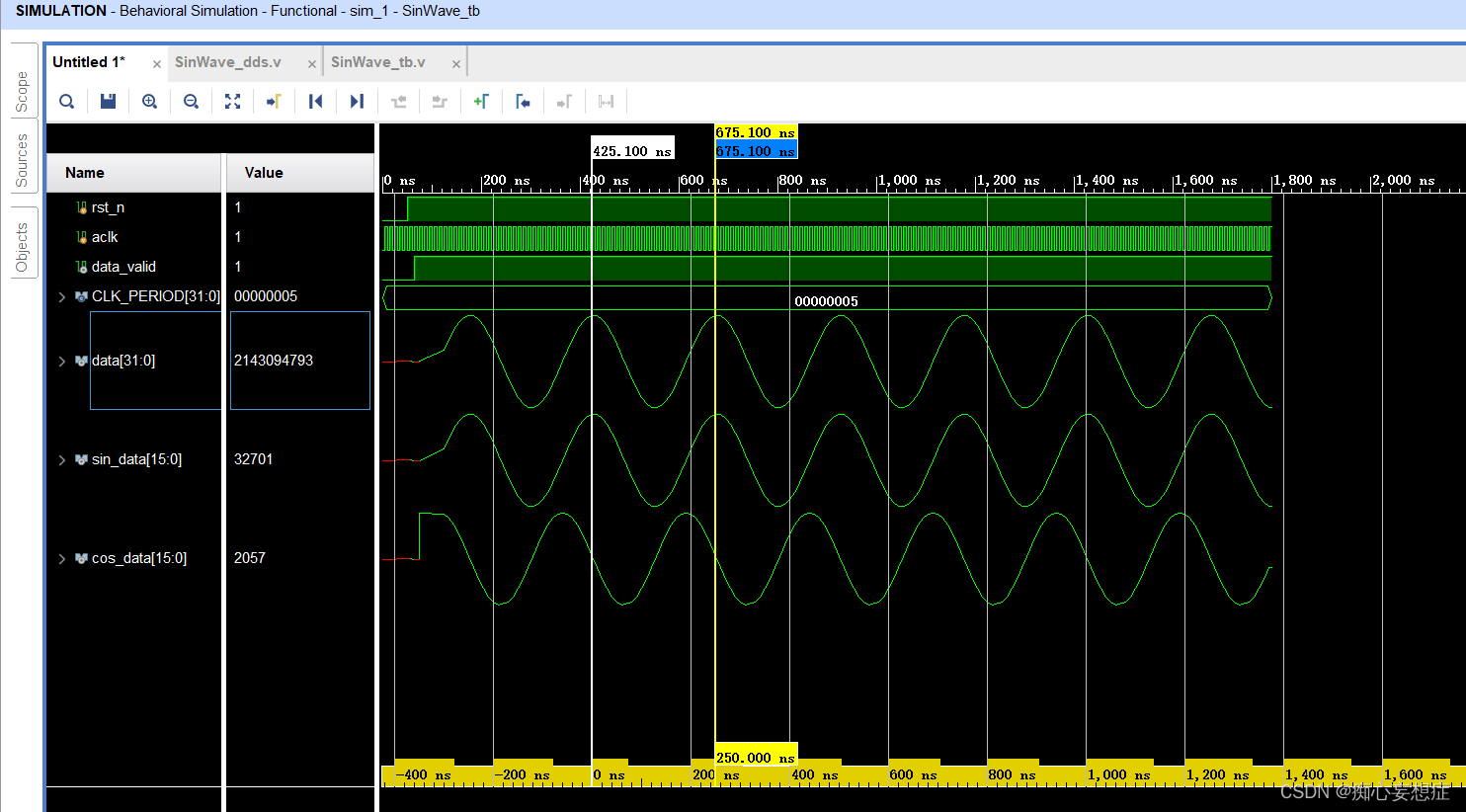

仿真结果如下:

参考文章如下:

1、References • Vitis High-Level Synthesis User Guide (UG1399) • 阅读器 • AMD 自适应计算文档门户 (xilinx.com)

3517

3517

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?