DDS complier v6.0使用

根据使用需求,设置dds格式为 “sin cos lut only”,赛灵思官方dds IP的说明文档对该模式的描述如下:

When configured as a SIN/COS LUT only, the Phase Generator is not implemented and the PHASE_IN signal is input using the input PHASE channel and transformed into sine and cosine outputs using a look-up table. Efficient memory usage is achieved by exploiting the symmetry of sinusoid waveforms. The core can be configured for sine only output, cosine only output or both (quadrature) output. Each output can be onfigured independently to be negated. Precision can be increased using optional Taylor series correction. This exploits DSP slices on FPGA families that support them to achieve high SFDR with high speed operation.

当仅配置为SIN/COSLUT时,不实现相位发生器,使用输入相位通道输入PHASE_IN信号,并使用查找表转换为正弦和余弦输出。通过利用正弦波形的对称性,实现了高效的内存使用。IP可以配置为仅正弦输出、仅余弦输出或两者兼有(正交)。每一个输出可以独立配置或取消。精度可以使用可选的泰勒级数校正。这利用了支持它们的FPGA系列上的DSP资源来实现高速运行。

总的来说,当使用LUT模式时,输出可以指定为sin或cos或两者都有,此时IP核利用正弦波的对称性来提高内存使用效率,利用查找表输出。

使用时,设置“mode of operation”模式为 ”Rasterize”,该模式的文档描述为:

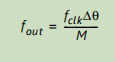

DDS 的光栅化操作模式不会截断累积相位。光栅化操作适用于所需频率是系统时钟的有理部分的配置(输出频率 = 系统频率 * N/M,其中 0 < N < M)。 支持从 9 到 16384 的 M 值。 SIN/COS LUT 被相应地配置为从 0 到 M-1 的值,它描述了一个完整的圆。 因为在光栅化操作模式中没有相位截断,所以不需要抖动或泰勒校正,因为它们减轻了相位截断的影响。 在光栅化操作中,相位噪声显着降低。 因此,输出相角分辨率和幅度分辨率仅由LUT表输出宽度决定。 在光栅化模式下,在适用的情况下利用象限对称来减少内存使用。单通道配置的 DDS 波形的输出频率 fout 是系统时钟频率 fclk、模数 M 和相位增量值 ΔΘ 的函数。以赫兹为单位的输出频率定义为

第二页实现部分,可以修改输出是cos或sin或两者都有,然后就是选择输出是否要反向。其中比较重要的设置是幅度模式这个设置,根据文档描述,该部分的区别为:

幅度模式:此选择允许来自 DDS 的两个幅度之一。

- 全范围:针对需要二进制补码表示内的最大幅度的通信应用,但由于期望自动增益控制,幅度值不太重要。对于非泰勒模式,全范围模式的目标振幅为 1–2^(输出宽度–2),而对于泰勒模式,振幅在此值和 1 之间变化。请注意,此处的幅度首先归一化为具有二进制小数点的输出宽度。 8> 位输出的二进制幅度为 100000000 – 10,给出介于 01111110 和 11111110 之间的值,分别对应于略小于 1> 和略大于 –1。

- 单位圆:对于 DDS 输出幅度值很重要的应用,例如 FFT 旋转因子生成。 当单位圆时,DDS 输出幅度为半满范围(即值范围从 01000…(+0.5). 到 110000…(-0.5))。 由于幅度在整个范围内减少了 2 倍,SDFR 减少了 6 dB。 增加 SFDR 或输出宽度以满足此要求。

两者的区别在于,单位圆模式的模值更接近1,但是小数位宽要小,而全幅度模式更加省资源,在实际使用的时候发现,单位元模式下,cos的输出总是从零开始,比如我输入相位值是0,cos的输出应该是1,但是cos的输出第一个值总是0,这就不符合我们的要求,所以这里我们用全幅度模式。

其他的全部选择默认设置。

2503

2503

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?