数码管显示日期(FPGA)

提示:以下是本篇文章正文内容,下面案例可供参考

一、实验要求

1.驱动6个数码管显示当天日期(230327)

二、实验原理

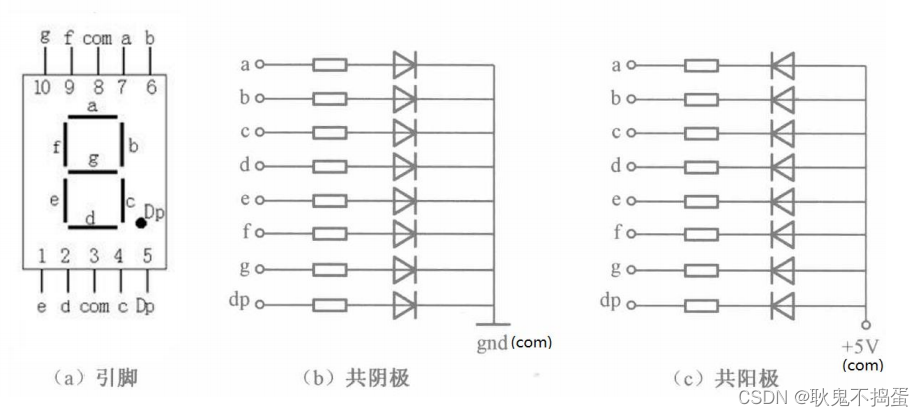

1.数码管内部原理图

数码管内部电路如图 1所示,从该图可以看出,一位数码管的引脚是10个,其中7个引脚对应连接到组成数码管中间“8”字型的led,Dp引脚连接到数码管的小数点显示led(dp)。最后还有两个公共端,生产商为了封装统一,单个数码管都封装成10个引脚,其中8和3两个公共端引脚(图中为com)是连接在一起的。公共端又可分为共阳极和共阴极,图 1(b)为共阴极内部原理图,图 1(c)为共阳极内部原理图。

对共阴极数码管来说,其8个发光二极管的阴极在数码管内部全部连接在一起,所以称“共阴”,而阳极独立。对共阳极数码管来说,其8个发光二极管的阳极在数码管内部全部连接在一起,所以称“共阳”,而阴极独立。以共阳极数码管为例,当我们想让数码管显示数字“8”,可以给a、b、c…g七个引脚送低电平,数码管就显示“8”,显示数字“1”,就给b、c引脚低电平,其余引脚(除公共端)给高电平,数码管就显示“1”。

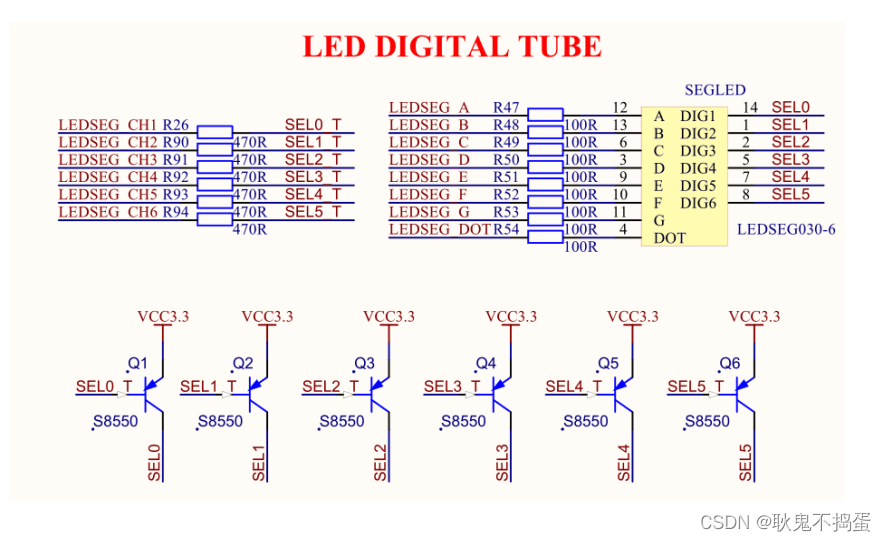

2.硬件原理图

我们的开拓者FPGA开发板上有6位共阳数码管,其原理图如图 2 所示。在这里我们需要注意的是,为了增加FPGA输出信号的驱动能力,我们使用PNP型三极管驱动数码管的位选段,所以给三极管基极提供低电平时,位选信号为高电平。

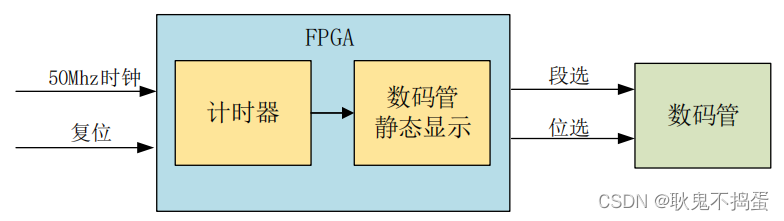

4.系统设计

需要一个静态数码管显示模块在数码管上显示数据,其次需要一个计时模块每当计时到0.5ms(1KHZ)时改变数码管显示的数值。由此画出系统的功能框图如下所示:

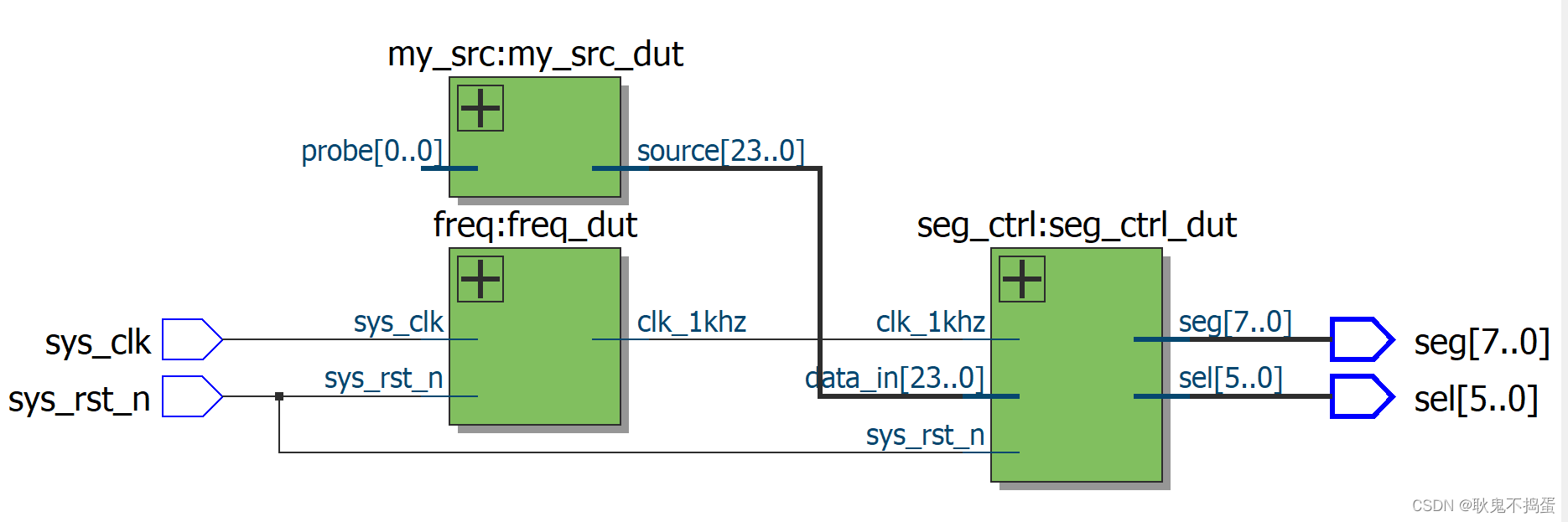

程序中各模块端口及信号连接如图 5 所示

二、代码

1.顶层模块如下所示:

module seven_tube(

input sys_clk, //系统时钟:50MHZ

input sys_rst_n, //系统复位:低电平有效

output [5:0] sel, //数码管位选信号

output [7:0] seg //数码管段选信号

);

wire clk_1khz; //定义中间连线信号

freq freq_dut(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.clk_1khz (clk_1khz)

);

seg_ctrl seg_ctrl_dut(

.clk_1khz (clk_1khz),

.sys_rst_n (sys_rst_n

1.不同开发板的引脚不同,需根据自己开发板重新配置引脚2.不同开发板的数码管高低电平有效不同,使用前需参考原理图3.数码管刷新频率采用1KHZ原因:频率过快(50MHZ)和频率过慢(1HZ)都会导致数码管显示不稳定,故选用1KHZ作为刷新频率。

1.不同开发板的引脚不同,需根据自己开发板重新配置引脚2.不同开发板的数码管高低电平有效不同,使用前需参考原理图3.数码管刷新频率采用1KHZ原因:频率过快(50MHZ)和频率过慢(1HZ)都会导致数码管显示不稳定,故选用1KHZ作为刷新频率。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6330

6330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?