一.任务

1.

在线Verilog编程网站学习:从门电路、组合电路、时序电路中各选3个以上的例题进行实践练习,并记录结果(包括初学时发生的错误)。

2.

(1)首先安装Logisim软件,新建一个项目,采用门电路组合电路方式完成一个1位全加器的设计,并在Logisim中进行测试。然后封装这个1位全加器为自定义的一个子电路模块(比如名称为OneAdder),然后新建一个项目,用1位全加器串行级联方式完成一个4位全加器的设计,并进行功能测试。

(2)首先基于Quartus 软件完成一个1位全加器的设计。分别采用原理图输入以及 Verilog编程 这两种设计方法。然后通过4个1位全加器的串行级联,完成一个4位全加器的 原理图设计;再改用 Verilog编程(3种模式:门电路、数据流和行为级描述),完成这个4位全加器设计,并观察Verilog代码编译综合后生成的 RTL电路,与之前电路图设计的4位全加器电路进行对比 。

(3)编写 测试激励Verilog模块,用Modelsim 对4位全加器 Verilog模块进行仿真测试,观察仿真波形图。如果仿真波形的逻辑功能正确,就连接的实验室 DE2-115开发板硬件上,完成引脚绑定,烧录,再拨动按钮开关,进行加法器 正确性的验证。

二.实验过程

1.在线Verilog编程网站学习

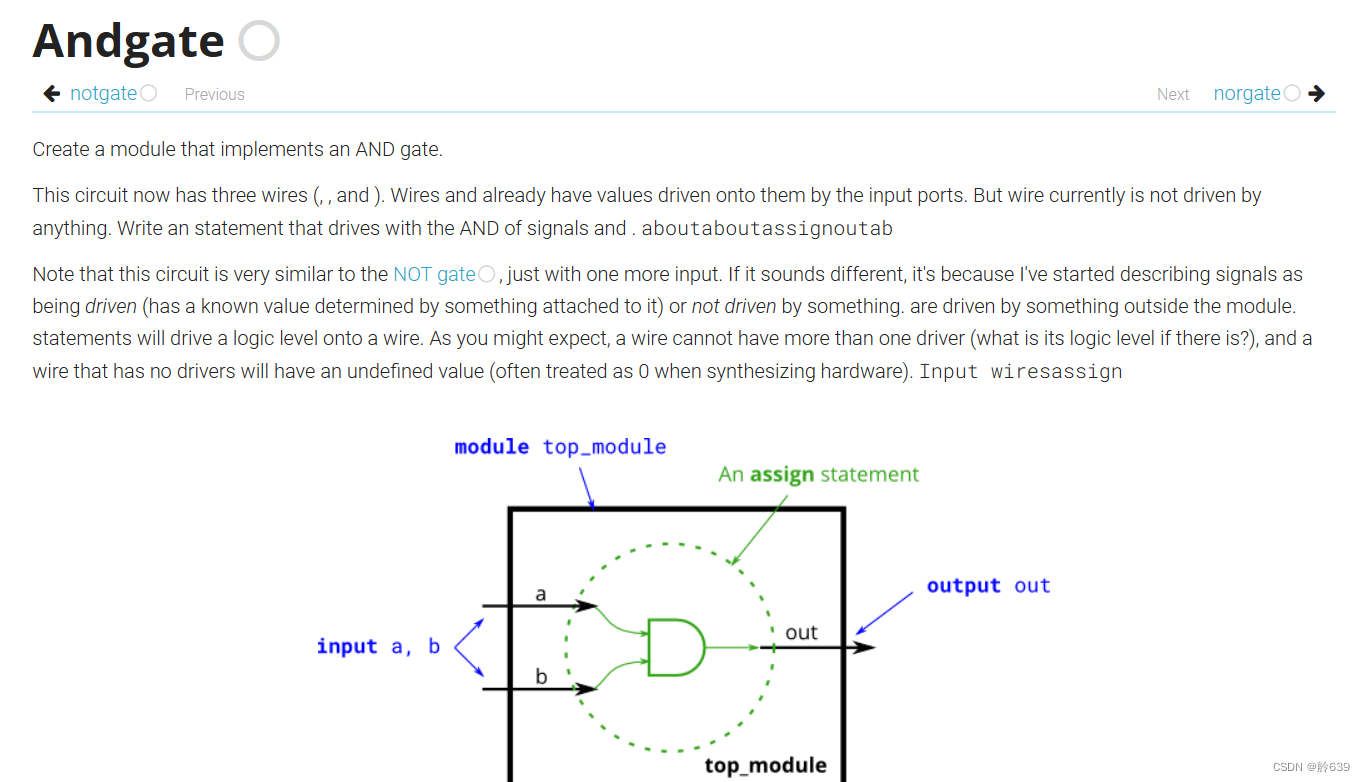

(1)门电路

提交代码:

module top_module(

input a,

input b,

output out );

assign out=a&&b;

endmodule

结果:

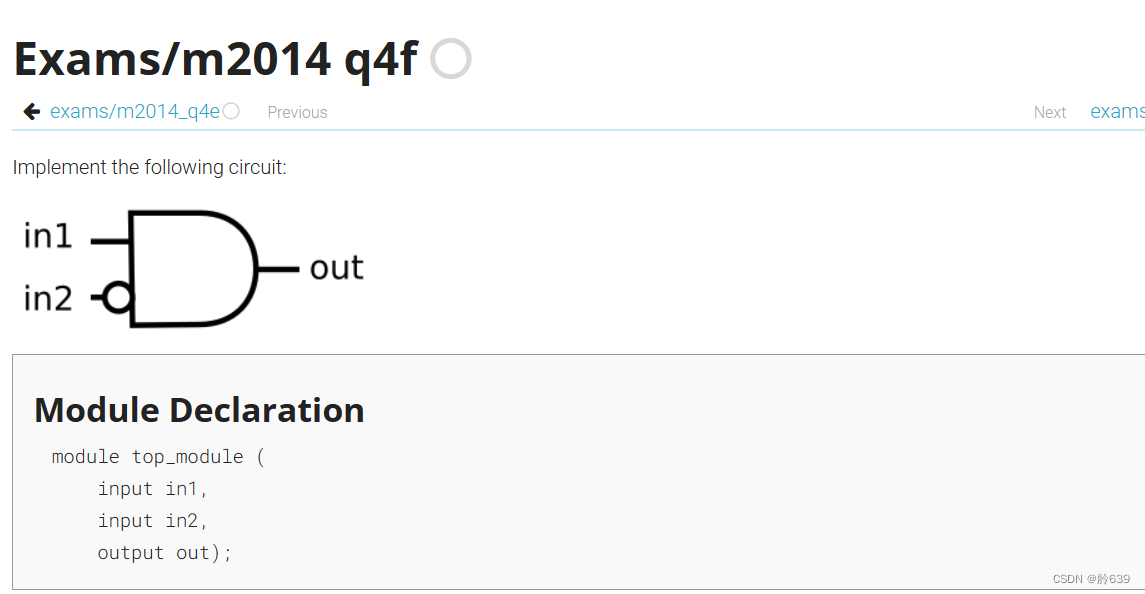

(2)组合电路

提交代码:

module top_module(

input a,

input b,

output out );

assign out = in1 && (~in2);

endmodule

结果:

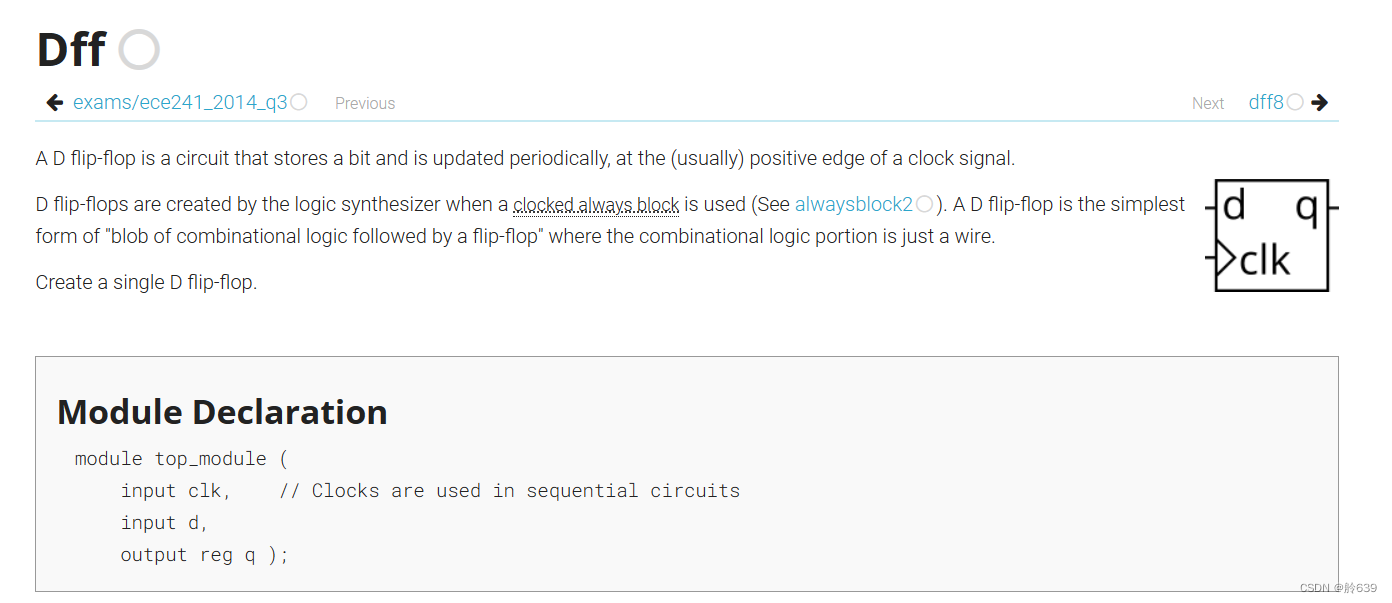

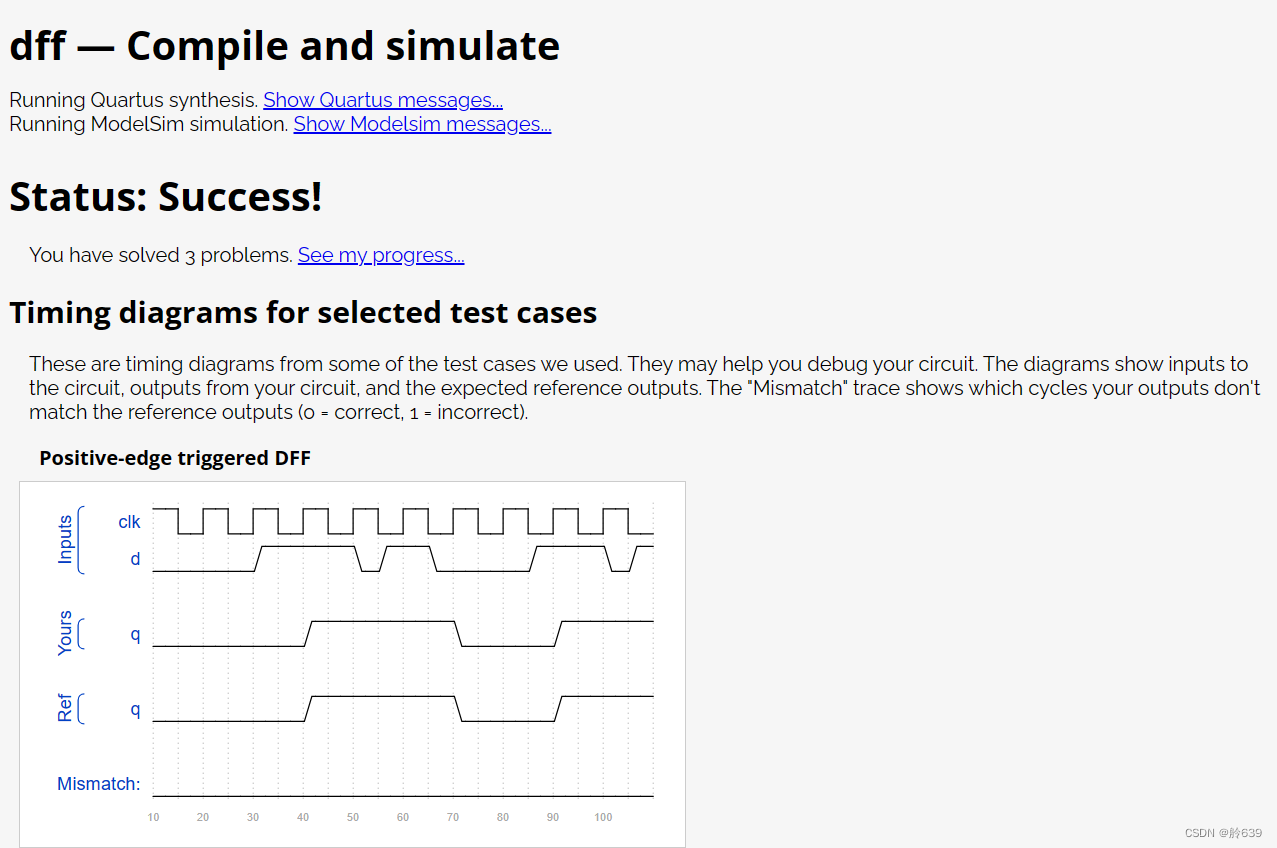

(3)时序电路

输入代码:

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @(posedge clk) begin

q <= d; // 在正边沿时,将输入 d 的值传递给输出 q

end

endmodule

结果:

2.Logisim全加器设计

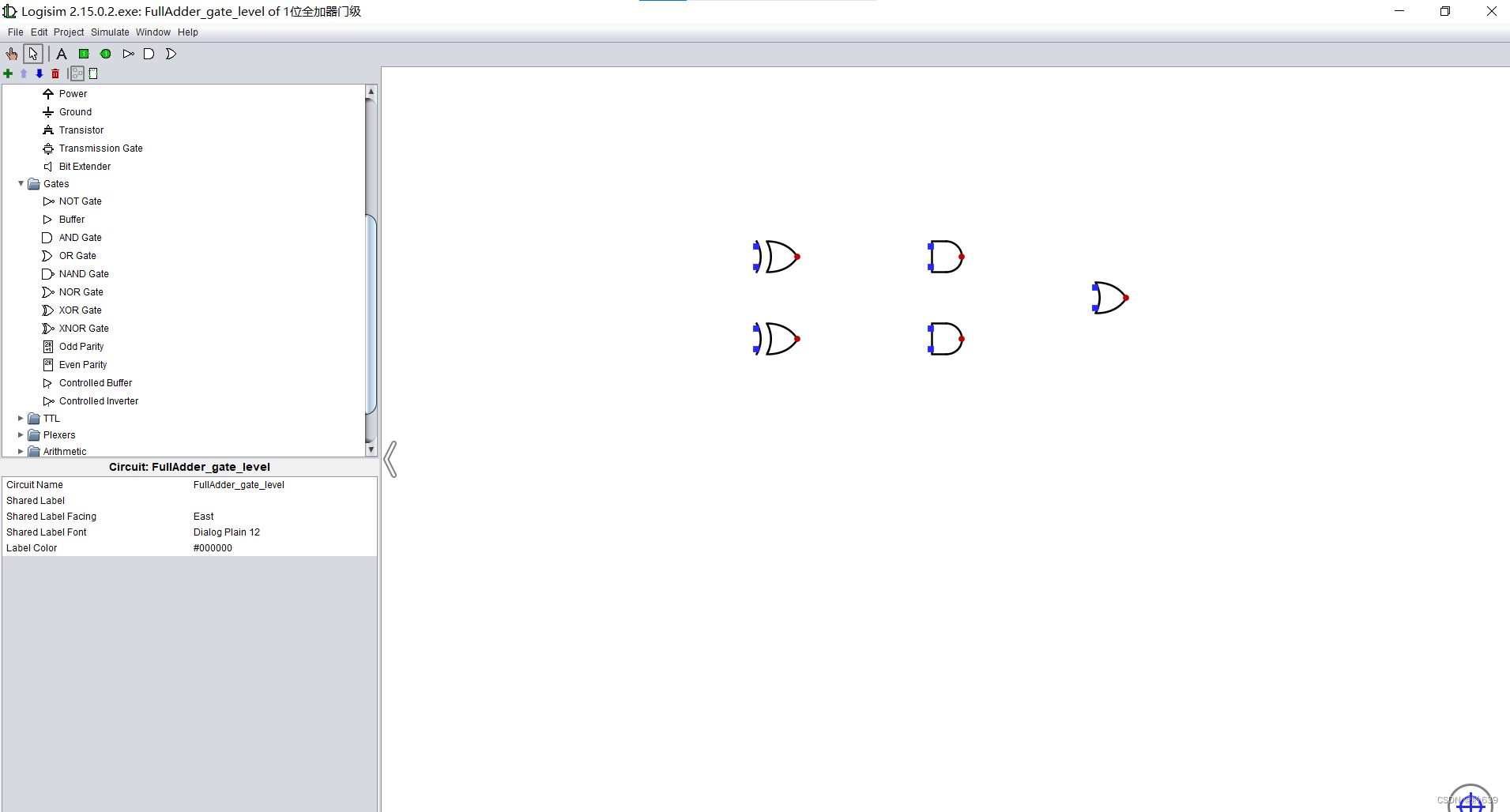

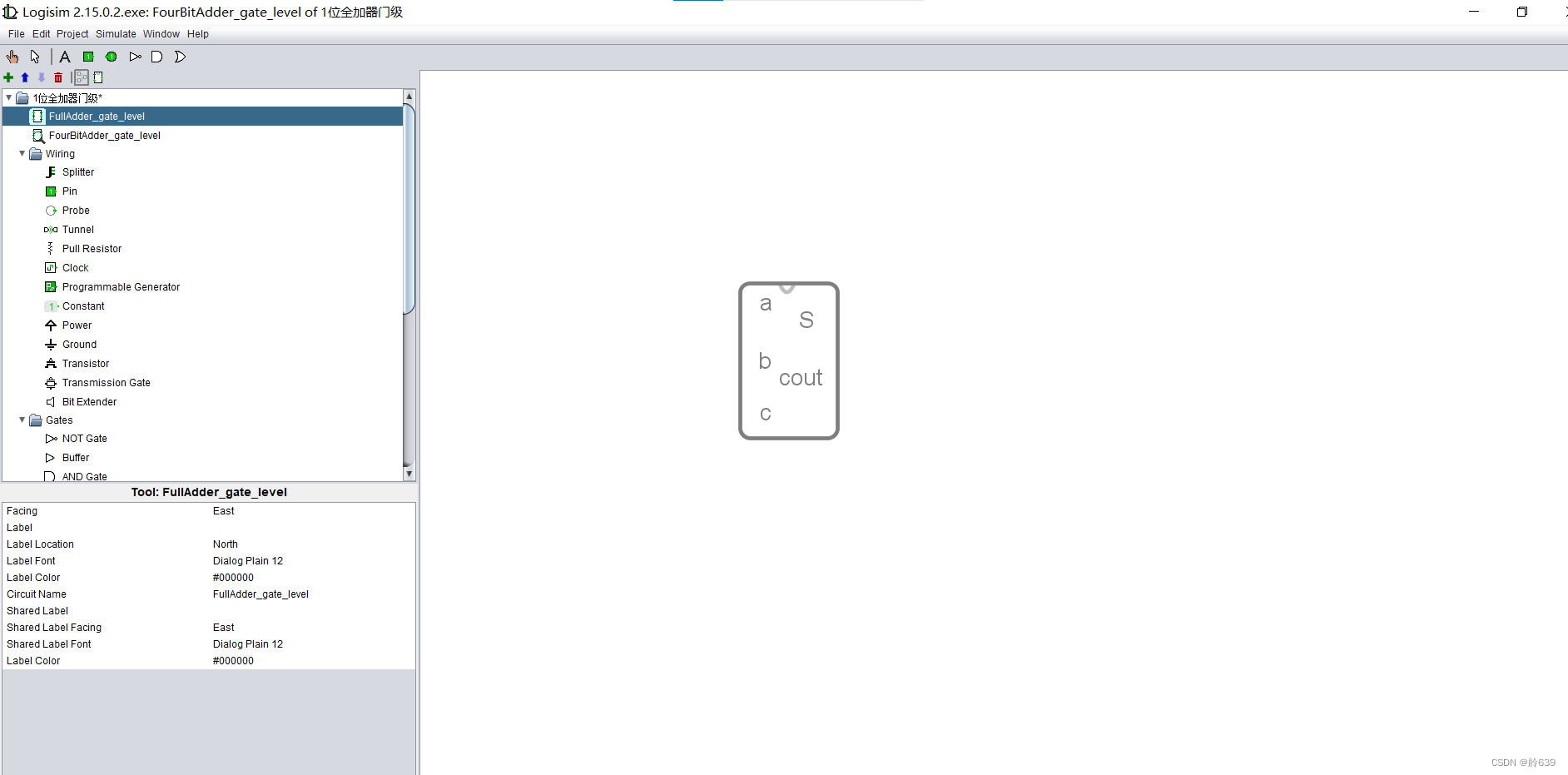

(1)1位全加器

打开logisim

在左侧寻找并添加如下图器件

添加三处输入与两处输出

并将线路按下图方式连接

可在点击如图选项后对输入进行测试

测试效果如下:

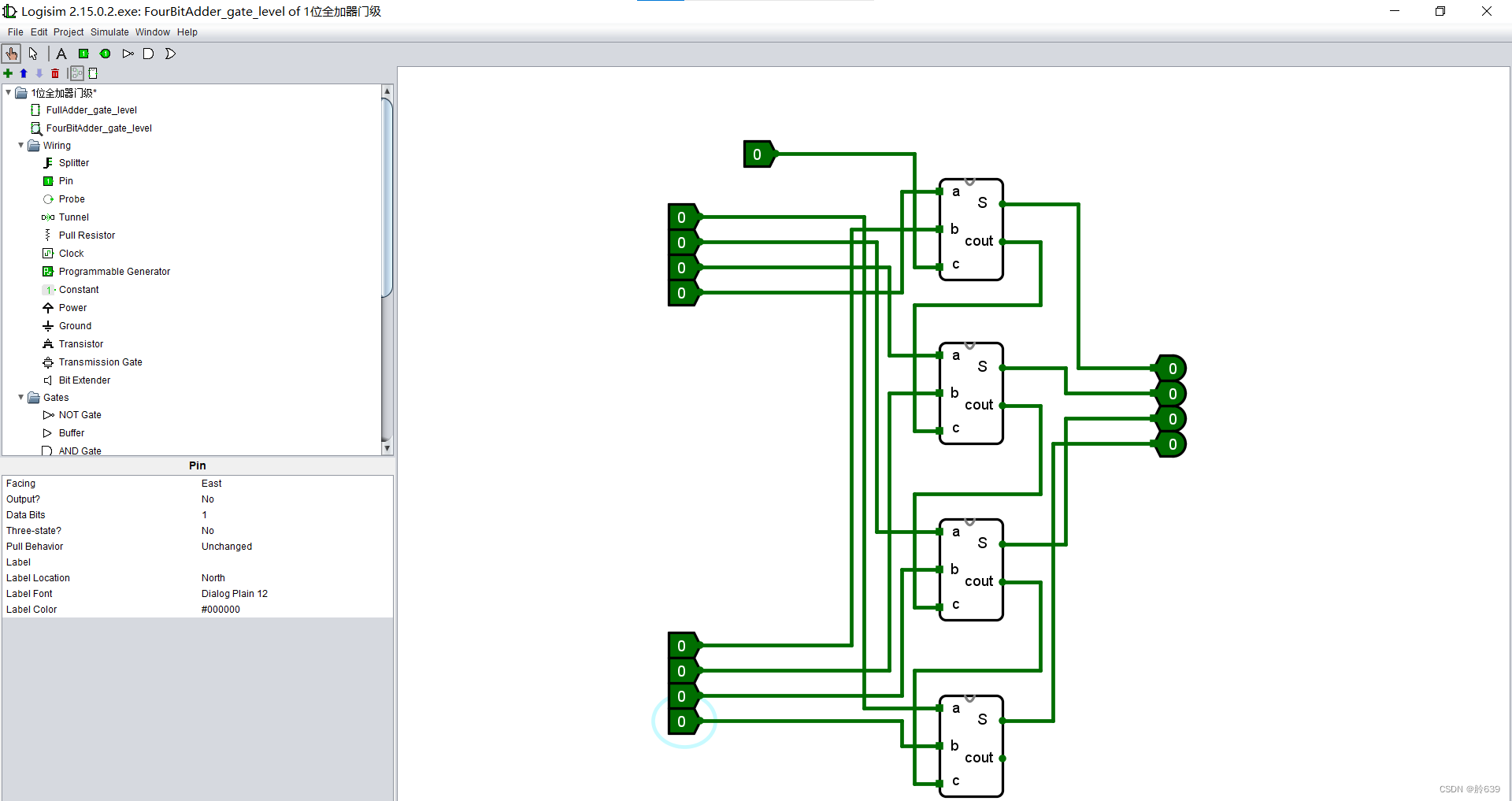

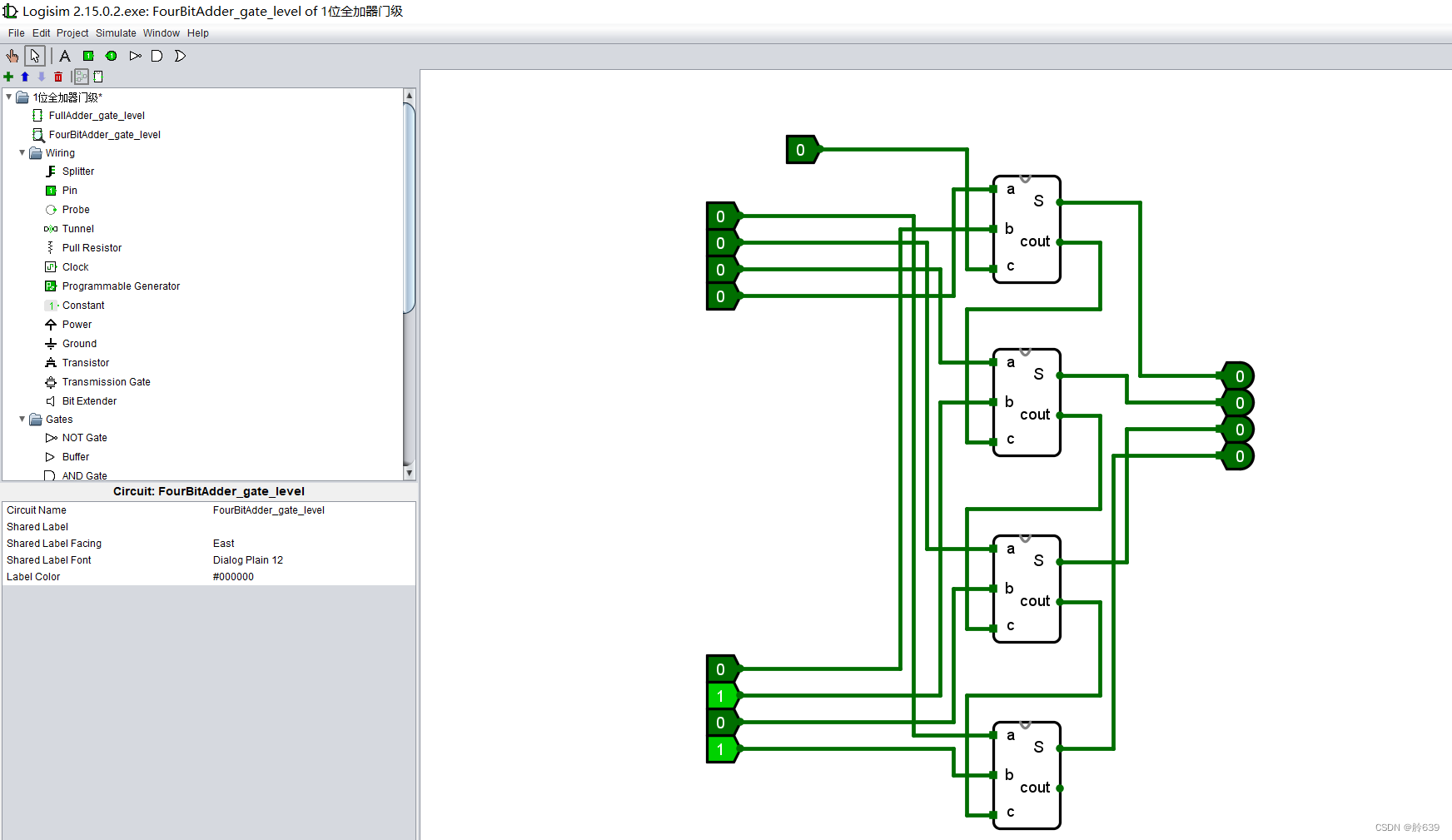

(2)4位全加器

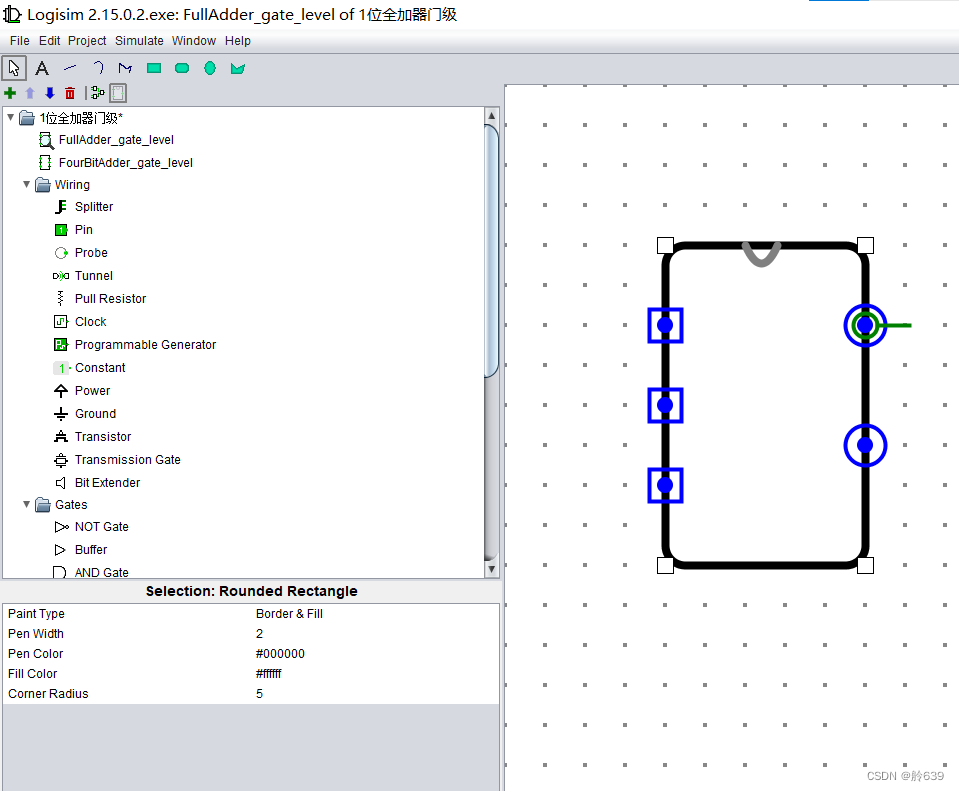

实现4位全加器前需对1位全加器进行封装

点击下图按钮进行封装相应的操作:

可对拖动边角对器件调整大小,然后拖动管脚到器件边缘

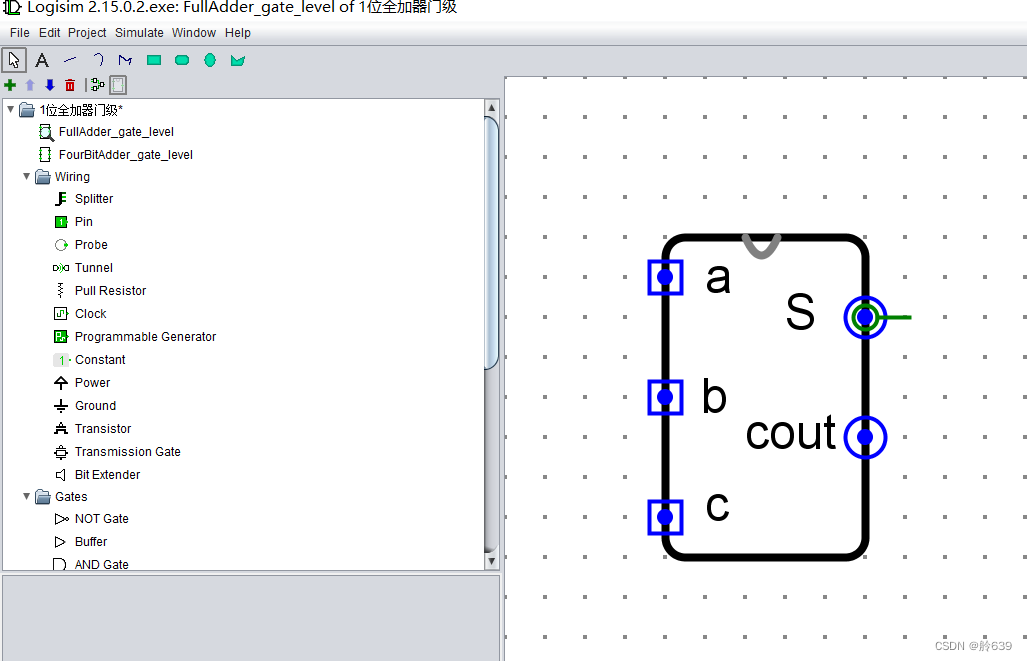

点击下图按键对管脚进行命名

右键单击项目创建新电路

在新添加的电路图中左键单击1位全加器的电路图文件可在新建电路图放置封装好的1位全加器电路

这里放置4个

按下图将电路图绘制完毕

改变输入信号进行测试:

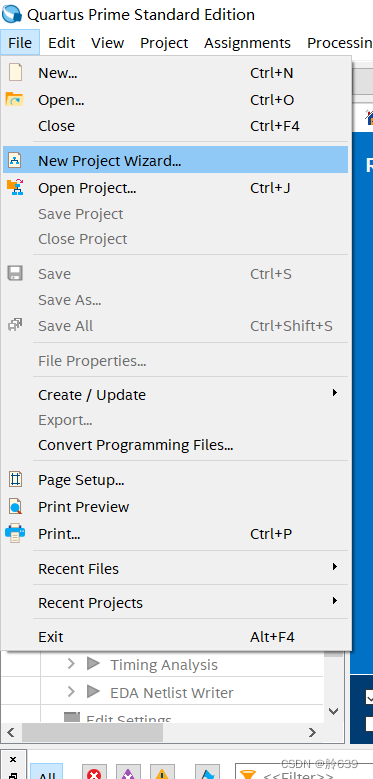

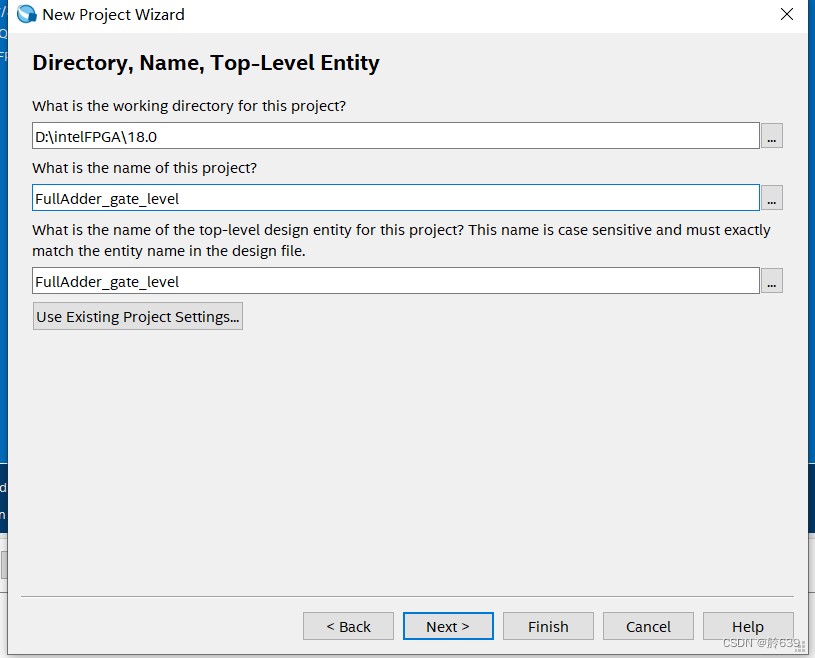

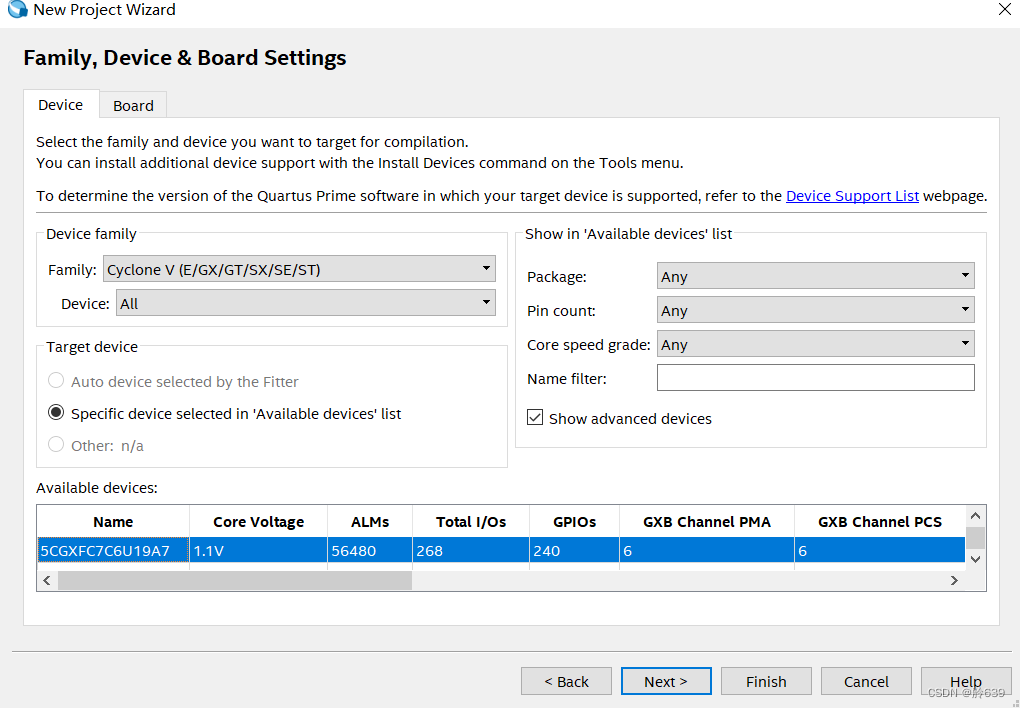

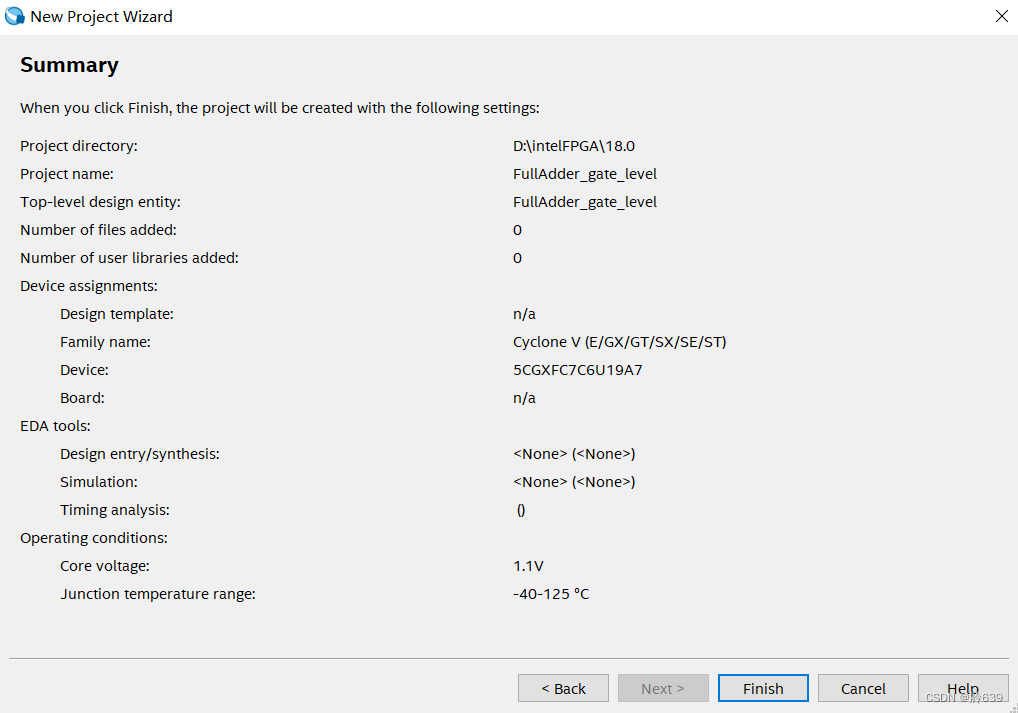

3.Quartus全加器设计

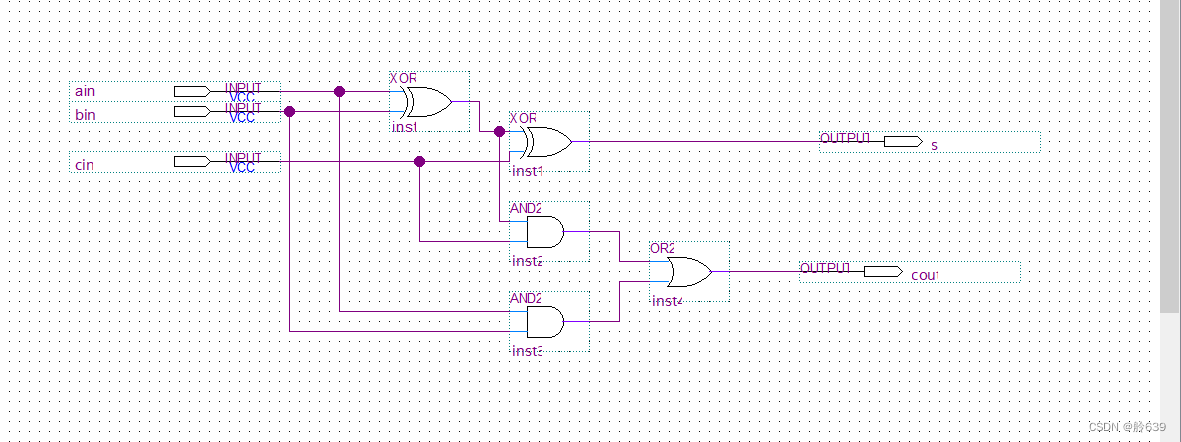

(1)原理图输入方式

新建项目

一路next到下图,选择元件:

再接着next,最后点击finish

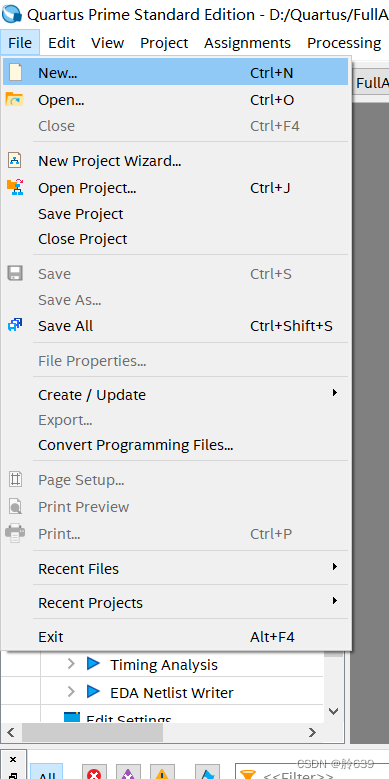

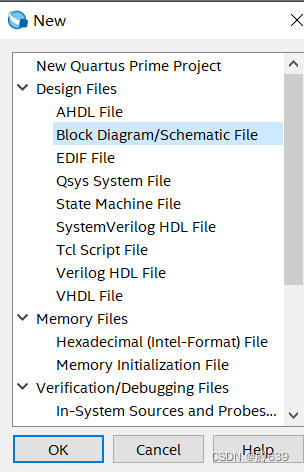

创建完项目后新建原理图:

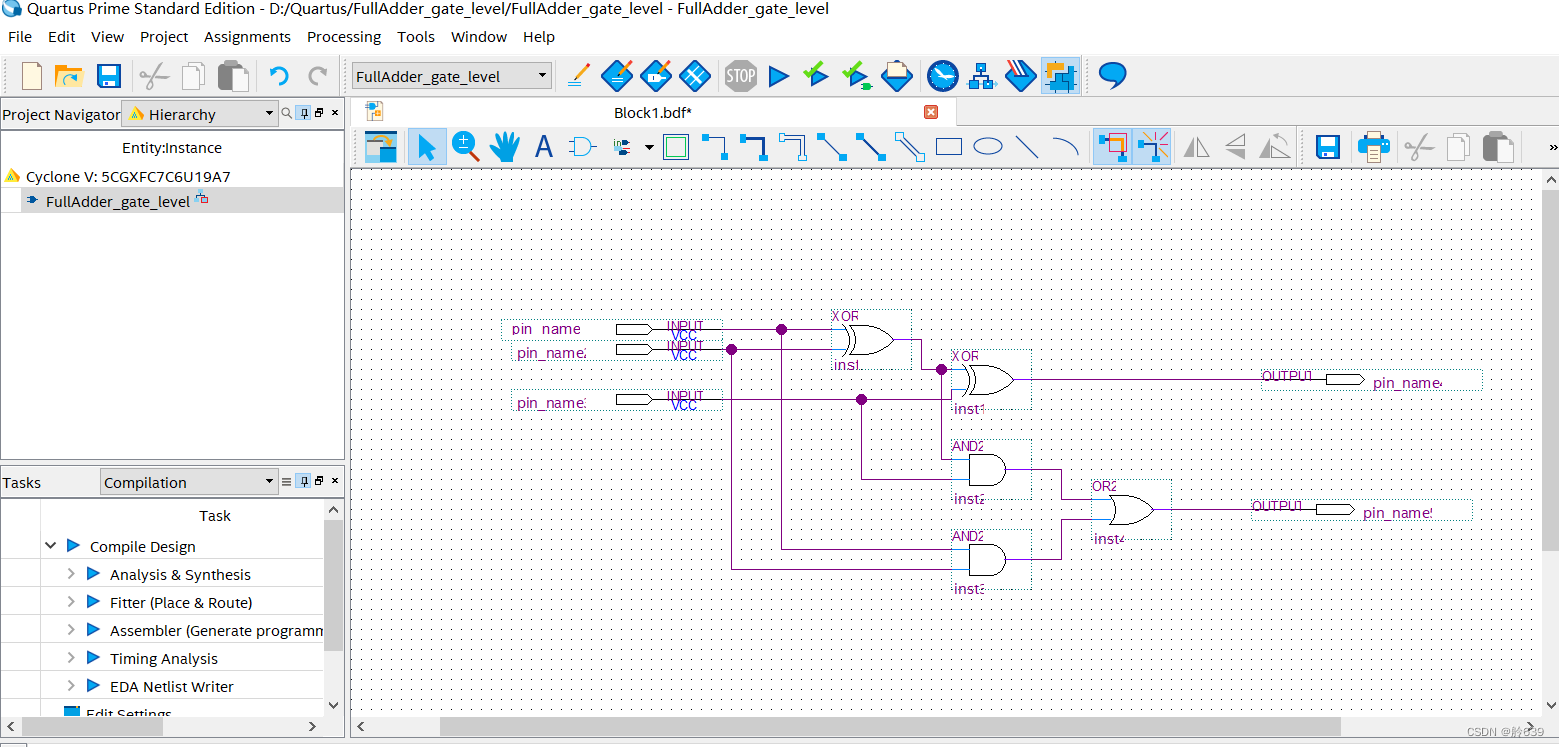

点击下图标志在新页面左侧寻找相应器件:

选择如下图器件并连接

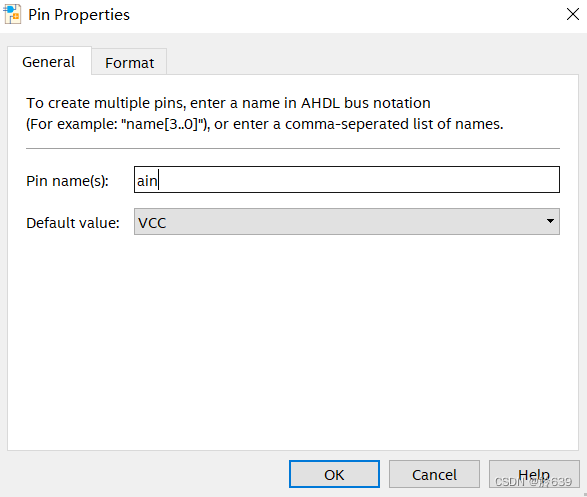

可双击各类元件编辑名称

保存编译:

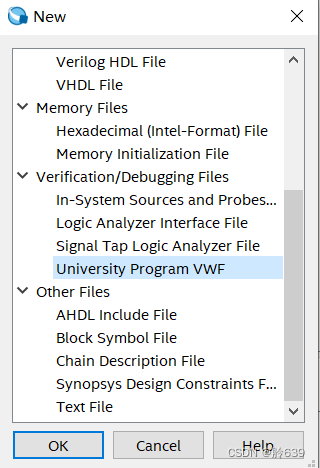

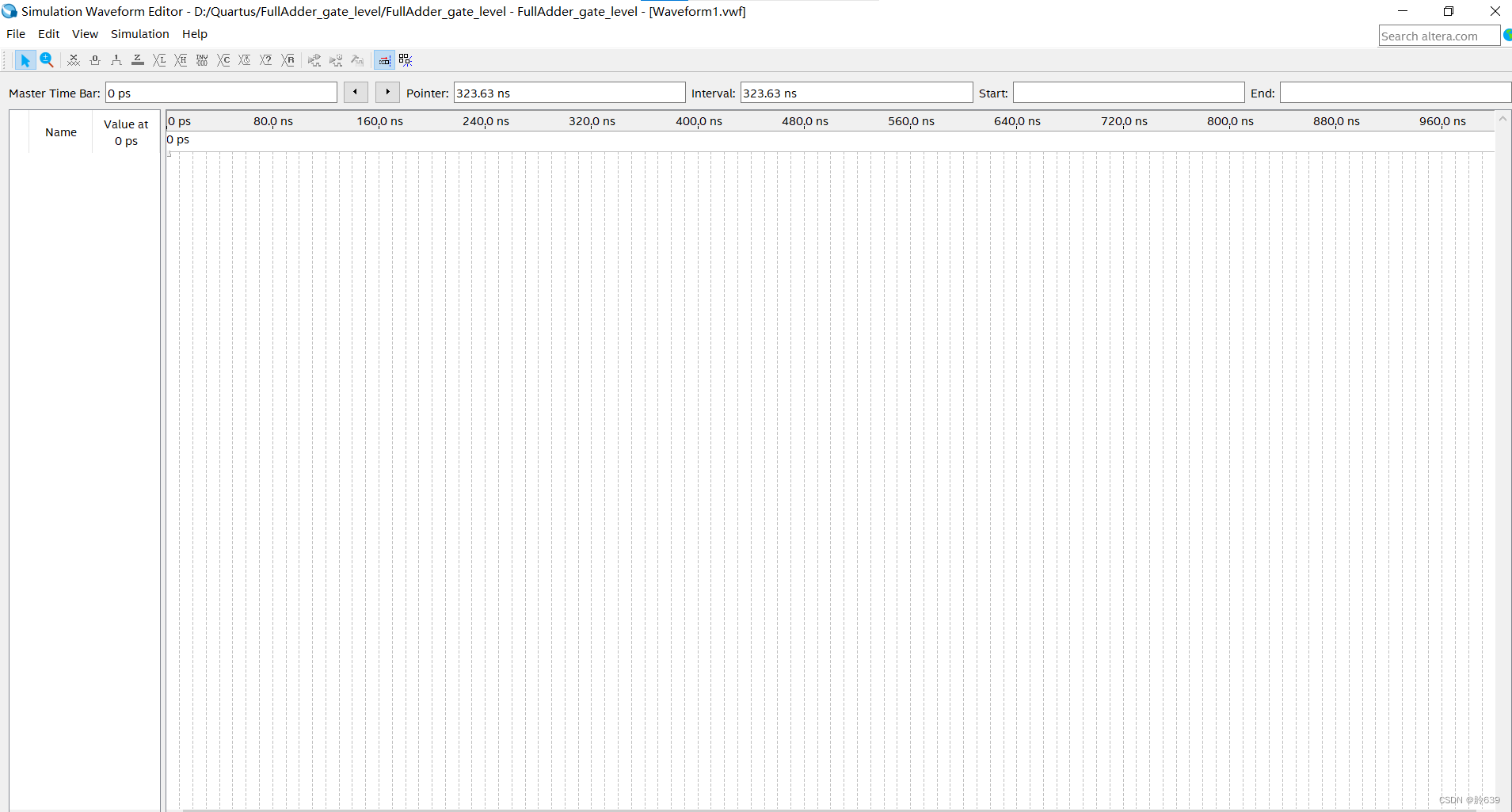

创建波形文件进行测试:

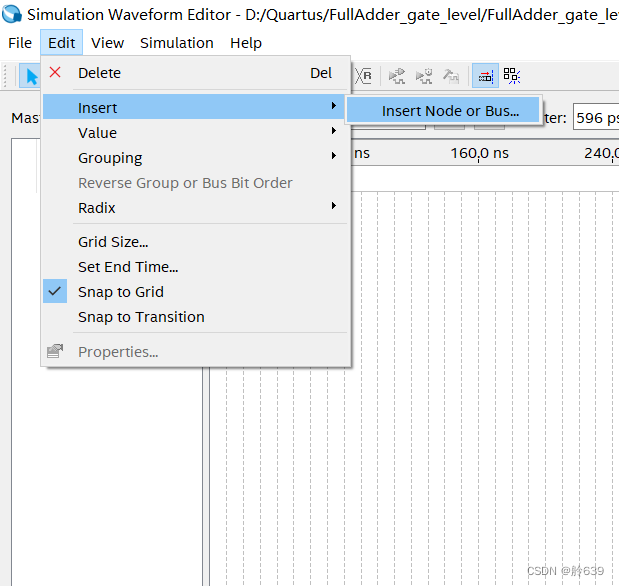

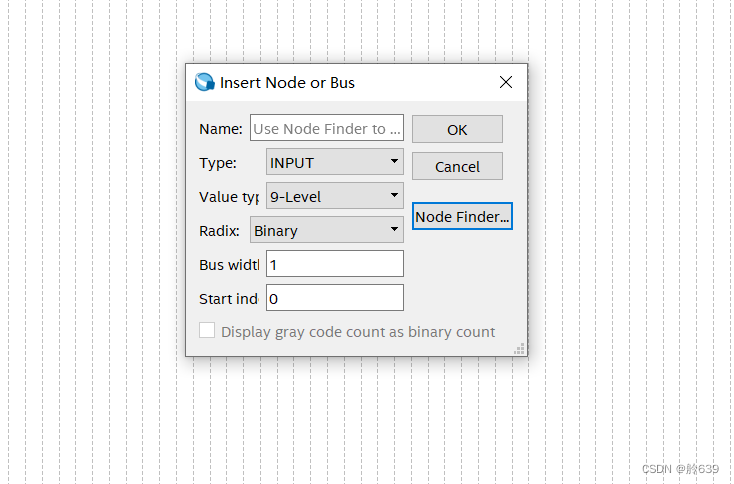

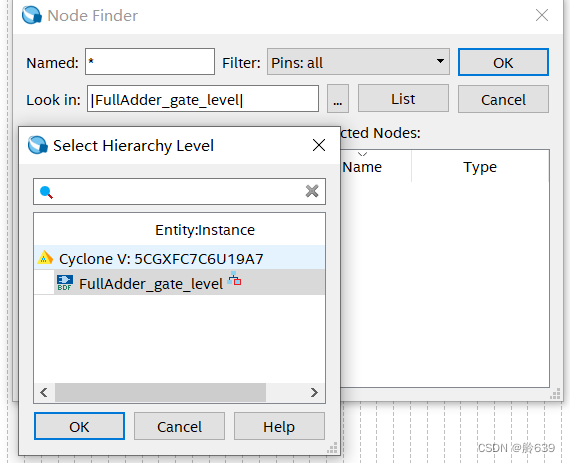

点击Node Finder

选择Look in选项内的文件

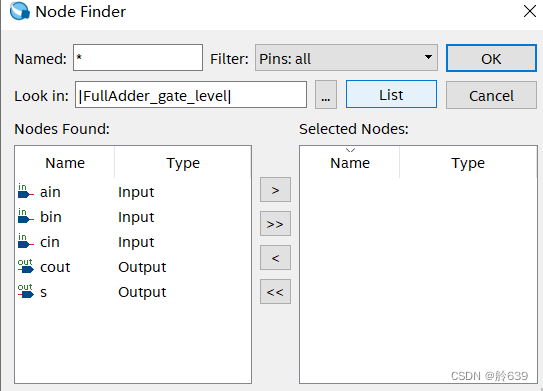

点击list

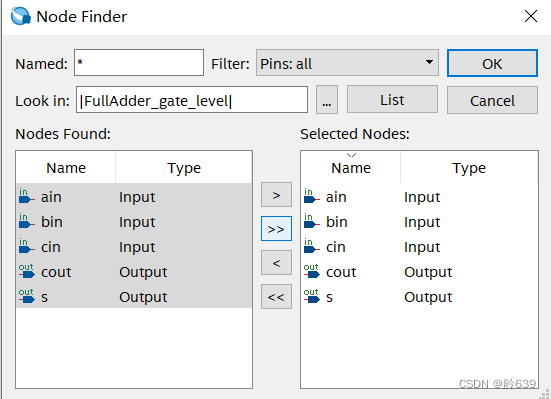

点击>>按键,之后连续点击ok

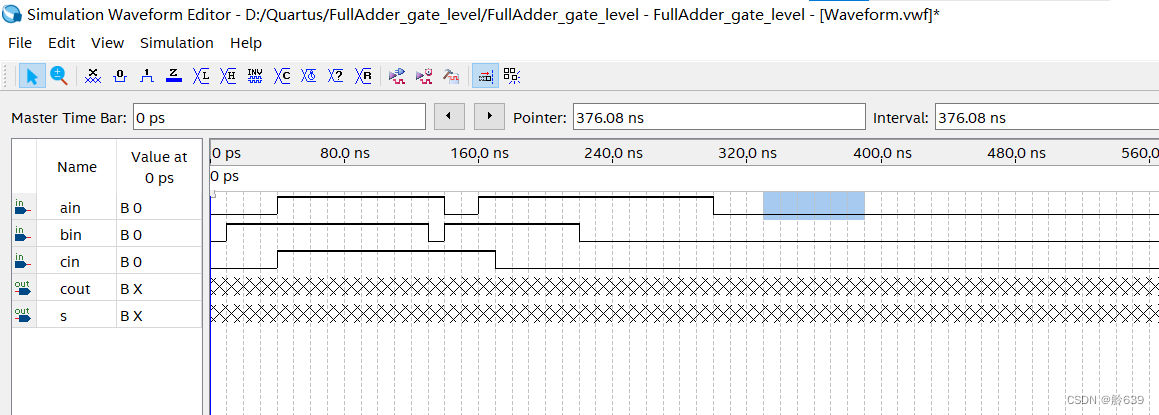

可选中对应段波形对波形进行编辑

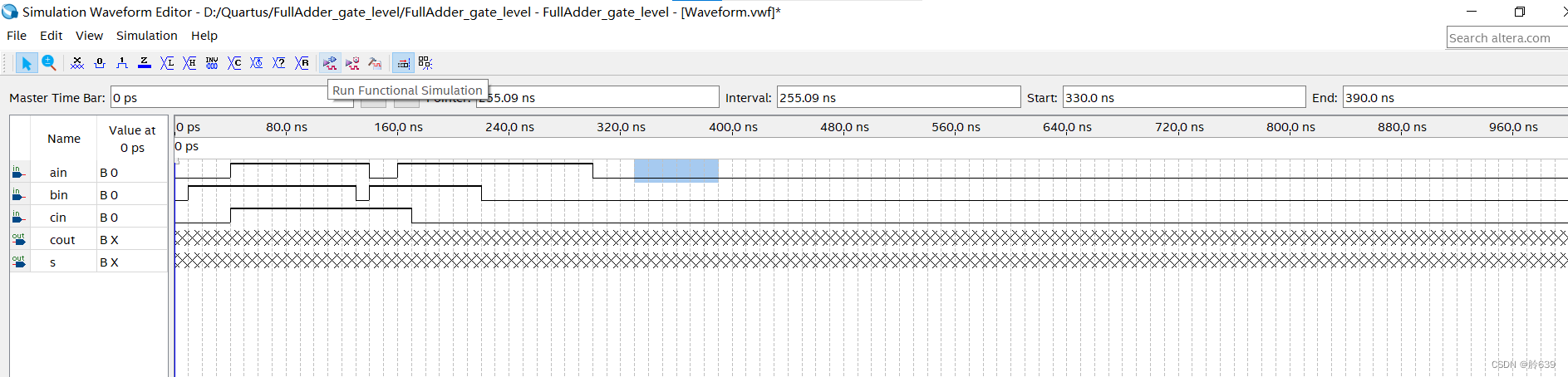

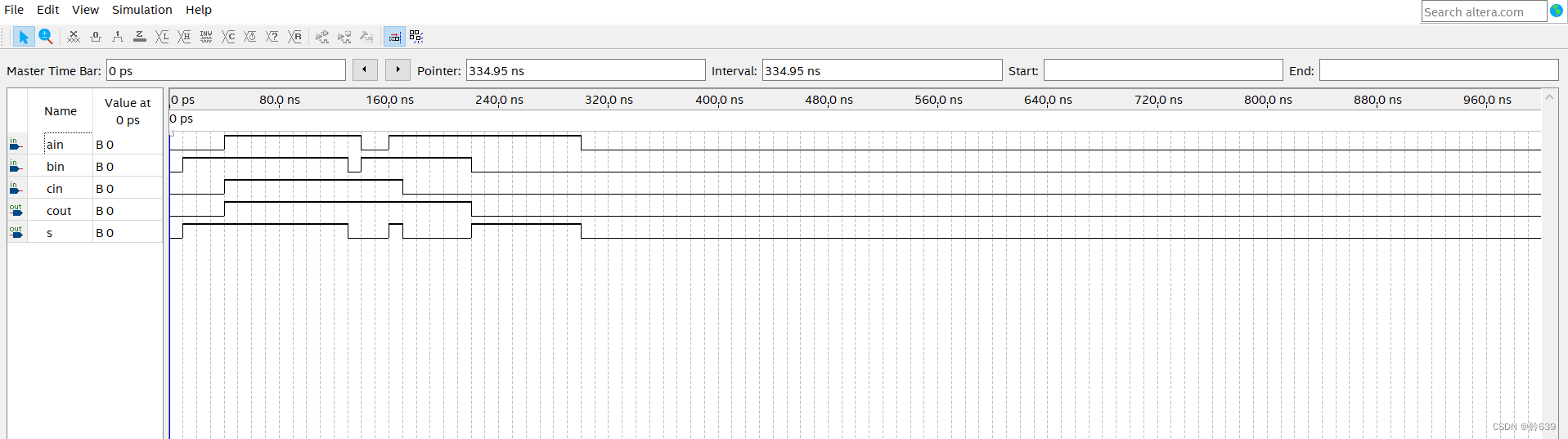

点击进行测试

测试完成

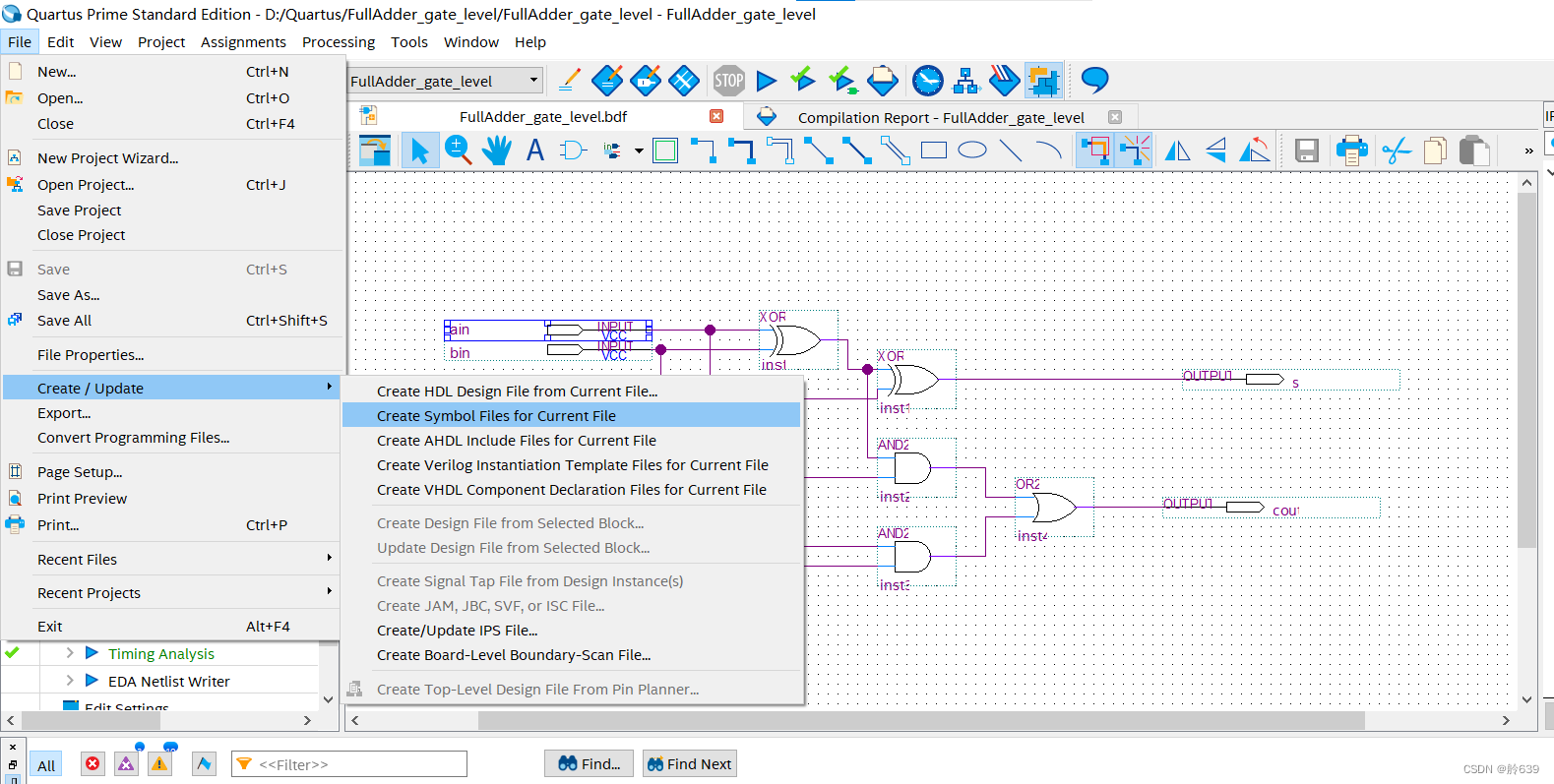

对1位全加器进行封装:

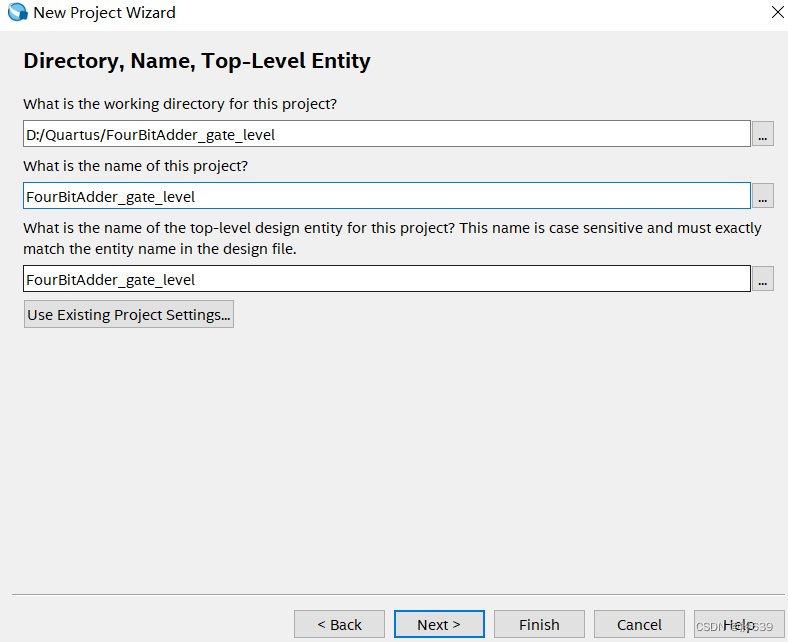

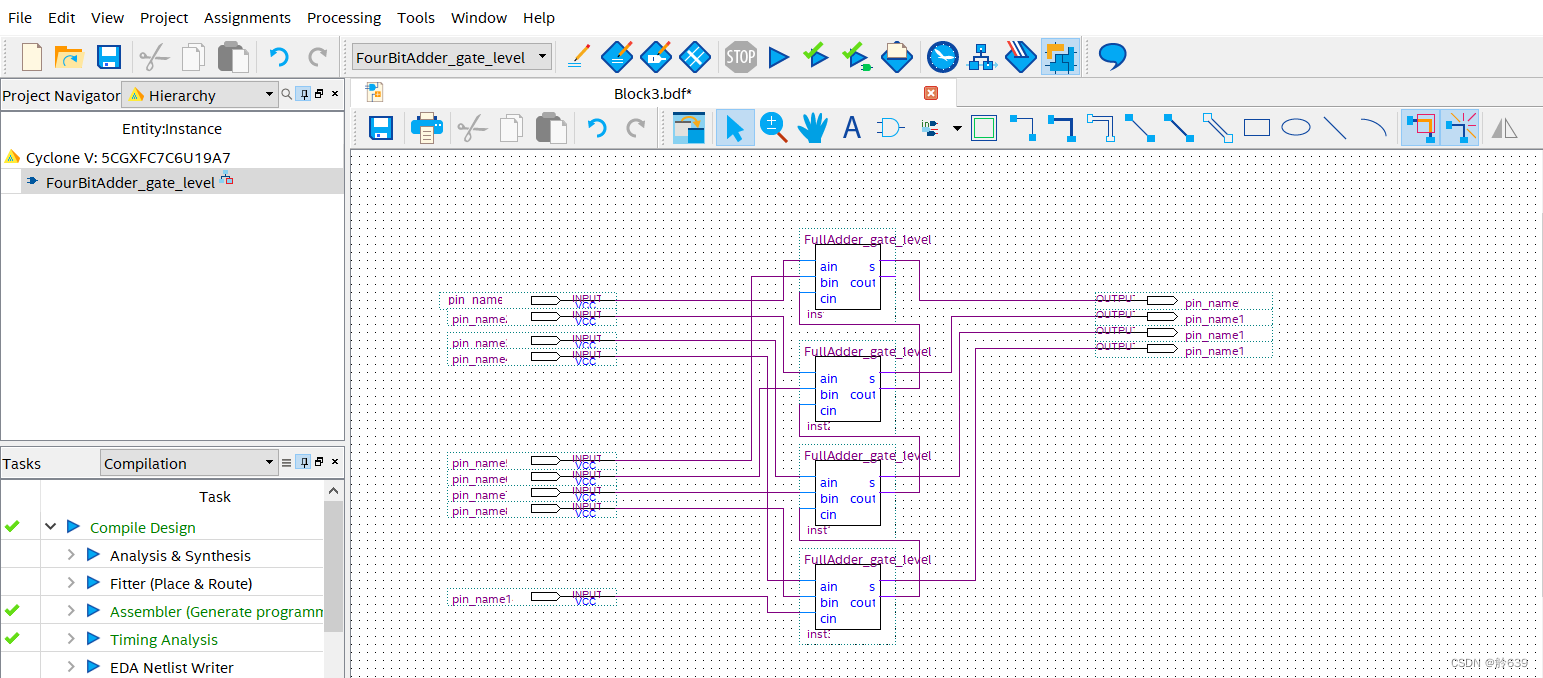

新建4位全加器项目:

新建原理图,连接如下图线路:

1位全加器可通过新封装的文件选择器件:

(2)Verilog编程方式

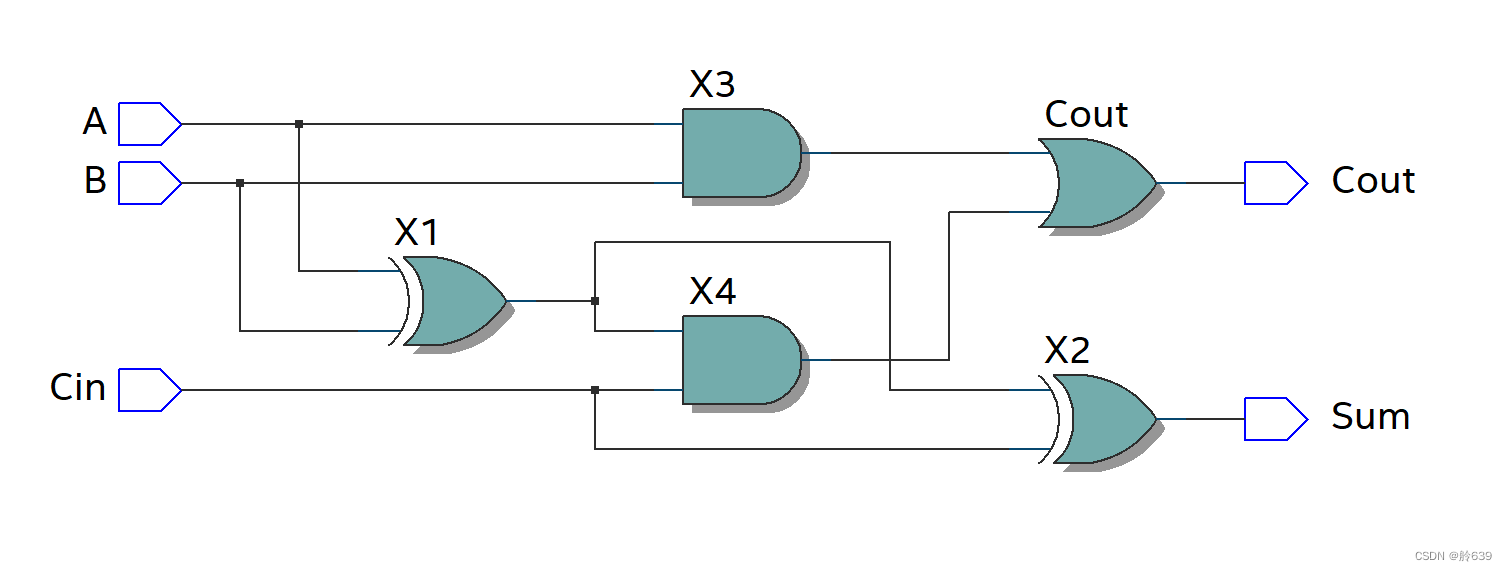

1、1位全加器

module Verilog2 (

input A, B, Cin,

output Sum, Cout

);

wire X1, X2, X3, X4;

// XOR gates

assign X1 = A ^ B;

assign X2 = X1 ^ Cin;

// AND gates

assign X3 = A & B;

assign X4 = X1 & Cin;

// OR gates

assign Sum = X2;

assign Cout = X3 | X4;

endmodule

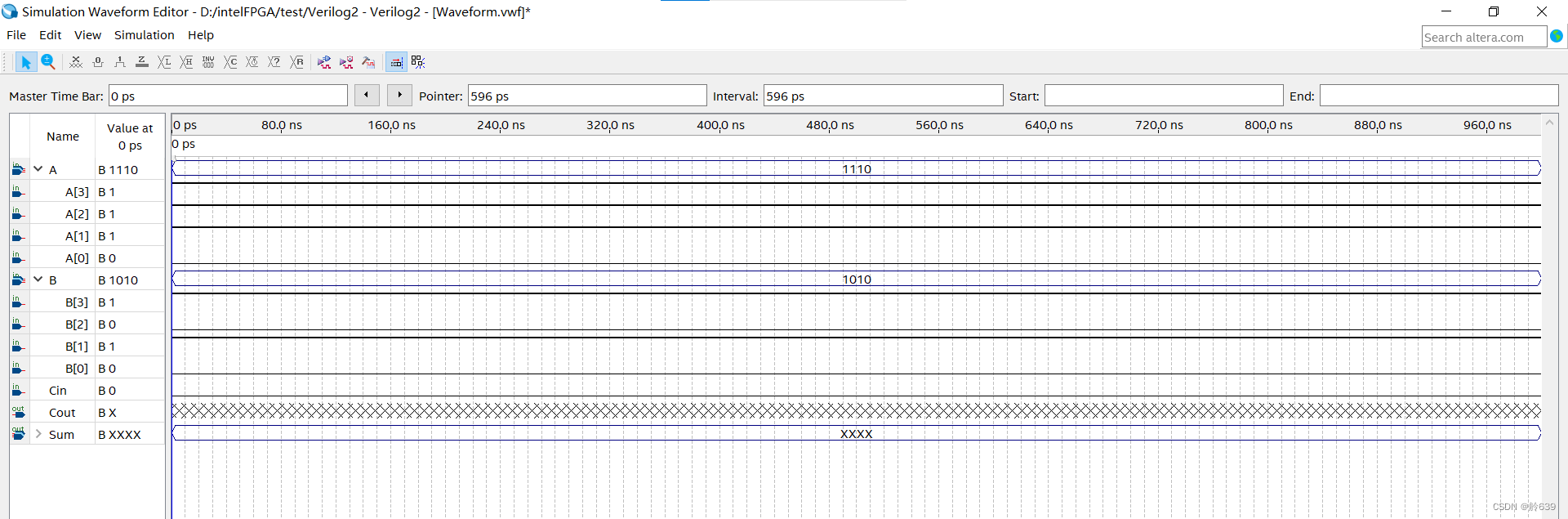

开始仿真,验证一下1110+1010

结果正确

2、4位全加器

(1)行为级

module Verilog2(

input [3:0] A,

input [3:0] B,

input Cin,

output [3:0] Sum,

output Cout

);

reg [3:0] Sum_int;

reg Cout_int;

always @(A or B or Cin)

begin

Sum_int = A + B + Cin;

Cout_int = (A[3] & B[3]) | (B[3] & Cin) | (Cin & A[3]);

end

assign Sum = Sum_int;

assign Cout = Cout_int;

endmodule

查看电路图

(2)门电路

module Verilog3(

input [3:0] A,

input [3:0] B,

input Cin,

output [3:0] Sum,

output Cout

);

// Internal signals

wire [3:0] X1, X2, X3, X4, X5;

wire Cout_int;

// XOR gates for Sum bits

assign X1 = A ^ B;

assign X2 = X1 ^ Cin;

assign Sum = X2;

// AND gates for carry generation

assign X3 = A & B;

assign X4 = B & Cin;

assign X5 = Cin & A;

// OR gate for Cout generation

assign Cout_int = X3 | X4 | X5;

assign Cout = Cout_int;

endmodule

(3)数据流

module Verilog4(

input [3:0] A,

input [3:0] B,

input Cin,

output [3:0] Sum,

output Cout

);

// Dataflow-style description using assignments

assign Sum = A + B + Cin;

assign Cout = (A[3] & B[3]) | (B[3] & Cin) | (Cin & A[3]);

endmodule

1352

1352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?