1. 实验目的

(1)熟悉使用Verilog HDL的三种不同描述方式进行基本门电路建模,实现数据扩展。

(2)学习使用Vivado进行逻辑设计的基本流程。

(3)学习使用Nexys4 FPGA硬件开发板,了解开发板主要的外围接口。

(4)了解设计源代码与仿真代码的区别。

2. 实验内容

(1)原理描述

基本与或非电路

(2)Verilog HDL设计源代码描述(要求:注释)

`timescale 1ns / 1ps

module lab1 (

input [1:0] SW,

output [3:0] LED

);

assign LED[0] = SW[0] ;//当SW[0]=1时LED[0]亮起

assign LED[1] = !SW[1];//当SW[1]=0时LED[1]亮起

assign LED[2] = SW[0] | SW[1];//当SW[0]或SW[1]中存在一个为1时LED[2]亮起

assign LED[3] = SW[0] & SW[1];//当SW[0]或SW[1]中全都不为0时LED[3]亮起

endmodule这是一个用Verilog编写的代码模块,用于描述数字电路。

timescale指令指定设计中使用的时间单位和精度。在这种情况下,时间单位是1纳秒(ns),精度是1皮秒(ps)。

module关键字表示模块定义的开始。模块具有名称(在本例中为“lab1”)和圆括号中的输入和输出端口列表。在本例中,模块具有两个输入:SW[1:0]和四个输出:LED[3:0]。

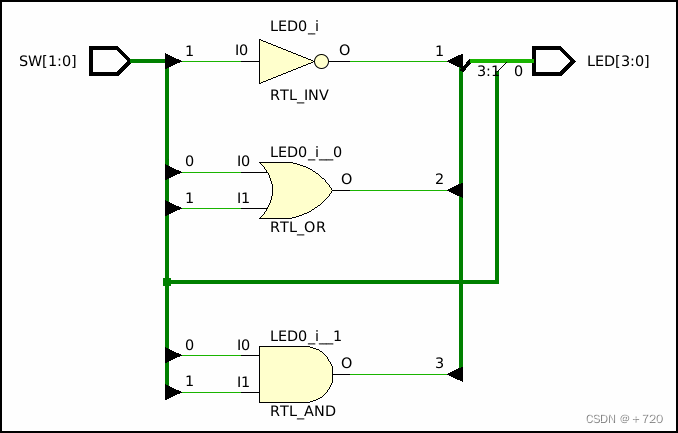

assign语句用于描述输入和输出端口之间的互连。在这些特定的赋值中,输出端口LED[0]连接到输入端口SW[0],LED[1]连接到SW[1]的反向,LED[2]连接到SW[0]和SW[1]的逻辑OR,LED[3]连接到SW[0]和SW[1]的逻辑AND。

endmodule关键字表示模块定义的结束。

总的来说,此模块描述了具有两个输入开关和四个输出LED的数字电路。LED的行为由输入开关的状态决定,如assign语句中所述。

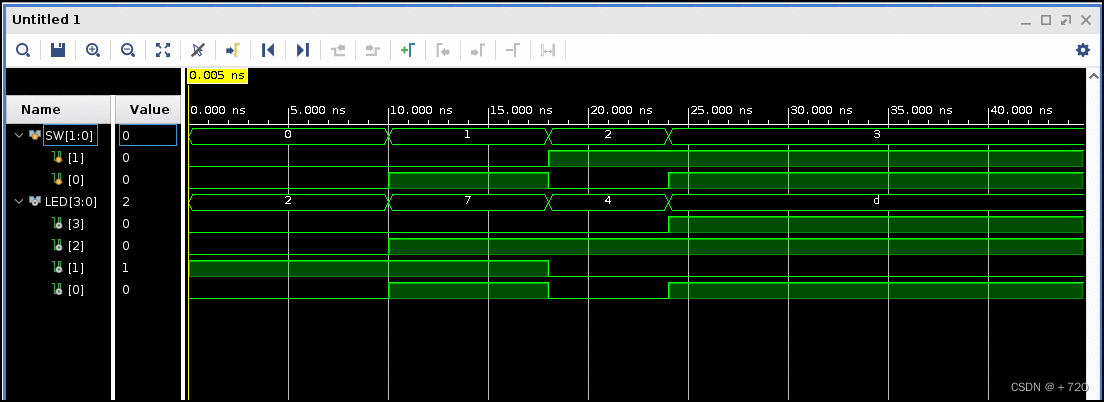

(3)TestBeach仿真代码及仿真结果

`timescale 1ns / 1ps

module lab1_testbench() ;

reg [1:0] SW;

wire [3:0] LED;

lab1 U1(

. SW(SW),

. LED (LED)

);

initial begin

SW = 2'b00;

#10 SW = 2'b01;

#8 SW = 2'b10;

#6 SW = 2'b11;

end

endmodule

(4)XDC文件配置

set_property PACKAGE_PIN N14 [get_ports {LED[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[3]}]

set_property PACKAGE_PIN J13 [get_ports {LED[2]}]

set_property PACKAGE_PIN K15 [get_ports {LED[1]}]

set_property PACKAGE_PIN H17 [get_ports {LED[0]}]

set_property PACKAGE_PIN L16 [get_ports {SW[1]}]

set_property PACKAGE_PIN J15 [get_ports {SW[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SW[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {SW[0]}]配置文件说明:

set_property命令用于设置所实现设计的各种设计属性。在这些特定命令中,为各种端口(例如LED[3]、LED[2]、LED[1]、LED[0]、SW[1]和SW[0])设置PACKAGE_PIN属性。PACKAGE_PIN属性指定目标设备上的物理引脚应连接到哪个特定端口。

get_ports命令用于获取与特定模式匹配的端口列表。在这些命令中,模式是端口名称,例如LED[3]、LED[2]、LED[1]、LED[0]、SW[1]或SW[0]。

还为一些端口设置了IOSTANDARD属性。IOSTANDARD属性指定特定端口应使用的输入/输出标准。值LVCMOS33表示应为指定端口使用低压 CMOS 3.3V标准。

上述文件是在硬件设计中为某些LED和开关设置物理引脚分配和输入/输出标准。很可能,所实现的设计包括具有可编程 I/O引脚的FPGA或ASIC设备(此处位nexys4),并且这些命令用于指定在设计中如何使用引脚。

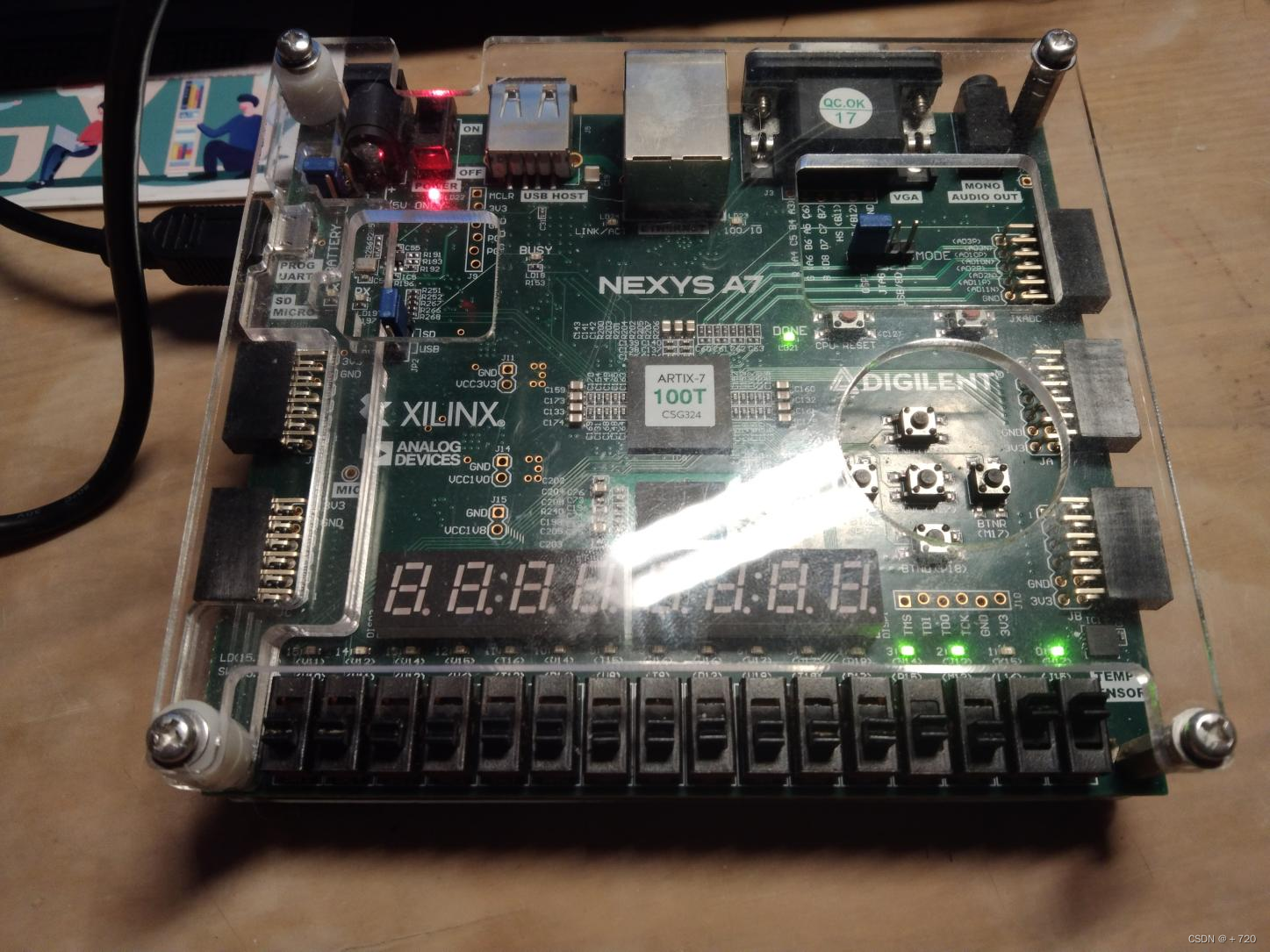

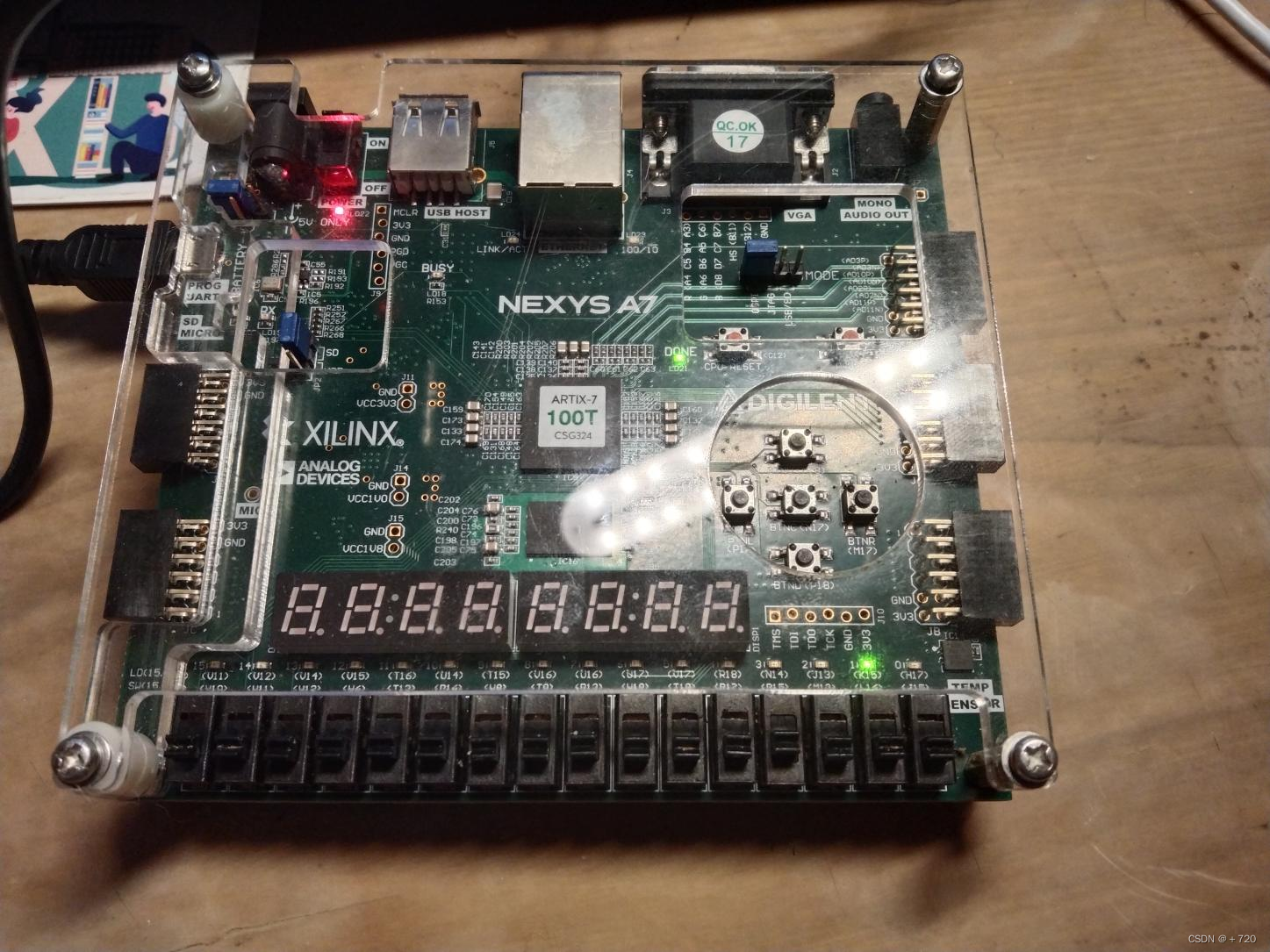

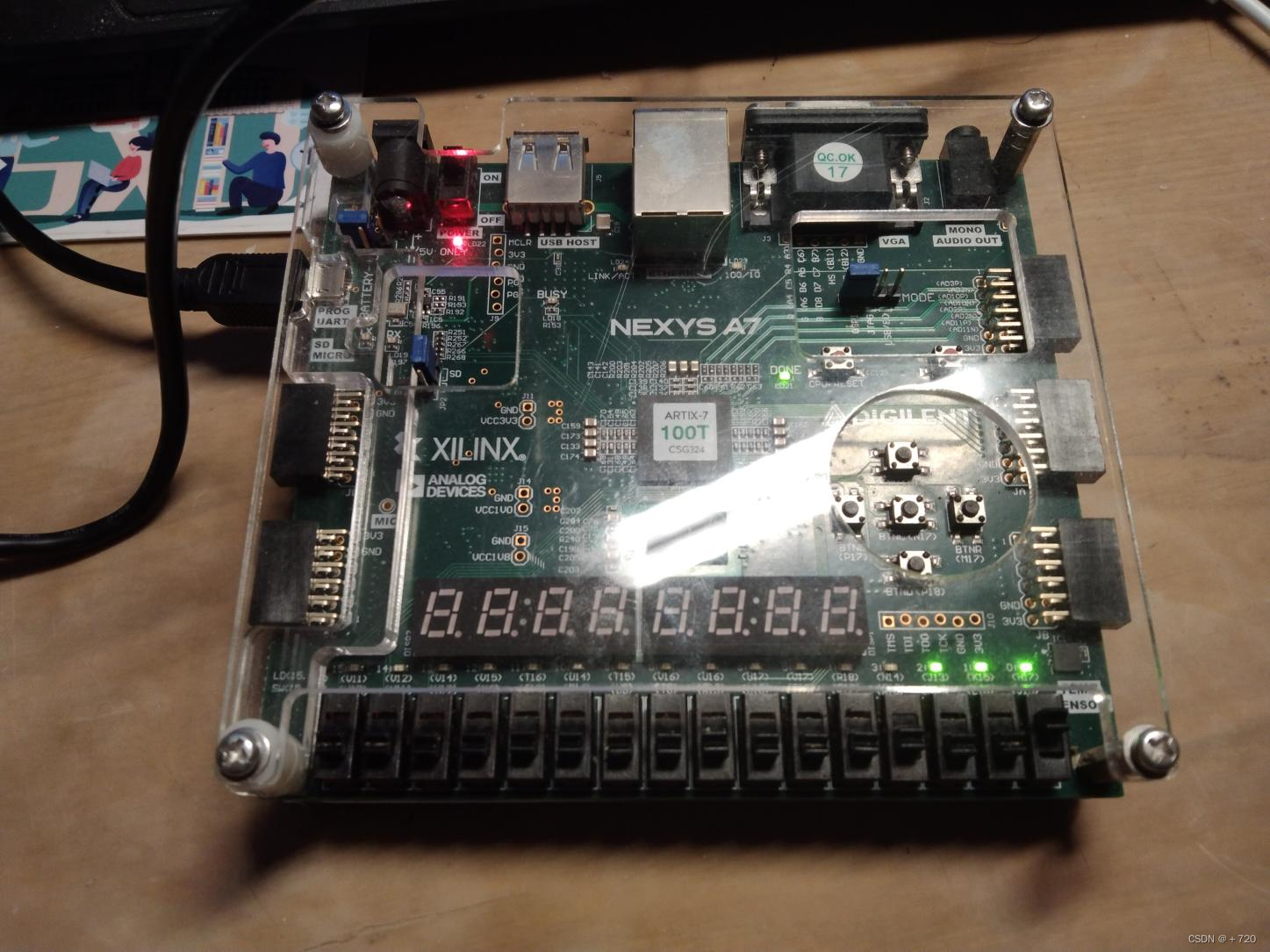

(5)下板测试

239

239

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?