在做Verilog验证时,如果设计的规模不大,那我们可以搭建一个testbench来验证设计。如果验证的模块有很多参数,那么我每验证一个case,都需要改一些参数,这样效率会很低,而且很容易出错。很容易出现debug半天发现自己的某一个参数和reference的参数设置的不一样。下面提出了自动从reference生成的文本中读取参数,保证了reference和dut的参数一样,可以减少错误,提高验证效率。

该方法的思想是把文本中的参数读到一个数组中,然后去索引,实现中用了一些system Verilog的语法。

比如一个文本中放了若干参数:

这些参数都是模块要用的,以下是一些数据类型定义。

以下33到43定义 了文件目录的句柄。

43--56把文本中的参数读到数组para_array中,一个参数名对应一个参数。在读取过程中用了sformat做字符串拼接,拼出参数文本的路径。

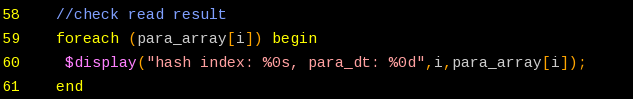

58--61用了sv的foreach语法,打印了数组中的参数,可以视检以下参数读取是否正确。

以下就是用参数名去索引参数。

2462

2462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?