总有小伙伴问我:“原型验证系统和硬件仿真器,哪一个更好?”

为什么会有这样的选择困难呢?实在是现在的芯片规模太大、太复杂了。

随着AI、5G等新技术的不断推进,“万物互联”打造的美好生活之下,应用越来越多元,这也使得整个芯片设计行业产生了巨大的推动与变革。而摩尔定律又持续演进,一块芯片看着很小,就指甲盖那么大,却承载了数百亿颗晶体管。集成度越来越高,整个芯片复杂度也呈指数级增长,这也催生出对更大规模的SoC设计要求。最终使得整个芯片设计对EDA工具的要求与依赖也越来越高。

在整个芯片设计流程中,没有一个芯片工程师可以绕开验证这个环节。而针对这种大规模的SoC设计,被提及最多的便是原型验证系统和硬件仿真器。

回到开头的问题,我一直相信选择没有更好,只有更适合。选择的结果往往是从自己的需求出发。问问自己,设计芯片时的应用场景、设计目标、设计规模、调试需求……都是怎样的呢?全方面评估后再选择适合自己的验证工具吧!

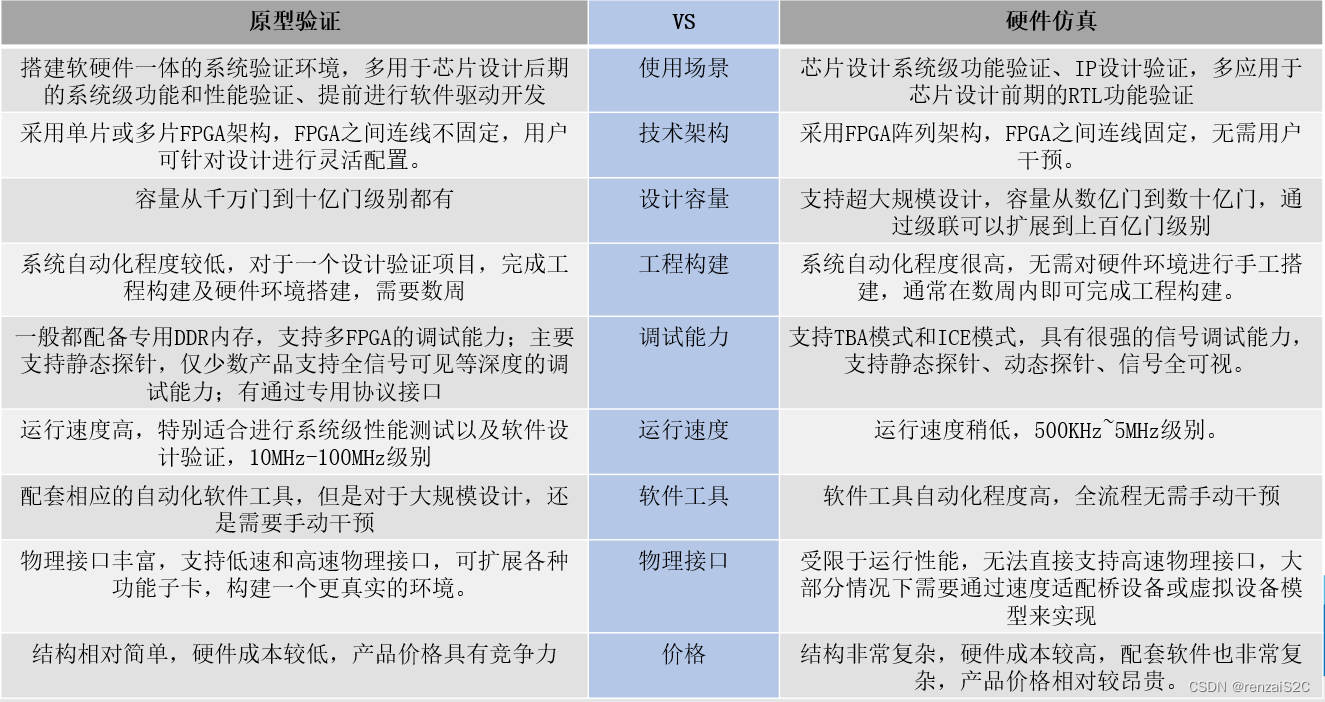

1、使用场景

原型验证系统是一种基于FPGA的芯片验证平台,它是通过将RTL移植到现场可编程门阵列来验证芯片功能。它会帮助工程师在芯片设计过程中搭建软硬件一体的系统验证环境,多用于芯片设计后期的系统级功能和性能验证。

也就是说,有了它,在流片前工程师们就可以在芯片的基本功能验证通过后,立刻开始驱动开发。甚至可以在流片前就给有需求的客户进行芯片演示,进行预售。这就大大缩短了整个验证周期,加速了产品上市时间。

此外因为原型验证系统内部处理和真实芯片一样都是可以做并行运算,其高效性能可以透过硬件子卡对接真实数据来发现更多隐蔽的bug。相较之下, 仿真使用的激励源模型和真实数据是有一定差别。

而硬件仿真器却是对完整的芯片设计进行加速仿真并调试,包括芯片设计的系统级功能验证、IP设计验证,多应用于芯片设计前期的RTL功能验证。在IP子模块开发基本成熟时,需要拼接成整体系统,检查系统有没有深度错误或性能瓶颈,此时需采用硬件仿真器的深度调试能力。

硬件加速器根据架构分为两种: FPGA-Based架构的硬件仿真器,以及CPU-Based架构的硬件模拟器,本次主要讲的是FPGA-Based架构的硬件模拟器。

硬件仿真器中含有数量较多的探测仪器、信号记录器等,以记录系统电路运行的每一个时钟周期的数据,以便查找设计错误,因此信号全可视是硬件仿真器的关键特性。

与原型验证系统相比,硬件仿真器能对全芯片进行和芯片时序行为一致的硬件仿真,包括全芯片信号的提取,对全芯片的功能、性能、功耗进行系统级的验证与调试。

通常来说,设计前期大部分都在调试,适合使用硬件仿真器验证,而设计后期大部分都在进行回归测试,此时便适合用高性能原型验证系统验证。

2、设计容量及技术架构

原型验证系统更适合一些中小规模的设计,容量从千万门到十亿门级别都有,可以满足不同芯片设计规模和设计场景的多样化需求。采用单片或多片FPGA架构,FPGA之间连线不固定,工程师们可针对自己的设计进行灵活配置。

对比原型验证系统,硬件仿真器的设计容量就更大了,可以支持10亿门级以上的超大规模设计容量,通过级联甚至可以扩展到上百亿门级别。采用的是FPGA阵列架构,FPGA之间连线固定,是不需要工程师们干预的。

3、工程构建

硬件仿真器有着全自动化的软件设置实现流程,基本无需修改硬件连接配置,以及灵活多样的全系统仿真调试能力,包括:信号的追踪深度更深(达数十亿仿真周期)、信号的条件触发、动态探针插入、离线调试等。通常跑完大型项目只需几周。

而原型验证系统由于系统自动化程度较低,对于一个设计验证项目,完成工程构建及硬件环境搭建通常需要数周以上。

4、调试能力

硬件仿真器和原型验证系统之间还有一个关键区别便是调试。硬件仿真器支持TBA模式和ICE模式,具有很强的信号调试能力,支持静态探针、动态探针、信号全可视等。

而原型验证系统配备专用DDR内存,支持多FPGA的调试能力,实现与逻辑分析仪相当的高效调试。主要支持静态探针,仅少数产品支持动态探针和全信号可见等功能。此外,原型验证系统还配有通过专用协议接口,比如JTAG、Ethernet、PCle或者其他高速接口。

5、运行速度

不过,原型验证系统所具有的运行速度是硬件仿真器无法匹敌的。在验证时,运行的测试程序越多,对设计可靠性越有保障。原型验证系统可以在短时间内运行大量的测试向量,轻松可达10MHz-100MHz级别,而硬件仿真器运行速度稍低,500KHz~5MHz级别。

6、软件工具

虽然,中小规模的芯片设计,原型验证系统的执行速度可以说比硬件仿真器快了整整一个数量级。但一碰到10亿门级以上的超大规模设计,若原型验证系统依然想要保持原有的速度,必然对其软件工具和硬件设计提起了更高的要求。

尤其是当今AI、5G等新技术的盛兴,越来越多的芯片和电子器件被集成到同一系统中,以获得更高的计算能力。这些超大规模的复杂芯片设计,势必对验证提出了更大的挑战。

对于这种超大规模设计,硬件仿真器更具优势。因为它独有的、超大规模的硬件结构,尽可能地保证了RTL设计的完整性。有些硬件仿真器的供应商也会提供各种功能的软件开发包,来帮助加速整个验证效率,比如多芯片自动划分工具,针对该平台而优化的综合工具,在线调试工具,等等。

而原型验证系统面对大规模设计,想要不影响整个性能和速度的全系统验证,会选择使用多片FPGA芯片。但多片FPGA互联产生的问题又随之而来,比如低延迟并行I/O接口、高带宽Serdes接口、自动化分割、多片FPGA的信号调试、各种软硬件接口扩展方案,等等。这些都决定了原型验证系统需要更专门的设计,特别需要配套相应的自动化工具。

因为对于两三片FPGA以上的中大型设计,手工分割和优化的投入太大,还会存在潜在的人为错误。这就好比有自动挡的汽车不开,非得用手动挡的。对工程师来说既耗时又耗力,还需要相当的经验,相当划不来。

目前市场上,像思尔芯S2C的芯神瞳原型验证解决方案,兼具网表级和RTL级自动分割能力,可以很好地帮到工程师解决此类问题。甚至配备完整原型工具链,可与其他点工具如逻辑综合器结合做优化,实现更好的优化策略。

7、物理接口

物理接口的可扩展性通常是工程师们较为关心的问题。原型验证系统一般配有专用接口,可扩展各种功能子卡,构建一个更真实的环境,帮助找到软件仿真/硬件仿真器无法探测到的BUG。而由于运行性能较高,它还能支持1Gbps-26Gbps左右的高速物理接口,部分支持降速桥。硬件仿真器则受限于运行的性能,无法直接支持高速的物理接口。大部分情况下会通过速度匹配桥设备或虚拟设备模型来实现。

8、成本价格

所有的点都对比的差不多了,最后就要来看看两者的价格了。

相比于原型验证系统,硬件仿真器的价格就相对没有那么竞争力。因为它的结构非常复杂,容量也非常大,硬件成本较高,配套软件也非常复杂,产品价格也因此相对高昂。

其实,原型验证系统VS硬件仿真器这两者从不是二选一的抉择。原型验证系统的本质是进行源代码验证和软件开发的功能模拟器,而硬件仿真器的本质是系统级源代码错误捕捉工具。更多时候,在芯片设计的不同节点,工程师所用的工具是不一样的。相信大家可以根据自己的实际情况,在正确的时间,在正确的使用场景中使用正确的工具!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?