引言

前面,我们介绍过对裸机程序进行RTL仿真,那些裸机程序规模比较小,只有几KB大小。

另外,我们也已经实现了针对O_board的SoC进行了RTL仿真(http://blog.csdn.net/rill_zhen/article/details/21190757),本小节,我们将实现在ML501平台上对linux进行RTL仿真。

1,DDR2仿真模型的修改

针对ML501的ORPSoC工程中,默认配置的DDR2的仿真模型与实际板子上使用的DDR2 SDRAM的参数不一致,我们要进行修改。

a,实际内存参数

要想对DDR2 SDRAM的仿真模型进行修改,我们首先要弄明白几个概念。

RANK,BANK,row,,column。这几个都是逻辑上的概念。

此外还有channel,module,chip,device等物理上的概念。

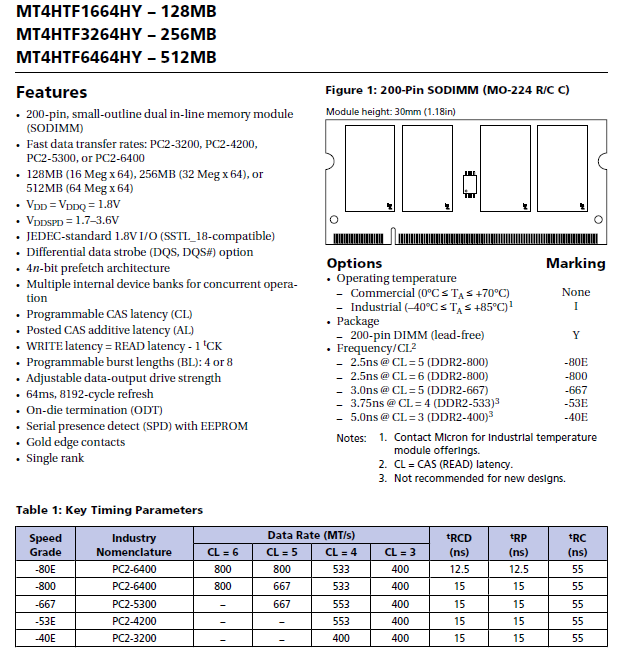

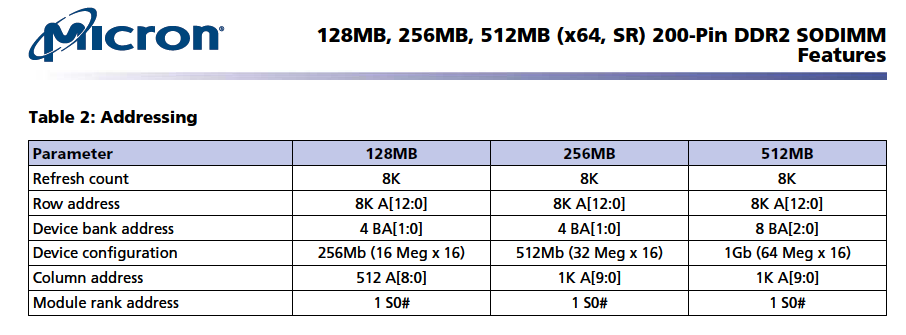

对于ML501使用的DDR2 SDRAM来说,其具体参数如下所示:

通过查看内存条,我们可以看到如下内容:MT4HTF3264HY-667F1 1RX16 256MB PC-5300S,

其中3263是指内存条的organization:32Megx64,x64表示整个内存条的数据线(DQ)宽度是64bit。

667表示内存条的speed grade。PC-5300也是speed grade。

1RX16表示内存条上面的4个device,每个数据宽度是16,16X4正好是64bit。

256MB,毫无疑问,表示内存条的容量是256M bytes。

通过内存条上面的标示,我们就可以获得很多信息,此外,通过查看其数据手册,我们会得到更详细的参数:

RANK:是single rank。

BANK:BA是2bit,说明bank数量是4,每个bank的大小是256MB/4=64MB。

row:宽度是[12:0],一共13bit。

column:宽度是[9:0],一共10bit。

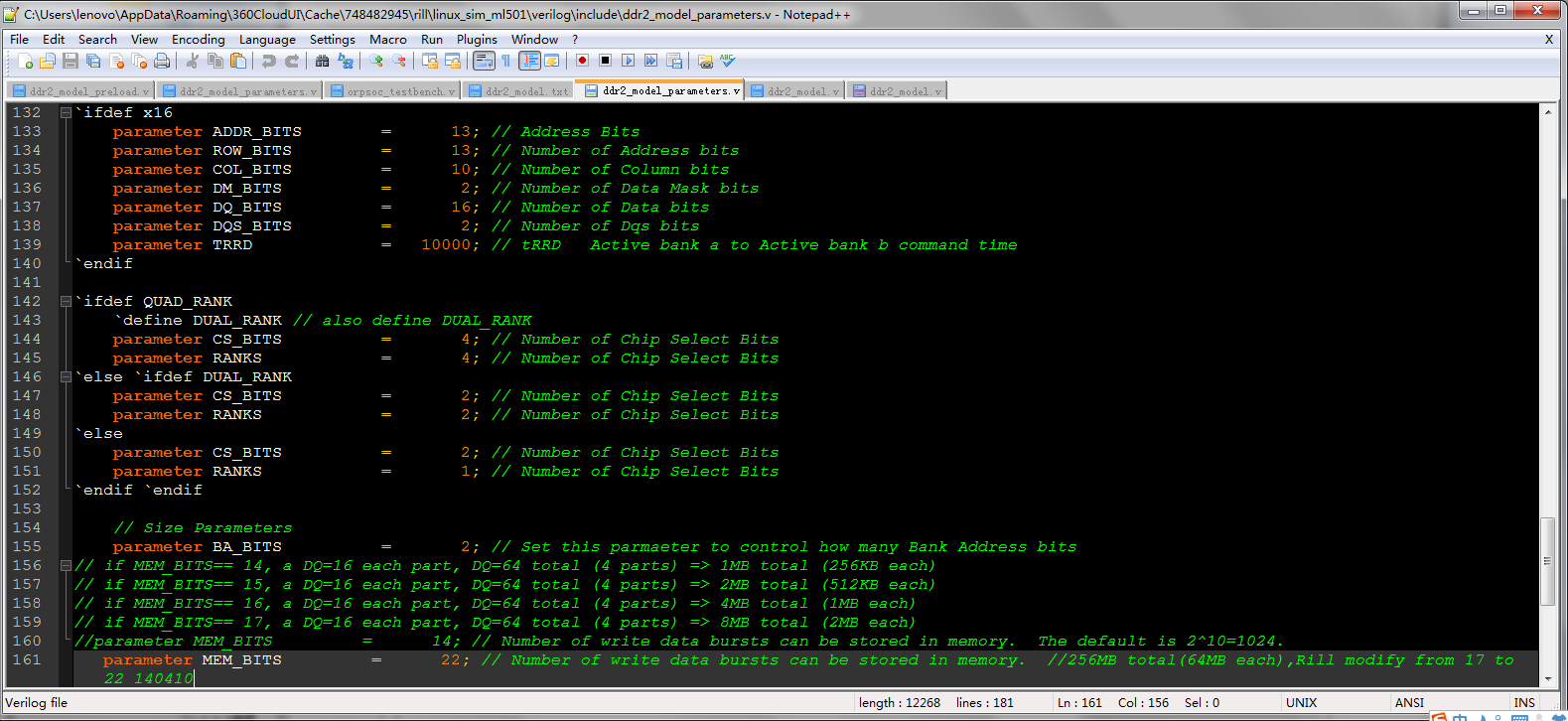

b,仿真模型参数

确定了我们实际使用的内存条的参数之后,我们就可以修改仿真模型的具体参数了。

需要注意的是ddr2_model.v只是一个timing model,具体的storage,需要我们自己根据实际情况来定。

这里需要修改的是MEM_BITS,由于ddr2_model.v是一个device的仿真模型,每个device中包含4个四分之一的bank,共64MB,所以对于如下定义:

// Memory Storage

`ifdef MAX_MEM

reg [BL_MAX*DQ_BITS-1:0] memory [0:`MAX_SIZE-1];

`else// [8 * 16 -1:0] [0:(1<<22) -1]==>26bit==>64MB

reg [BL_MAX*DQ_BITS-1:0] memory [0:`MEM_SIZE-1];

reg [`MAX_BITS-1:0] address [0:`MEM_SIZE-1];

reg [MEM_BITS:0] memory_index;

reg [MEM_BITS:0] memory_used;

`endif我们需要定义MEM_BITS为22,如下所示:

完整的参数,如下所示:

/****************************************************************************************

*

* Disclaimer This software code and all associated documentation, comments or other

* of Warranty: information (collectively "Software") is provided "AS IS" without

* warranty of any kind. MICRON TECHNOLOGY, INC. ("MTI") EXPRESSLY

* DISCLAIMS ALL WARRANTIES EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED

* TO, NONINFRINGEMENT OF THIRD PARTY RIGHTS, AND ANY IMPLIED WARRANTIES

* OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. MTI DOES NOT

* WARRANT THAT THE SOFTWARE WILL MEET YOUR REQUIREMENTS, OR THAT THE

* OPERATION OF THE SOFTWARE WILL BE UNINTERRUPTED OR ERROR-FREE.

* FURTHERMORE, MTI DOES NOT MAKE ANY REPRESENTATIONS REGARDING THE USE OR

* THE RESULTS OF THE USE OF THE SOFTWARE IN TERMS OF ITS CORRECTNESS,

* ACCURACY, RELIABILITY, OR OTHERWISE. THE ENTIRE RISK ARISING OUT OF USE

* OR PERFORMANCE OF THE SOFTWARE REMAINS WITH YOU. IN NO EVENT SHALL MTI,

* ITS AFFILIATED COMPANIES OR THEIR SUPPLIERS BE LIABLE FOR ANY DIRECT,

* INDIRECT, CONSEQUENTIAL, INCIDENTAL, OR SPECIAL DAMAGES (INCLUDING,

* WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION,

* OR LOSS OF INFORMATION) ARISING OUT OF YOUR USE OF OR INABILITY TO USE

* THE SOFTWARE, EVEN IF MTI HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH

* DAMAGES. Because some jurisdictions prohibit the exclusion or

* limitation of liability for consequential or incidental damages, the

* above limitation may not apply to you.

*

* Copyright 2003 Micron Technology, Inc. All rights reserved.

*

****************************************************************************************/

// Parameters current with 512Mb datasheet rev N

// Timing parameters based on Speed Grade

// SYMBOL UNITS DESCRIPTION

`define sg37E

`define x16

//`define MAX_MEM

`ifdef sg37E

parameter TCK_MIN = 3750; // tCK ps Minimum Clock Cycle Time

parameter TJIT_PER = 125; // tJIT(per) ps Period JItter

parameter TJIT_DUTY = 125; // tJIT(duty) ps Half Period Jitter

parameter TJIT_CC = 250; // tJIT(cc) ps Cycle to Cycle jitter

parameter TERR_2PER = 175; // tERR(nper) ps Accumulated Error (2-cycle)

parameter TERR_3PER = 225; // tERR(nper) ps Accumulated Error (3-cycle)

parameter TERR_4PER = 250; // tERR(nper) ps Accumulated Error (4-cycle)

parameter TERR_5PER = 250; // tERR(nper) ps Accumulated Error (5-cycle)

parameter TERR_N1PER = 350; // tERR(nper) ps Accumulated Error (6-10-cycle)

parameter TERR_N2PER = 450; // tERR(nper) ps Accumulated Error (11-50-cycle)

parameter TQHS = 400; // tQHS ps Data hold skew factor

parameter TAC = 500; // tAC ps DQ output access time from CK/CK#

parameter TDS = 100; // tDS ps D

本文介绍了如何基于ORPSoC在ML501平台上进行Linux的RTL仿真。主要内容包括DDR2仿真模型的参数修改,如内存参数、仿真模型参数和preload的调整,以匹配实际DDR2 SDRAM的配置。通过验证,确保仿真结果与硬件下板一致,展示了RTL仿真在理解Linux启动过程中的硬件时序优势。

本文介绍了如何基于ORPSoC在ML501平台上进行Linux的RTL仿真。主要内容包括DDR2仿真模型的参数修改,如内存参数、仿真模型参数和preload的调整,以匹配实际DDR2 SDRAM的配置。通过验证,确保仿真结果与硬件下板一致,展示了RTL仿真在理解Linux启动过程中的硬件时序优势。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6016

6016

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?