A common source of errors: How to avoid making latches

Syntactically-correct code does not necessarily result in a reasonable circuit (combinational logic + flip-flops). The usual reason is: “What happens in the cases other than those you specified?”. Verilog’s answer is: Keep the outputs unchanged.

语法正确的代码并不一定会产生合理的电路(组合逻辑+触发器)。通常的理由是:“在你指定的情况之外会发生什么?”Verilog的答案是:保持输出不变。

This behaviour of “keep outputs unchanged” means the current state needs to be remembered, and thus produces a latch. Combinational logic (e.g., logic gates) cannot remember any state. Watch out for Warning (10240): … inferring latch(es)" messages. Unless the latch was intentional, it almost always indicates a bug. Combinational circuits must have a value assigned to all outputs under all conditions. This usually means you always need else clauses or a default value assigned to the outputs

这种“保持输出不变”的行为意味着需要记住当前状态,从而产生一个锁存器。组合逻辑(例如,逻辑门)不能记住任何状态。注意警告“Warning (10240): … inferring latch(es)”消息。除非锁存器是故意的,否则它几乎总是表明有漏洞。在所有条件下,组合电路必须为所有输出分配一个值。这通常意味着您总是需要为输出分配else子句或默认值

以如下两种情况为例

未正确使用if语句

未正确使用case语句,缺少default项

示例:

A 错误示例

//How to avoid making latches

//make lathes

module NO_latches (

input d,

input c,

output reg q,

input [1:0]a,

output reg b

);

always @(*) begin //保持原来的值产生锁存器

if (d)

q = c;

end

always @(*) begin

case(a)

2'b00:b = 1'b0;

2'b11:b = 1'b1;

endcase

end

endmodule

RTL Viewer

if 语句和 case语句都综合得到了锁存器

B 没有锁存器示例

//How to avoid making latches

//NO lathes

module NO_latches (

input d,

input c,

output reg q,

input [1:0]a,

output reg b

);

always @(*) begin //保持原来的值产生锁存器

if (d)

q = c;

else

q = 1'b0;

end

always @(*) begin

case(a)

2'b00:b = 1'b0;

2'b11:b = 1'b1;

default:b = 1'b0;

endcase

end

endmodule

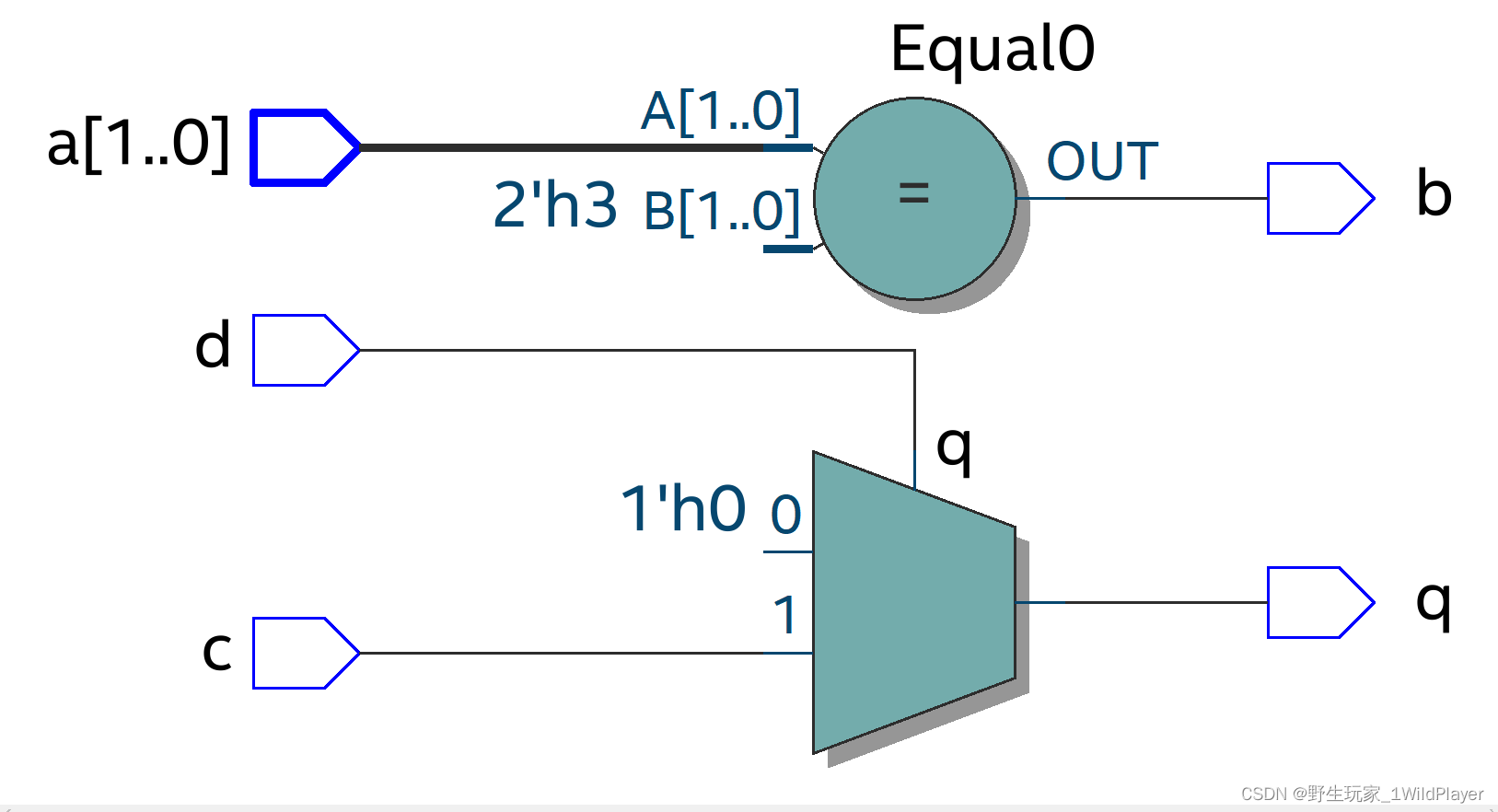

RTL Viewer

if 语句和 case语句都没有综合得到锁存器

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?