一、PCB层叠结构

1、层叠结构设计的先决条件层叠结构的设计,需预先获取以下信息:

①单板总层数,包括信号层、电源层、地层的数目。

②单板厚度。

③单端信号和差分信号的目标阻抗。

④PCB的介电常数。

(1)单板层数确定

设计者需根据单板尺寸、单板规模,如信号数目、电源种类等,以及EMC的要求粗略估计单板的信号层、电源层、地层的数目,从而获得单板的总层数。总层数越多,布线越方便,EMC性能越好,但成本也相应提高。

(2)单板厚度

在机框式通信产品中,单板沿导轨插入机框,因此厚度与导轨宽度有关,同时单板的厚度还取决于总层数等因素。

(3)目标阻抗

从信号完整性考虑:要求在信号传输路径上实现阻抗的匹配。

(4)介电常数和材质正切值

为材质介电常数与真空介电常数的比值。介电常数是表征电磁场在特定材质中导通能力的参数,介电常数越大,则电磁场在该材质中导通的能力越强。

越高,高频信号越容易通过,即高频的损耗越大。

材质正切值也称为材质损耗正切值,与

相同,它也是一个与信号完整性相关的参数。

值越大,则信号的损耗越大。在高速电路设计中,应尽量选择

和

小的材质。

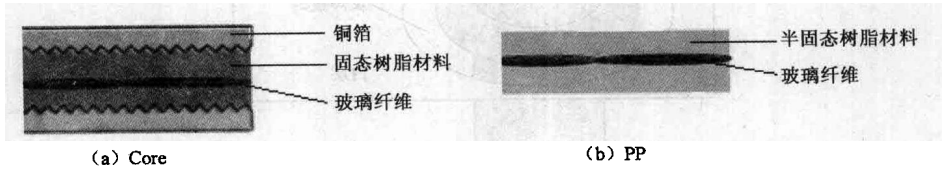

2、Core和PP

Core的两个表层都铺有铜箔,可作为信号层、电源层、地层等导电层,Core的上、下表层之间填充的是固态材料;PP的表面不铺铜箔,在PCB中起填充作用,其材质是半固态的树脂材料。在制作多层板时,需配合使用Core和PP,一般在两个Core之间应选用PP作为填充物。

二、PCB信号完整性设计

一般而言,完整性SI与以下几个因素有关:反射、串扰、辐射。反射是由信号传输路径上的阻抗不连续造成的;串扰与信号的间距有关;而辐射则与高速器件自身以及PCB设计均有关。阻抗匹配是影响信号完整性最主要因素。

1、信号反射

信号的有效频率取决于信号的边沿速率,当信号的有效频率

比较低,使得信号的有效波长

如小于信号走线长度的6倍时,该信号线路可被视为传输线。对于传输线必须考虑阻抗不匹配所造成的反射,反射系数计算公式:

为反射点之后线路阻抗

为反射点之前线路阻抗

例如:假设周期频率10MHz,上升沿时间0.5ns,走线长度6in(英寸)。

判读是否为传输线:

由于信号走线长度为6in,大于的1/6(2in),以此视为传输线,必须考虑阻抗不匹配所造成的反射。

始端、传输路径、终端阻抗的不匹配,都会造成信号的反射。为减小反射,需尽可能地减小反射系数,即要求

尽可能地等于

。

2、阻抗匹配设计

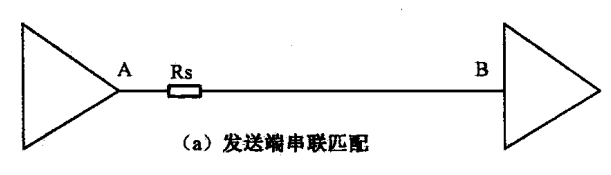

(1)发送端串联匹配

单点对单点的信号连接,应采用发送端串联匹配。该匹配方式使发送端器件输出阻抗与发送端匹配电阻Rs的和,近似地等于传输线阻抗,这种匹配方式只是实现了发送端的匹配。

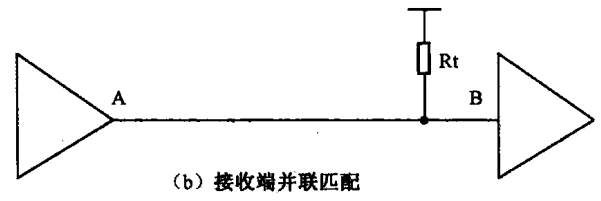

(2)接收端并联匹配

接收端并联匹配适用于单点对多点的连接,与发送端匹配不同,接收端匹配无须借助反射以建立电平,通过使匹配电阻Rt的阻值等于传输线阻抗,可实现接收端的阻抗匹配。改设计不会影响信号的边沿速率。存在接收端高、低电平不对称的问题。

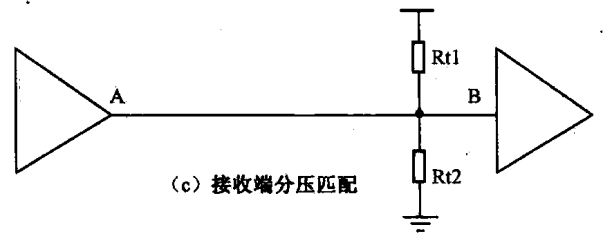

(3)接收端分压匹配

这是VPECL等高速电平常用的匹配方式,改设计不影响信号的边沿速率;较容易实现接收端高、低电平相对门限电平的对称分布,可满足接收端对共模偏置电平的要求。

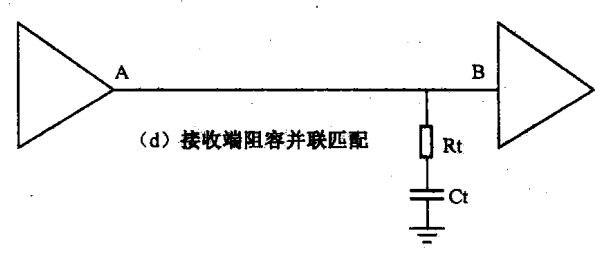

(4)接收端阻容并联匹配

在阻容并联匹配中,电容Ct可阻断该通路,有效地减小了功耗,一般取Rt的阻值与传输线阻抗近似相等,C选取几十至几百皮法的陶瓷电容即可。由于C的存在,将使信号的边沿变缓同时存在接收端高、低电平不对称的问题。

三、PCB散热设计

在高速电路设计中,对散热的考虑应结合几个要点:器件自身的功耗、器件功耗对周围器件的影响、散热通道。

1、器件自身的功耗在概要设计阶段,设计者应对板上关键器件的最大功耗进行估计,根据该估计值,评估风扇风力、散热片是否足够。

2、器件功耗对周围器件的影响晶振、存储器、Y5V型的电容等器件,都属于温度敏感器件,在设计时,应尽量远离电源模块、LDO、高功耗器件等热源。

3、散热通道:散热片的锯齿突起要与风向垂直;连接器的排列方向与风向垂直;高功耗器件要处于出风口;高个器件摆放时注意防止阻挡低个器件风向。

四、PCB设计的ESD防护

1、ESD防护器件

(1)TVS管

TVS管指电压型瞬态抑制二极管,一般并联在被保护线路之中。在功能上,TVS管与稳压二极管相似,当输入电压突然增大,超过阈值电平时,TVS管反向导通,并提供快速的电流泄放通道,从而将电压钳位在安全区域,后级电路得到保护,而当输入电压恢复正常后,TVS管又能迅速地回到反向截止状态,不影响后级电路的正常工作。

主要参数

:最高反向截止电压。当两端电压低于

时,TVS管处于截止状态,管内仅有极小的反向漏电流

流过。对TVS管的选型,

应高于差分对信号正常工作时的差分电平。

:最低导通电压。当两端电压高于

时,TVS管进入导通状态,此时管内流经的电流为

。

:峰值电流。TVS管所能承受的最高电流,TVS导通的电流达到

时,两端电压达到最高钳位电压

。根据产品的测试标准,选择

参数。

:寄生电容。由于容性的影响,差分信号边沿速率将降低,权衡

对差分对信号质量的影响。

:反向漏电流应不影响差分对信号的正常工作。

(2)压敏电阻

压敏电阻指在一定电流和电压范围内,阻值随两端电压而变化的器件。压敏电阻一般并联在电路中,其保护机理与TVS管类似,当输入电压突然增大且超过阈值时,压敏电阻能将电压钳位到某稳定的电压值。压敏电阻的寄生电容相对较大,不建议用于高速接口。

(3)气体放电管

气体放电管一般并联于接口信号的前端,其工作原理是,当放电管两端的电压超过阈值时,放电管击穿导通,两端电压降低,电荷快速地通过管体,从而实现了对后级电路的保护。两端电压恢复正常后,气体放电管恢复为断路,不对后级电路的工作造成影响。气体放电管对高速信号的影响也是最小的。

| 高 | 中 | 低 | |

| 响应速度 | TVS管 | 压敏电阻 | 气体放电管 |

| 通流能力 | 气体放电管 | 压敏电阻 | TVS管 |

| 寄生电容 | 压敏电阻 | TVS管 | 气体放电管 |

| 反向漏电流 | 压敏电阻 | TVS管 | 气体放电管 |

2、遵循原则:

原则一,使响应速度最快的TVS管最靠近被保护的器件,而通流能力较强的气体放电管和压敏电阻则放置在接口的前端。即由接口的前级到后级分别放置:气体放电管、压敏电阻、TVS管。

原则二,高速设计中应考虑保护器件的寄生电容对高速信号的影响。一般不建议在高速信号上使用压敏电阻。是否使用TVS管,需仿真其寄生电容对接口信号眼图、回损等参数的影响。

原则三,保护器件应就近放置于接口信号的主线路上,不能通过长引线连接到接口信号上。

五、PCB设计的EMC防护

EMC包括EMI和EMS两项:

EMI,即电磁干扰,指电子设备(或电子元器件)在工作时,产生的不利于其他设备(或元器件)的电磁能量。I的测试项目包括传导干扰(CE)、辐射干扰(RE)、谐波干扰等。

EMS,即电磁敏感度,指电子设备(或电子元器件)在工作时,应能承受的外部其他设备(或元器件)的电磁干扰能量。EMS的测试项目包括传导敏感度(CS)、辐射敏感度(RS)、静电放电(ESD)、浪涌(Surge)、电压跌落测试(DP)等。

EMC针对的电压波动量级是微伏级,应用的原理是传输线效应原理和天线原理,其设计关注点为传导、辐射、瞬态干扰等。EMC的设计方法可分为以下四点:屏蔽、隔离、滤波、接地。

1、解决EMC设计要点:

(1)20H和3H原则

20H原则:为了减小单板的边缘辐射,要求电源层相对地层内缩一定距离,假定电源层与最近的地层之间的材质厚度是H,则内缩距离要求为20H,电磁能量的70%将被限制在板内。

3H原则:长距离平行走线的信号线之间的间距应达到3H,信号线走线距离参考平面的边界应达到3H,其中,参数H是指信号层到参考层之间的材质厚度。

(2)法拉第电笼

法拉第电笼:在单板的边缘,每隔100~200mil,打一个与内层地平面相连的地孔。走线时需注意,不能将信号走线到电笼之外。在表层推荐用一条宽度为200~400mil的地线将这些地过孔连接,在信号层,推荐用一条宽度为20-40mil的地线将地过孔连接,但不建议连线成环路。

(3)表层铺地

在表层做大面积铺地,以起到对第二层及倒数第二层的电磁屏蔽作用。表层铺地时,必须充分地打地过孔,严禁出现孤立的铜箔。因为,当表层铜箔接地不充分时,将表现为天线,不仅没起到屏蔽的作用,反而加强了对外的辐射。

(4)散热片接地

散热片的接地,同样要求在接地铜箔上充分地打地过孔,以防散热片成为对外辐射的天线。

(5)晶振处理

晶振等时钟源是产生辐射的重要源头,PCB设计时需注意将其与单板上的其他线路进行隔离。有以下要点需注意:

要点一,滤波。使用磁珠与电容为晶振的电源引脚滤波,并使电容紧贴晶振等时钟器件的电源引脚放置。

要点二,在表层,晶振下方做挖空铜箔处理,不得走线或铺电源平面。

要点三,紧贴表层的第二层,若不是地层,则应在对应晶振的区域内做铺地处理,并用多个地过孔与地层相接。

(6)走线与安装孔保持距离

单板上的安装孔、定位孔等是电磁能量向外辐射的通道,因此需使走线尽量地远离这些孔,推荐走线与安装孔等保持30mil以上的距离。

(7)避免尖角走线

尖角走线除阻抗不连续外,尖角还能成为辐射的天线,因此,从MC的角度而言,也应避免尖角的出现。

(8)在LC滤波电路上增加串联电阻,以减小电路品质因素Q

电路品质因素计算公式:

R越大,则Q越小,从而减小电路振荡。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?