芯动

1、用UVM的意义是什么?UVM的好处在于什么?

UVM提供了一套标准的类库,为用户提供了开发建构具有高复用性和高性能架构的验证环境所需的所有基本模块;

UVM提供了一套完善的运行机制,从复用性,完备性等方向提升了验证效率:包括factory机制,config机制,phase机制,objection机制,sequence机制,寄存器抽象层(RAL),事务级建模(TLM)等。

2、UVM的重用性通过哪些机制体现?

第一,通过factory机制override,但是sv也有。

第二,通过callback机制进行重载,可以用于异常激励测试/修正不同项目的差异。

3、UVM端口的连接方式,数据传输方式?

UVM主要通过TLM进行通信。

端口可以分为

- port、export、import:一对一通信、有阻塞之分

- analysis_port、analysis_export、analysis_imp:一对多广播、无阻塞之分

端口的连接需要在connect_phase中进行connect。

数据传输

- 对于put系列端口有put、try_put、can_put等操作,对于get系列端口有get、try_get、can_get等操作;

- 对于analysis_port和analysis_export来说只有一种操作:write,在analysis_port的run_phase中调用,在analysis_imp所在的组件中定义一个名为write的函数

4、在项目中如何对寄存器进行验证?

使用uvm内建测试序列对寄存器访问进行测试,比如reg_access可以验证是否能够访问内部寄存器,bit_bash测翻转情况,hardware_reset测复位前后寄存器的读取情况。

5、你了解哪些常用的验证手段?

UVM、FPGA原型验证

6、并发断言和立即断言的区别?

- 并发断言:并发断言与时序有关,可以放在过程块、模块、接口或者一个程序中,可以在静态(形式)验证和动态模拟(仿真)工具中使用,有关键词property

a_ib:assert property(@(posedge clk) not(a&b));

- 立即断言:立即断言与时序无关,必须放在过程块中,只能用于动态模拟(仿真),无关键词property

always_comb begin a_ia: assert(a&b); end

7、 怎么去单纯的检测一个单比特信号的序列是否是我期望的序列?

序列检测类问题,可以使用移位寄存器,比如以检测序列10010为例,直接使用一个5位的寄存器寄存每一个bit流,并在下一个时钟周期移位,再与期望序列进行对比。

8、在makefile里怎么调用一个shell

两种形式

- 为了获取命令在shell环境中的执行结果:利用$(shell command)作为基本结构

CUR_DIR := $(shell pwd) CUR_TIME := $(shell date) FILE_LIST := $(shell ls *.c) all: @echo $(CUR_DIR) @echo $(CUR_TIME) @echo $(FILE_LIST)运行结果为:

/home/cv/test 2021年 7月19日 星期一 19时58分25秒 CST /home/cv/test/src/playground.c /home/cv/test/src/template.c

- 单纯执行指定的命令以进行特定的操作

all: mkdir build clean: rm hello_test build/*.o用在基本规则格式的 command 处,例如打印信息、创建文件夹、删除中间文件等等。

9、makefile怎么把用例名testname传递到环境里面去?

首先声明TESTNAME ?= 例名,然后再RUN中添加$(OUT)/sim/$(TESTNAME)_$(SEED).log

和 +UVM_TESTNAME=$(TESTNAME),这个是默认的,在编译时可以通过TESTNAME = XXX进行修改,然后加上CM_MAKE ?= $(TESTNAME)_$(SEED)

10、VCS都有哪些编译方式?从编译到运行都有哪些步骤?

VCS编译主要分三步,分别是Analysis、Elaboration和Simulation。

- 首先make vlog分析verilog代码

- 然后make uvm生成uvm库文件、make testbench生成顶层tb库文件,make elab编译生成simv文件

- 最后make run执行仿真

大普微

1、验证中验证点分解原则

测试点分解原则:测试点必须覆盖所有规格feature,一个测试点必须在一条tc中覆盖,一条tc可以对应多个测试点

测试点分解方法:边界值验证,黑盒,对输入或输出的边界值进行测试。比如:数据长度为a-b,需验证长度为a-1、a、a+1、b-1、b、b+1。

测试点一般包含接口时序数据传输、寄存器访问、功能、场景、时钟复位、不同配置的工作模式、关键模块、异常测试等。

2、如何从spec中获取feature

基于接口、功能、性能和架构

3、assertion用在哪些地方,有哪些优点

断言可以用来与设计功能和时序作比较。

优点是可读性好,可以自由打开关闭,用来检测算法模型的断言在形式验证中可以穷尽计算,尽可能找出违例。

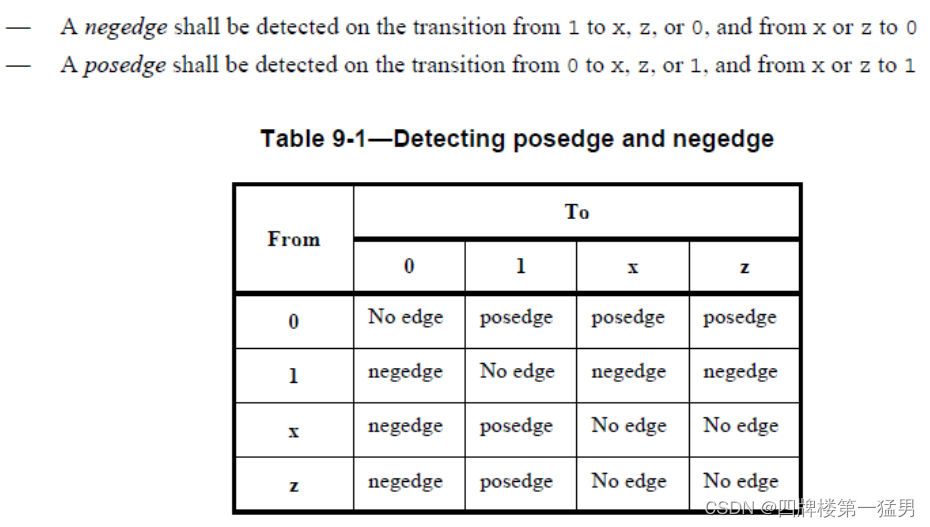

4、仿真时x/z出现在什么地方

产生x态的原因:四值逻辑默认值为x态,功能仿真时数组取值越界为x态,线网信号存在多个驱动,多个驱动之间相互冲突为x态。

产生z态的原因:综合把部分逻辑优化,导致网表中的输出端口无驱动。

5、 outstanding和out of order的理解

6、outstanding和out of order的应用场景

7、AHB与AXI优缺点比较

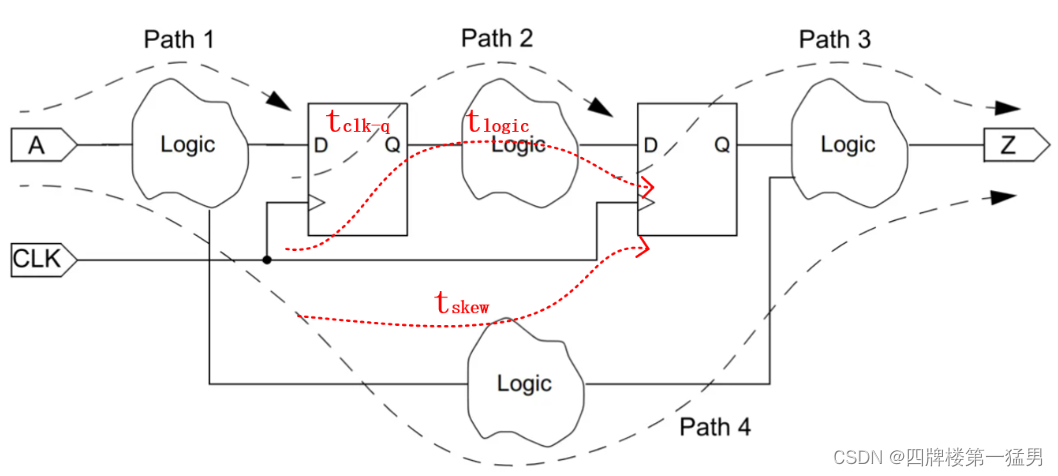

8、什么是建立时间,保持时间

建立时间是指信号在时钟有效沿到来之前需要保持稳定的时间。

其中tclkq是时钟源到q的时间,tlogic是寄存器的组合逻辑,tskew是前后寄存器边沿到达时间差,T为时钟周期。

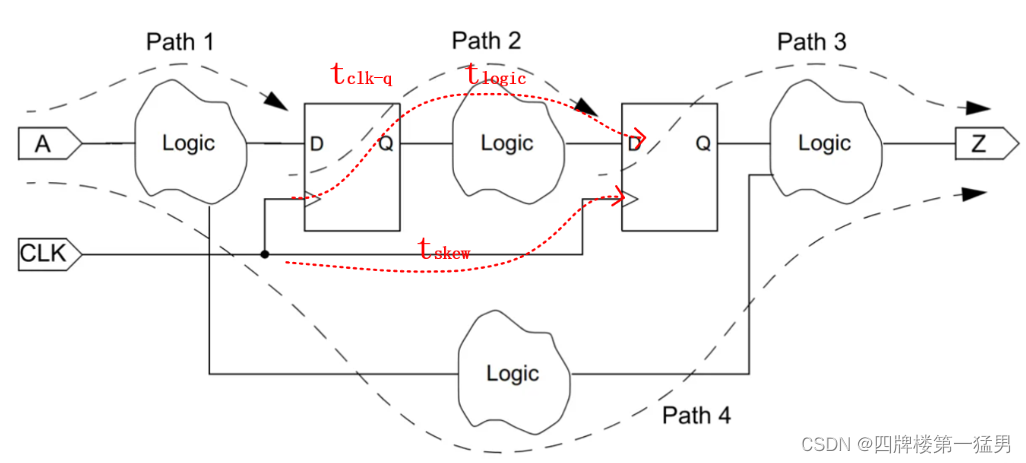

保持时间是指信号在时钟有效沿到达之后需要保持稳定的时间。

9、setup,hold如何修复

根据上面的公式可以看到,为了解决建立时间和保持时间违例,都应该让不等式的右边值尽量大。

建立时间可以:增大skew,clock通路上插上buffer,减少寄存器的组合逻辑,降低时钟频率以增加T,更换DFF期间以降低tclkq等。

保持时间可以:增大tclkq,换一些更慢的DFF,也可以增加tlogic组合逻辑的时间,减少tskew。

修复保持时间比修复建立时间要简单,只要在组合逻辑路径上插入buffer,就可以迅速解决保持时间违例。

10、为什么会产生保持时间违例

因为前面输出变化太快,导致信号稳定太慢,自动插入几个buffer即可解决这个问题。

11、 2个模块指定了各自的timescale,编译命令也指定了,以哪个为准

在编译过程中,`timescale指令影响这一编译器指令后面所有模块中的时延值,直至遇到另一个`timescale指令。

这里要特别注意,timescale的作用域以编译顺序来的,而不是instance层次结构。

模拟器总是定位在所有模块的最小时延精度上,并且所有时延都相应地换算为最小时延精度。

至于VCS的-timescale选项是防止编译的第一个源文件没有指定timescale用的:源代码文件中有的包括`timescale编译指令,有的不包括。

如果在VCS命令行中,不包括`timescale的源代码文件在最前面,VCS会停止编译。使用-timescale选项为这些在前面且又没有`timescale的源文件指定timescale。

VCS中还有一个-override_timescale选项,可以覆盖所有的源文件中的timescale设置。

12、 介绍验证仿真结构

- 在uvm中,仿真的时候,自动创建最顶层uvm_root实例,这个实例是唯一的。

- 然后通过run_test()方法会创建自己实现的test的实例并命名为uvm_test_top。

- test一般是包括env,然后在run phase调用virtual seq。virtual seq会挂载env里面的sqr,然后调用了各自agent里面的sequene库,实现了功能点对应的测试序列。

- env里面一般包括scoreboard,virtual sqr,agent,coverage model。virtual sqr里面都是对应agent里面sqr句柄的集合。coverage model负责采样功能覆盖率。

- scoreboard里面一般包含一个refmodel,还有一个作比较的compare。

- agent里面一般包括组件driver和moniter,sequencer,和object sequence库。driver负责通过sqr拿到sequence产生的item,然后解析item驱动interface。moniter负责检测interface的信号发给scoreboard或者其他模块。agent可以配置成active模式或者passive模式,passive模式下把driver和sqr disable掉,此时agent就只有monitor检测信号,这个agent永远不会驱动interface。sequence库里面一些基本的测试序列,这些序列负责产生item,比如单次写操作,单次读操作。然后通过sqr的接口,把item传给driver。

- 在uvm中,以上的test,env,agent,sqr,scoreboard,coverage model,driver,moniter是属于组件类继承与component,是在仿真开始前就搭建好起来的架构,整个仿真过程中保持不变,有build phase,run phase等自动运行的phase机制。而transaction,sequence,sequence item是属于object类,没有phase机制,是在仿真过程中随时创建并且消失的。

13、monitor传输是TLM机制吗

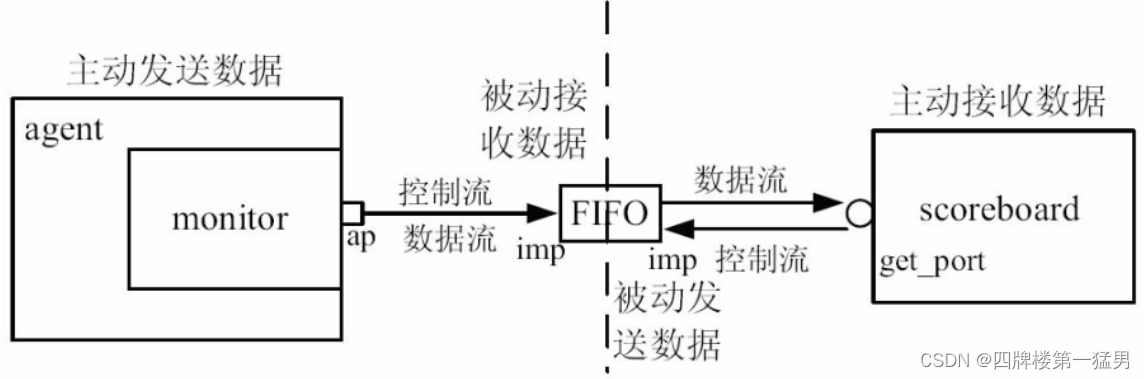

是的,一般使用TLM_FIFO实现monitor和scoreboard的通信。

FIFO的本质是一块缓存加上两个imp端口。

在monitor和FIFO的连接关系中,monitor为analysis_port,FIFO使用的是analysis_imp端口,数据流和控制流方向相同。

在scoreboard与FIFO的连接关系中,scoreboard中使用blocking_get_port端口,而FIFO使用的是一个get端口的imp。在这种连接关系中,控制流是从scoreboard到FIFO,数据流是从FIFO到scoreboard。

14、使用TLM FIFO的好处

第一个好处是不必在scoreboard中再写一个write的函数,scoreboard可按照自己的节奏工作,而不必跟着monitor的节奏。

第二个好处是FIFO的存在隐藏了imp。

第三个好处是可以轻易解决当reference model和monitor同时连接到scoreboard应如何处理的问题。

15、介绍TLM有几种机制

TLM有两个通信对象,分别为initiator和target,initiator作为通信请求发起方,target作为通信请求响应方;还有两个数据对象,分别为producer和consumer,producer作为数据生产方,consumer作为数据接收方。

TLM有三个通信端口,分别为port、export和imp,端口优先级port > export > imp。port作为控制发起端,而imp只能作为target接收请求的响应端。要注意连接时只能高优先级连接低优先级,并且三种端口并非组件类,只能使用new()在build_phase中创建,不能使用create。

TLM的通信方式可分为一对一传输和一对多传输。

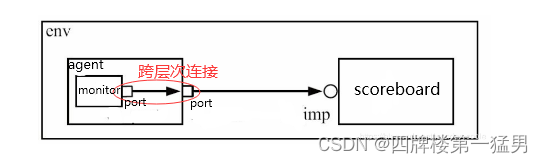

一对一传输可分为put()和get()的单向传输、transport()的双向传输和uvm_analysis_port的跨层次传输。

- 双向传输相当于一次put传输再加一次get传输,可以在同一任务调用过程中完成REQ和RSP的发出与返回。

- 而跨层次传输通常在agent中声明一个ap但是不例化,让其指向monitor的ap,在env中可以直接连接agent的ap到scoreboard的imp以实现monitor和scoreboard的通信。

一对多传输可以使用通信管道TLM FIFO和分析端口analysis port。

- uvm_tlm_fifo是继承于uvm_component的组件,其内部预留多个端口,其所带端口类型均为imp!

- uvm_analysis_port是最常用的一对多传输端口,在组件中以广播形式向外发送数据,其只有一个write()操作:

首先在component中定义analysis_port,在run_phase()中调用write函数

uvm_analysis_port #(transaction) ap; ap.write (tr);然后在订阅端(subscriber)定义write方法

最后在env中利用端口连接组件

compB.ap.connect(sub1.analysis_export); compB.ap.connect(sub2.analysis_export); compB.ap.connect(sub3.analysis_export);

中兴微

1、介绍实习项目

2、代码量是多少?团队有多少人?你负责了哪些部分?

3、如何确保项目已经验证完全,验证完备性

首先就是代码覆盖率和功能覆盖率的一个结合,要确保覆盖率达到百分之百,不能覆盖需要exclude的地方需要出具详细报告并且说明为什么,比如default条件无法到达的情况。

然后就是要多review,每走完一个流程都要和设计以及架构一起review验证功能点,tc以及波形。

4、代码覆盖率中收集了哪些覆盖率,没有覆盖到的是哪些地方,是如何考量的?没有覆盖到的地方是怎么做的?

收集了行覆盖率、条件覆盖率、状态机覆盖率、分支覆盖率、翻转覆盖率

覆盖率必须收满,收不满的情况:

- 比如case语句中,把所有情况都覆盖了,那最后的default就执行不到,这种情况行覆盖率、条件覆盖率和状态机覆盖率都可能达不到100%,需要exclude掉

- 再比如在寄存器中,一个32bit的寄存器,有很多保留位,那保留位复位值为0,只读寄存器不能写入,因此这部分无法进行翻转,这种情况下toggle一定达不到100%,需要exclude掉

- 再比如一些逻辑冲突或者设计冗余的语句,正常需要大量的定向case打边界条件、非法条件,但是有些分支是逻辑冲突,再怎么写非法case也覆盖不了,比如a成立的话b才可能成立然后a & b,那就不可能收集到a为假、b为真这条分支。这种情况直接在验证报告中与designer共同说明

比较难收的toggle覆盖率正常只收集模块接口的toggle、内部一般不收。代码覆盖率在exclude前一般得97%+,最低95%。

行覆盖率:检测每句话是否被执行到了。

翻转覆盖率:检测寄存器,线网等是否有0-1,1-0的跳变。

条件覆盖率:统计未覆盖的条件。

状态机覆盖率:检测状态机的状态是否都被覆盖到。

分支覆盖率:多重条件的每一条Path。

5、介绍一下AHB Matrix项目

6、描述一下AHB的信号

系统信号有HCLK、HRESET

地址总线信号有HADDR

数据总线信号有HWDATA、HRDATA

命令总线信号有HWRITE、HSIZE、HBURST、HSEL、HTRANS、HREADY、HRESP、HPROT

仲裁总线信号有HBUSREQ、HLOCK、HGRANT、HMASTER、HMASTER LOCK、HSPLIT

Master发出的信号:

HCLK:Clock

HRESETn:低电平复位信号

HADDR:Address

HTRANS[1:0]:Master用来指示当前传输的数据状态,包括四种:IDLE,BUSY,NONSEQ,SEQ

HWRITE:是否为写数据 1:写 0:读

HSIZE[2:0]:选择Bus的宽度 0:8bit 1:16bit 2:32bit大部分时间是不变的,等于2。

HBURST[2:0]:burst传输,表示一串信号的传输,当slave设备知道这是一连串的数据的时候就比较好准备,减少没ready的情况。

HPROT:protect,这个不怎么用

HWDATA[31:0]:写入的数据总线Decoder发出的信号:

HSELx:Decoder在接收到地址以后,判断这个地址属于哪一个slave,然后把这个slave的选中信号HSELx拉高。Slave发出的信号:

HRDATA[31:0]:读出来的数据总线。

HREADY:Master发送了一个信号,要知道Slave能不能接受,这个信号很重要,Master要知道数据是不是写进去了。

比如发送一个ADDR,检查HREADY是否为高,高了之后再发下一拍的动作:下一个地址以及上一拍的数据。

如果HREADY没有被拉高,那么信号维持一拍再检查READY。

HRESP[1:0]:Response信号。Slave设备指示Master动作的唯一方式。有四种情况:OK、ERROR、SPLIT和RETRY。

正常收到了就返回一个OK,出错了就报一个Error,或者没法响应了,就发Retry或者Split。让Master过段时间再来。

7、写操作和读操作是如何进行的,如何确保读写完成

先进行SINGLE的写操作,首先等待总线授权,即先拉高HBUSREQx总线请求,然后等待HGRANTx授权信号和HREADY信号表明从机已经响应,接着将htrans设为NONSEQ,地址、突发类型、传输大小分别进行非阻塞赋值为transaction中的对应值,而hwrite信号置1,表明当前为写操作,SINGLE操作时空一拍,然后将tr的data给到cb的hwdata,先驱动数据!同时整个操作阶段一直检查下降沿时hready信号是否拉高,如果拉高则跳出进行读操作,如果hready一直为低电平就代表从机未响应,那么主机占线就一直等待。

然后执行SINGLE的读操作,一样的htrans设为NONSEQ,地址、突发类型、传输大小一样赋值,hwrite信号置0,表明当前为读操作,SINGLE操作空一拍,先驱动数据!然后检查hready,如果OKAY那么执行,读回接口上的rdata。

海思

一面:55min

1、学校课程,学习成绩,对后端的了解,对课程熟悉程度。

2、STA:建立时间、保持时间,为什么需要建立时间保持时间?亚稳态会造成哪些影响,为什么要避免亚稳态?

3、对XOR熟悉吗?如何理解XOR?真值表

4、对仲裁了解过吗,有哪些形式的仲裁,具体场景是怎么样的?给一个场景避免饿死,用轮询仲裁,三个master对一个slave,并且master优先级完全一致,时序出现了错误,三个主机同时拉高了总线授权信号,这种bug作为验证要如何cover?

5、简单聊了下项目

6、跨时钟域问题

7、手撕,单bit跨时钟域快到慢

8、反问交流,非常友好

二面:1h

1、自我介绍+手撕,边沿检测

2、简历确认提问

3、实习项目

4、如何考虑华为和研究所

5、三种fork join的区别

6、跨时钟域的了解,怎么验证

7、对仲裁器的理解

8、反问交流,非常友好

主管面:55min

1、自我介绍

2、对着简历提问

3、实习项目重点提问、深挖

4、学习经历

5、遇到的挫折,怎么解决的

6、你的优点和短板是什么

7、在项目中遇到的困难有哪些,是怎么解决的

8、如何和团队成员沟通的,如果出现矛盾或者分歧如何解决

9、异步时钟在跨模块传输的时候怎么去验证,通过什么方式,项目中的跨时钟是快到慢还是慢到快

10、反问,最看重新人什么能力,需要提升哪些

自主学习、团队协作!验证要比设计更懂设计,高速接口协议,同步异步之类的基础

沐曦

基本深挖项目,面试官还是蛮有水平的,选一个项目深问,感觉沐曦比较倾向于AXI,面试官对AXI很感兴趣

有手撕,出了一道场景题:

多master多slave同时发数据,保证任意slave收到100个req的时候停止所有激励发送

我是用了个event,两段fork join_none并发,slave检测到100个trigger,另一端wait到了 disable fork。

后面面试官又问我未知数量master如何保证在fork join_none中可以发全,在fork外面套一层foreach,而不是在fork join_none里面多次调用`uvm_do_with的宏。

问家乡,学校

反问

时长共50min

1146

1146

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?