1 引入

本文讨论的锁相环仅考虑软件算法,不涉及硬件部分。

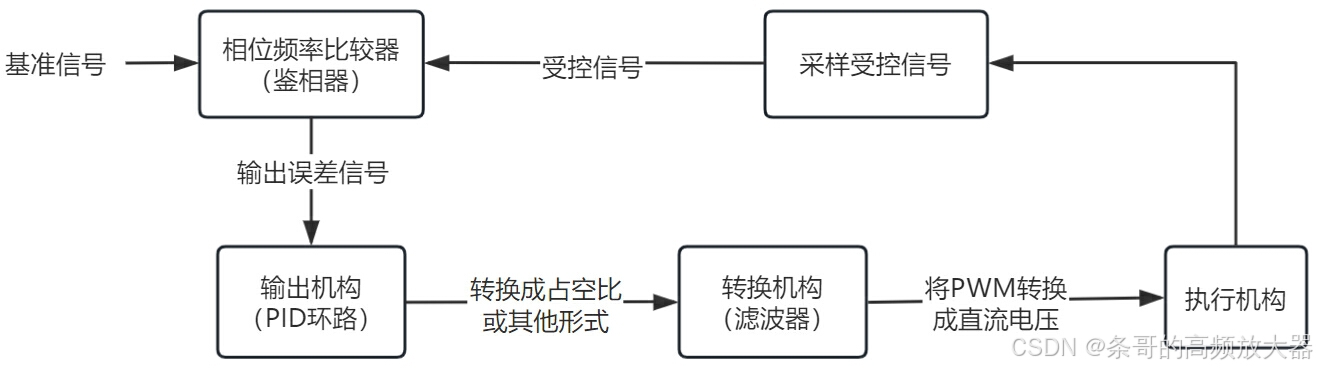

如下图,锁相环是对受控信号进行调控使其和基准信号同频同相,是一个经典的反馈控制算法。其中最重要的部分是鉴相器(相位频率比较器),鉴相器可以通过对比基准信号和受控信号的特征得到当前的误差,后续再由PID或简单滤波将误差转换成输出量对受控信号进行调整。

所以问题的关键便在于鉴相器如何得到误差。

2 鉴相器如何输出误差

2.1 原理

回到我们的目标,所谓锁相,包含了两层含义,表面是相位同步,其实还包括频率同步(还有一种叫锁频器,只同步频率)。但我们的调节手段只有调频(或者调速),即仅通过调节频率同时实现频率相位都同步,似乎不太可能。于是先来进行可行性的验证,观察一组简单的基准信号和受控信号表达式:

其中U1是基准信号,U2是受控信号,w1和w2分别是两个信号的角频率,即,

。

对受控信号不加以调控时,经过时间后,二者表达式变为:

二者的相位差也从变成

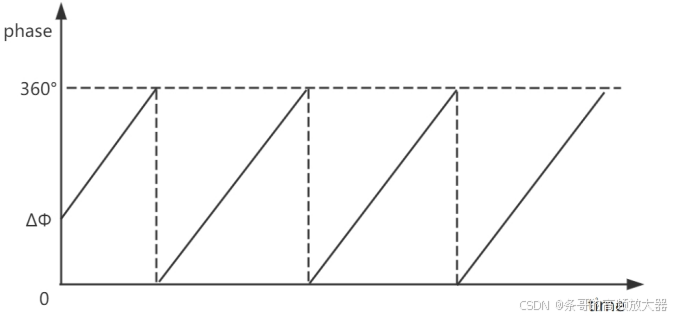

,即相位差是时时刻刻变化的,且由于

为定值,而相位(角度)范围为(0,360°),因此这个变化又是周期的。

由此可见,频率存在差异时,相位会不断的变化:当频率差大于0,相位会不断的超前;当频率差小于0,相位会不断的滞后。这两种情况下,都会存在相位刚好同步的时刻。于是当我们想:只需要小心翼翼地调整受控信号频率,同时关注信号的相位,使二者同相的瞬间频率刚好接近就行了(感觉又简单又很难)。

2.2 理想状态下的简单尝试

于是考虑一种最简单的方案,对受控信号的频率进行调节,使其最终和基准信号同频,即,并假设这个调频的动作是线性的,需要经过

时间才能完成,则最终的受控信号表达式变为:

二者的相位差变为。此时已经同频了,如果要保证此时同相,仅需满足

,其中

,

和

都已知,求解似乎变得理所当然!

关键问题来了,截止目前我们都是基于理想状态去实施方案。在这个过程中,最大的难点就是保证频率的线性调节,初始相位和频率也需要精确的测量,提高方案实施的精度,一旦这些环节出现偏差,就会出现频率同步了,但相位总是相差一点的情况,这时候再想如法炮制上述方案也没有用,因为频率此时已经同步了。

总结一下,该方案同时使用频率差和相位差作为误差源,并用一个确定的时间进行一次性地调节,理论实现非常简洁和迅速,但受制于现实环境难以应用。由以上表述,可以改进的方向有两个:

①原方案并未使用任何反馈回路信息,只用了先验信息去调控,我们可以把方案中一次性的调节过程给切碎,分成一小段一小段地调控,每一段都充分使用反馈信息做出新的调整。

②方案同时使用频率和相位进行误差计算,对两个输入量同时进行控制是更复杂的,需要解析二者的相关信息。但实际上频率同步后、相位不一定同步,而相位同步后、频率自然也是同步的,因此仅使用相位差也可以实现锁相功能。

2.3 将反馈引入

回顾最开始的一组信号:

初始时刻,二者的相位差为,假设此时

,则

在短时间内会不断地减小(超前),我们此时慢慢减小频率,但不确定需要调整到什么目标,由上面改进方向②可知,可以用相位差作为误差源去调频率,于是我们就用相位差作为阶段目标去调整,至于误差转换成输出的方式,可以直接使用PID调节。

但还有一个问题,即调整方向,上面默认了,所以误差便应是负数,如果某时刻

,则误差则变成了正数,理论上感觉没问题。但这里依然将频率差考虑在里面了,就会出现这种情况:频率接近,但相位处于反相。此时频率会在基准附近来回摆动,输出也会随之来回摆动,最终在反相的位置平衡。

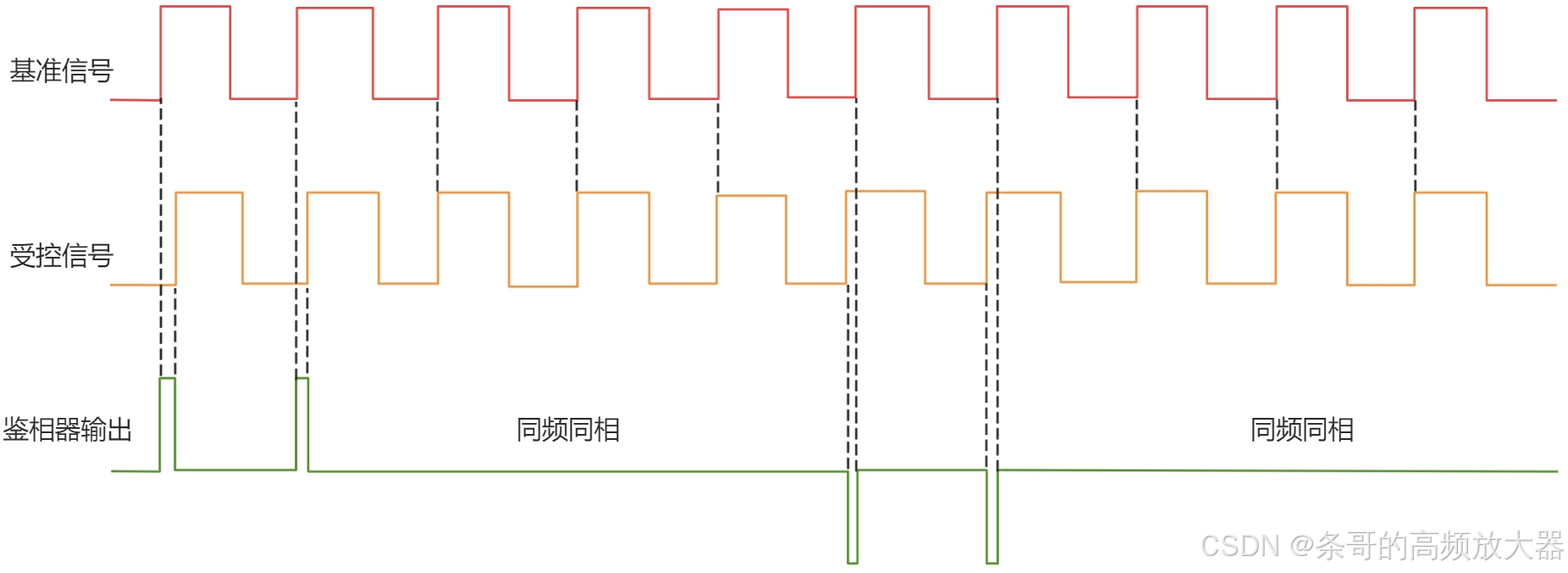

为了彻底舍弃频率误差且保持正确的调节方向,可以引入三态输出,如下图,其误差输出信号规则如下:

①当基准信号的上升沿来临时,输出Level+1(在之前的基础上+1);

②当受控信号的上升沿来临时,输出Level-1(在之前的基础上-1);

③其它时候保持当前Level;

④初始时刻的水平值由频率差决定,受控频率小于基准频率,则初始Level为0,否则为1;

于是得到下图经典的鉴相器输出:

于是可以根据每次鉴相器的输出Level*占空比得到当前误差,并将该误差输出到PID环路中,进行PID控制,最终将受控信号对齐基准信号。

822

822

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?