soc概述

soc即系统级芯片又称为片上系统(system on chip),即将系统的主要功能集成到一块芯片上。至少包含一个处理器核(微处理器/微控制器/数字信号处理器)。

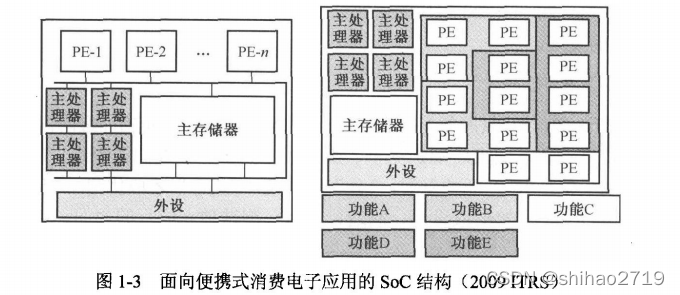

现在的soc上可整体实现CPU、DSP、数字电路、模拟电路、存储器、片上可编程逻辑电路等,综合实现图像处理、语音处理、通信协议、数据处理等功能。一个典型的面向消费电子的soc架构如下(pe指的是process engine):

soc按用途可分为

- 专用soc:是专用集成电路(ASIC)向系统级集成的自然发展

- 通用soc:将绝大部分部件、如CPU、DSP、RAM、I/O等集成在一块芯片上

IP(intelligent property)是组成soc的基本单元,所谓IP指的是由各种超级宏单元模块电路组成并经过验证的芯核,称为IP core

soc的优势

- soc可以实现更为复杂的系统

- soc具有更高的可靠性

- soc具有较低的设计成本

- 缩短产品设计时间

- 减少产品反复的次数

- 可以满足更小尺寸的设计要求

- 可达到低功耗设计的要求

soc的设计趋势以及挑战

1、soc的设计趋势

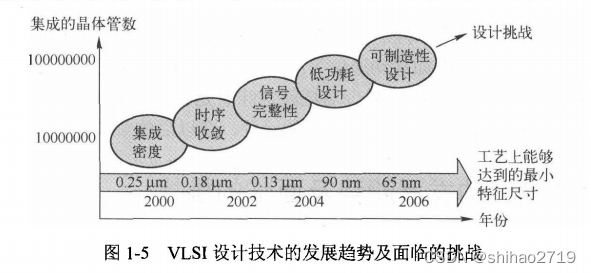

- 集成密度(复杂性)

主要来源于两个方面:

(1)硅器件的复杂性

①对于器件而言,无法确定各个理想参数的缩小比例(包括电源电压、阈值电压等)

②尺寸缩小使得寄生电容、电感的影响无法忽略,对于制造公益的可靠性造成一定的影响

(2)设计的复杂性

①芯片验证更为复杂:集成度越高,实现的功能越丰富,验证就越烦琐,验证的工作量几乎占了soc流程中的40%-70%

②芯片测试更为复杂:芯片规模的增大,往往会导致外围引脚的增加,并且内部逻辑电路会越来越复杂,会生成海量的测试向量

③混合电路设计更为复杂:数模混合的集成会变得尤其复杂 - 时序收敛

集成电路设计中的时序收敛一般指后端设计时序能够达到设计需求 - 信号完整性

信号完整性(signal integrity)是指一个信号在电路中产生正确的能力,一般认为是在需要的时间内,该信号有所必须达到的电压电平数值 - 低功耗设计

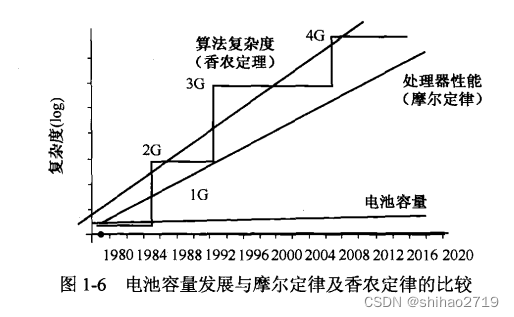

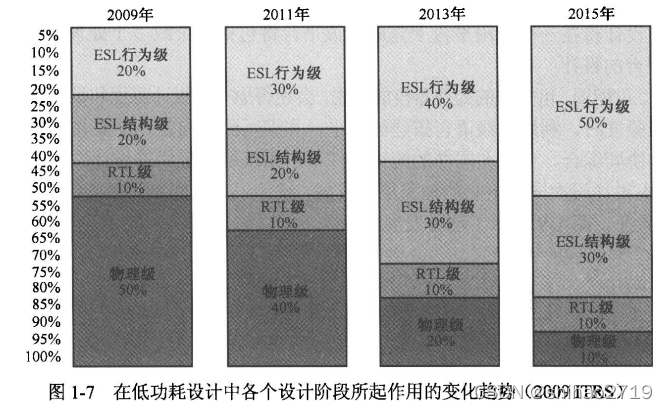

soc 的低功耗设计是当前芯片设计的重大挑战,在消费电子等领域,低功耗设计成为芯片设计的首要需求之一。

随着制造工艺尺寸的缩小,CMOS的静态功耗(漏电)急剧增长,带来了一系列的现实问题以及挑战:

(1)功耗增加引起的IC运行温度上升会引起半导体电路的运行参数漂移,会缩短芯片使用寿命

(2)为了进行低功耗设计,选择不同性能参数的器件,大大增加了设计的复杂度

从宏观结构上来看,IC功耗来源于IC内部的各功能模块以及各功能模块之间通信,功能越复杂、实现规模越大,功耗越高,所以系统级的设计从根本上关系到芯片功耗的大小。

从微观电路上来看,集成电路的功耗主要分为静态功耗和动态功耗,目前集成电路主要以CMOS器件为主,在这类电路中,动态功耗是主要的组成,但是随着工艺节点的推进,泄漏电流消耗的功率比重逐渐增大。 - 可制造性设计以及成品率

过去,芯片的成平率完全依赖于代工厂的工艺制造水平,现在越来越依赖于设计本身的特征。

2、soc设计方法与挑战

- 系统级设计

- 基于可配置处理器设计与使用的soc设计方法

soc设计流程

soc设计与传统的ASIC设计最大的不同在于:

(1)soc设计更需要了解整个系统的应用,提出合理的芯片架构

(2)soc设计是以IP复用为基础的

一个完整的soc设计包含:系统结构设计、软件结构设计硬件设计

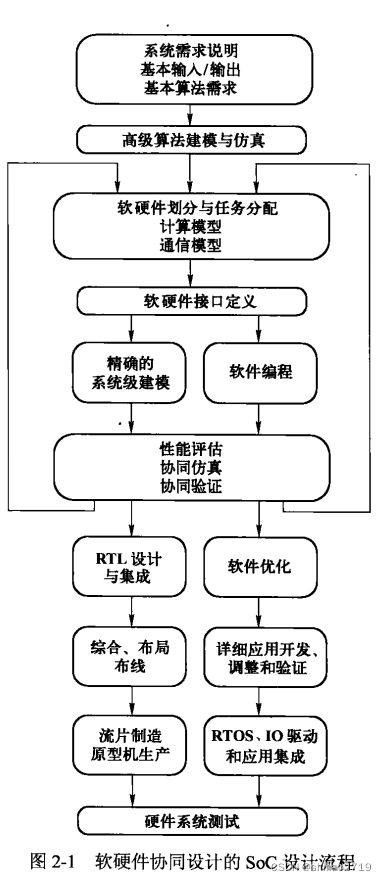

软硬件协同设计

soc作为一个完整的系统,包含了硬件和软件两部分,硬件指的是soc芯片部分,软件指的是运行在soc芯片上的系统以及应用程序。

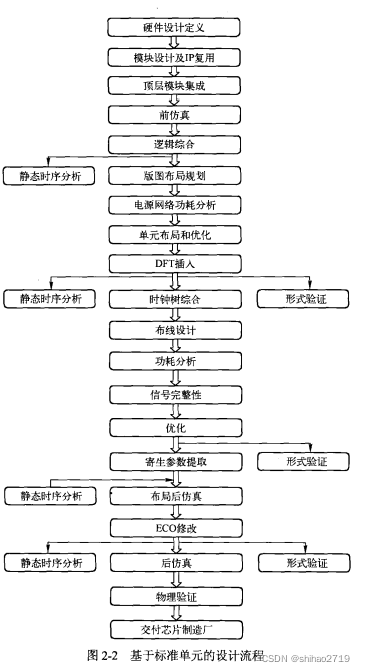

基于标准单元的SOC芯片设计流程

soc设计是从整个系统的角度出发,把处理机制、模型算法、芯片结构、各层次电路直至器件的设计紧密联合起来。

486

486

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?